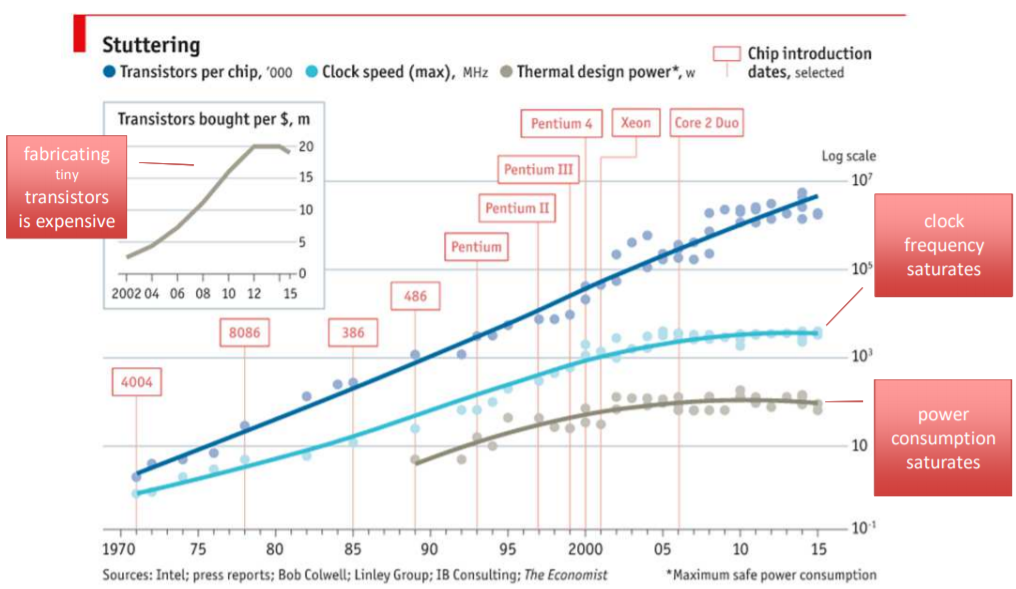

摩尔定律

- 集成电路上可以容纳的晶体管数目每18个月翻一倍

- 时钟频率区域饱和

- 功耗趋于饱和

MOSFET

阈值电压

V T = V T 0 + γ ( ∣ 2 ϕ F + V S B ∣ − ∣ ϕ F ∣ ) V_T = V_{T_0}+\gamma(\sqrt{|2\phi_{F}+V_{SB}|}-\sqrt{|\phi_{F}|}) VT=VT0+γ(∣2ϕF+VSB∣−∣ϕF∣)

- V T 0 : V S B = 0 时 的 经 验 值 V_{T_0}:V_{SB}=0时的经验值 VT0:VSB=0时的经验值

- γ : 体 效 应 系 数 , ≈ 0.4 V \gamma:体效应系数,\approx{0.4V} γ:体效应系数,≈0.4V

- ϕ F : 费 米 势 , 受 掺 杂 影 响 , ϕ F = ϕ T l o g ( N A n i ) \phi_{F}:费米势,受掺杂影响,\phi_{F}=\phi_{T}log(\frac {N_A} {n_i}) ϕF:费米势,受掺杂影响,ϕF=ϕTlog(niNA)

- V B ↑ , V S B ↓ , V T ↓ , 开 关 速 度 ↑ V_B\uarr,V_{SB}\darr,V_{T}\darr,开关速度\uarr VB↑,VSB↓,VT↓,开关速度↑

- V B ↓ , V S B ↑ , V T ↑ , 漏 电 流 ↓ , 静 态 功 耗 ↓ V_B\darr,V_{SB}\uarr,V_{T}\uarr,漏电流\darr,静态功耗\darr VB↓,VSB↑,VT↑,漏电流↓,静态功耗↓

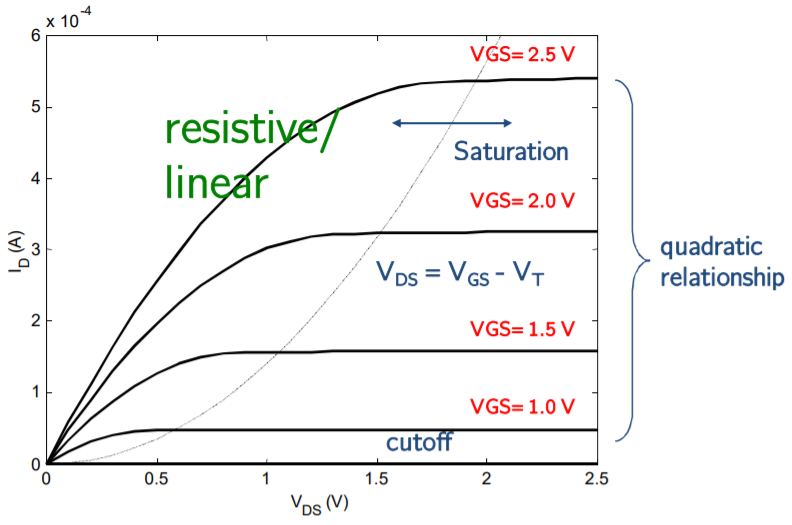

电流电压特性

可变电阻区(线性区)

I D S = μ n C o x W L [ ( V G S − V T ) V D S − V D S 2 2 ] I_{DS}=\mu_{n}C_{ox}\frac WL[(V_{GS}-V_T)V_{DS}-\frac {V_{DS}^2} 2 ] IDS=μnCoxLW[(VGS−VT)VDS−2VDS2]

- V D S < V G S − V T V_{DS}<V_{GS}-V_T VDS<VGS−VT

- L 较 大 , > 0.25 μ m L较大,>0.25\mu m L较大,>0.25μm

- 对 于 较 小 的 V D S , I D S 与 V D S 线 性 相 关 对于较小的V_{DS},I_{DS}与V_{DS}线性相关 对于较小的VDS,IDS与VDS线性相关

饱和区

I D S = 1 2 μ n C o x W L ( V G S − V T ) 2 I_{DS}=\frac 12\mu_{n}C_{ox}\frac WL(V_{GS}-V_T)^2 IDS=21μnCoxLW(VGS−VT)2

- V D S > V G S − V T V_{DS}>V_{GS}-V_T VDS>VGS−VT

- L 较 大 , > 0.25 μ m L较大,>0.25\mu m L较大,>0.25μm

- I D S 不 再 是 V D S 的 函 数 I_{DS}不再是V_{DS}的函数 IDS不再是VDS的函数

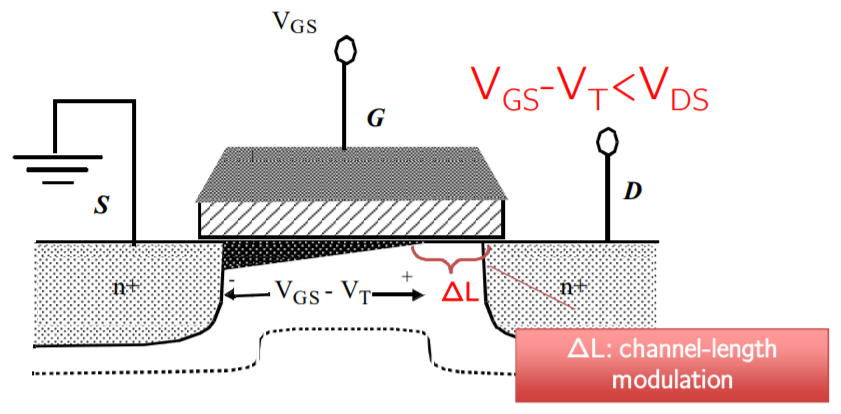

沟道长度调制

I D S = 1 2 μ n C o x W L ( V G S − V T ) 2 ( 1 + λ V D S ) I_{DS}=\frac 12\mu_{n}C_{ox}\frac WL(V_{GS}-V_T)^2(1+\lambda{V_{DS}}) IDS=21μnCoxLW(VGS−VT)2(1+λVDS)

- λ : 经 验 参 数 \lambda:经验参数 λ:经验参数

- 反 比 于 沟 道 长 度 L 反比于沟道长度L 反比于沟道长度L

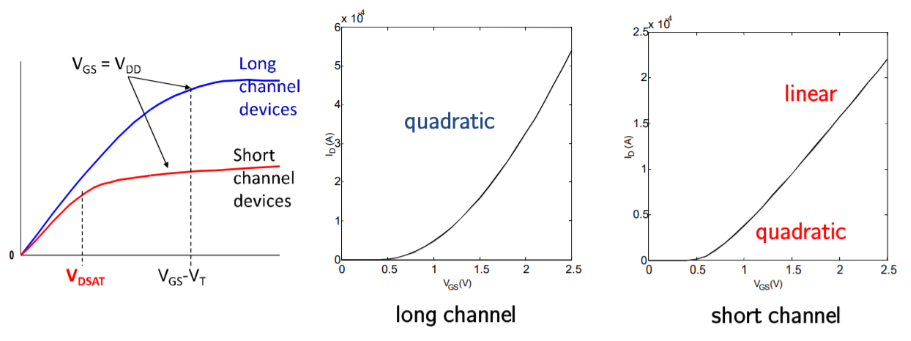

短沟道效应

- 短沟道器件载流子迁移速度提前达到饱和

- quadratic(二次)区域减小,linear(线性)区域增加

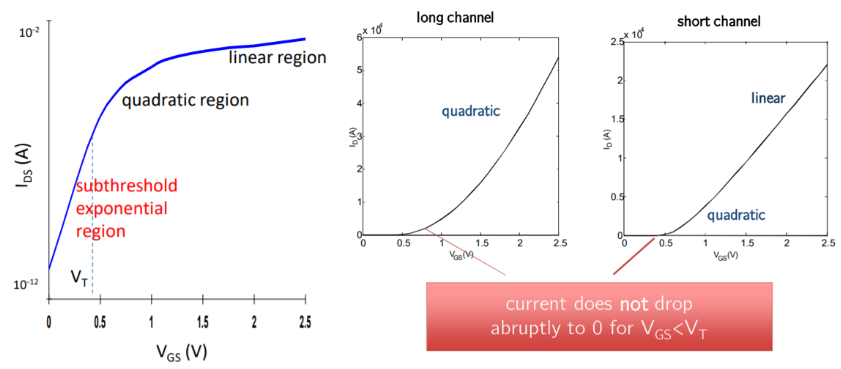

亚阈值

- V G S < V T V_{GS}<V_T VGS<VT时,FET关断时,沟道依旧有一定导电性

- 增加静态功耗

纳米晶体管

- 深亚微米器件: V T = f ( L , W , V D S ) V_T=f(L,W,V_{DS}) VT=f(L,W,VDS)

- L ↓ , V T ↓ L\darr,V_T\darr L↓,VT↓

- 漏极诱导势垒降低(drain-induced barrier lowering): V D ↑ , 漏 极 p n 结 耗 尽 区 ↑ , V T ↓ , V T = V T 0 − λ d V D S V_D\uarr,漏极pn结耗尽区\uarr,V_T\darr,V_T=V_{T_0}-\lambda_dV_{DS} VD↑,漏极pn结耗尽区↑,VT↓,VT=VT0−λdVDS

- 高电场下,电子会隧穿栅极氧化物,形成栅极漏电流,增加器件静态功耗 ( L < = 100 n m ) (L<=100nm) (L<=100nm)

- 相较 S i O 2 SiO_2 SiO2,高 K K K材料的电容大60%,栅极漏电流减小>100%

热载流子效应

- 阈值电压随时间漂移

- 电子或空穴隧穿到栅极氧化物( 1 V / μ m 1V/\mu m 1V/μm)

- n m o s nmos nmos的 V T V_T VT增加, p m o s pmos pmos的 V T V_T VT减小

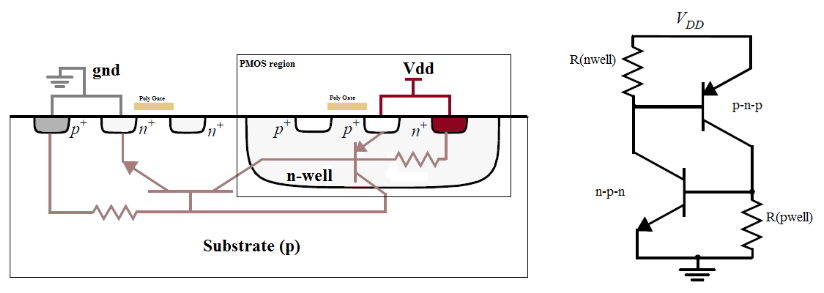

CMOS latch-up

- 一个BJT打开后,电流会打开另一个BJT,正向反馈,即使输入消失,输出也依旧持续

- 降低R(nwell)、R(pwell),使得V=IR低于阈值电压,不会打开BJT

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?