名称:数字频率计设计VHDL代码Quartus DE2-115开发板(文末获取)

软件:Quartus

语言:VHDL

代码功能:

课题简介

1.频率检测是电子测量领域最基本的测量之一,数字频率计是一种应用非常广泛的数字电路,本设计系统根据频率计的测频原理,选择合适的时基信号对被测信号脉冲进行计数,达到测频的目的。本课题要求借助EDA工具和设计方法

学习硬件描述语言,用编程的方法来设计电路,在 QUARTUSII软件环境中,进行电路的测试和仿真分析,最后下载到FPGA芯片完成硬件的功能测试。系统功能要求:具有记忆显示功能,测试结果采用6位十进制数字由七段数码管显示;测量范围100HZ-2OKHZ;响应时间15秒;显示时间21秒;测量误差≤0.1%。系统总体电路由频率控制模块、分频器数器、锁存器、数据选择器、译码器等模块组成。

2、课题能促进哪些人才培养目标的实现(能解决那些复杂工程问题)

课题支撐专业培养计划中毕业要求

指标点32:能够针对电力系统工程设计与产品开发的特定需求,完成元件和系统的设计,在设计中体现创新意识。

指标点3.3:在电力系统工程设计中能够考虑安全、健康、法律、文化及环境等制约因素。

指标点5.2:能够选择与使用恰当的仪器、信息资源、工程工具和专业模拟软件,对电力系统复题进行分析、计算与设计

指标点9.2:能够在团队中独立或合作开展工作。指标点9.3:能够组织、协调和指挥团队开展工作

指标点101:能就专业问题,以口头、文稿、图表等方式,准确表达自己的观点,回应质疑,理解与业界同行和社会公众交流的差异性

指标点11.3:能在多学科环境下(包括模拟环境),在设计开发解决方案的过程中,运用工程管理与经济决策方法

指标点12.2:具有自主学习的能力,包括对技术问题的理解能力,归纳总结的能力和提出问题的能力等。

本代码已在DE2-115开发板验证,DE2-115开发板如下,其他开发板可以修改管脚适配:

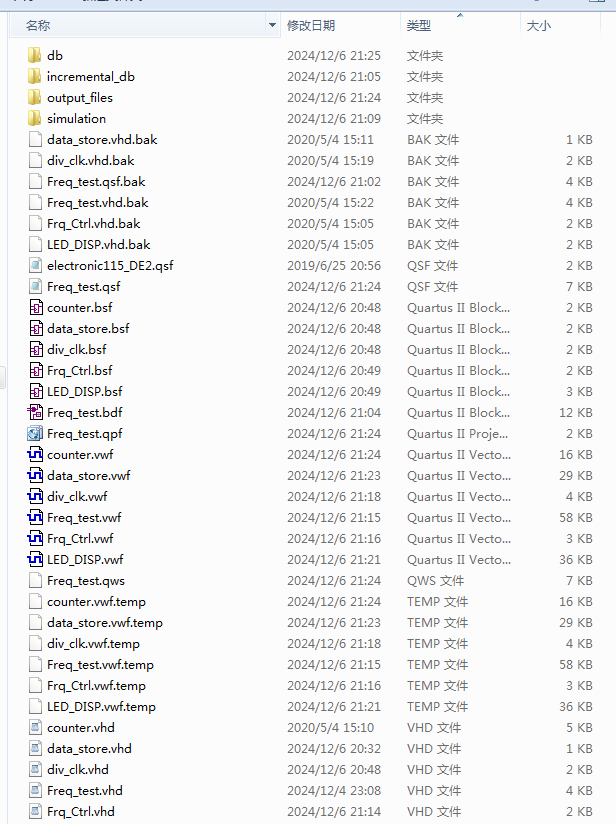

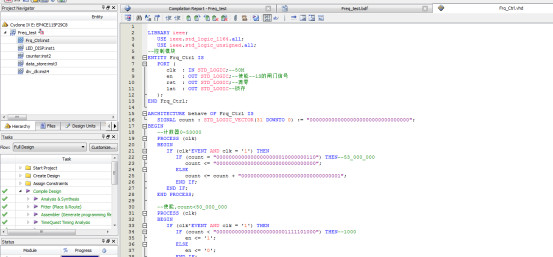

1. 工程文件

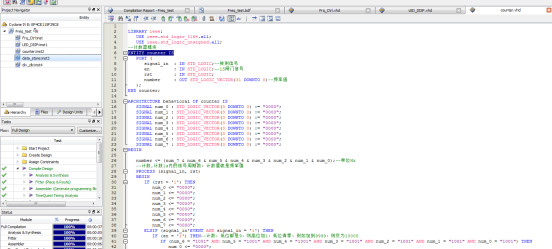

2. 程序文件

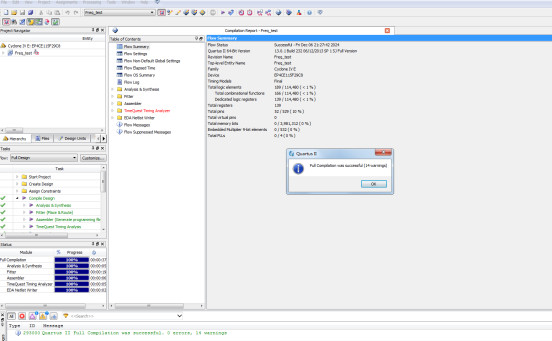

3. 程序编译

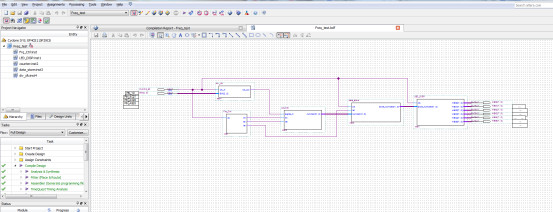

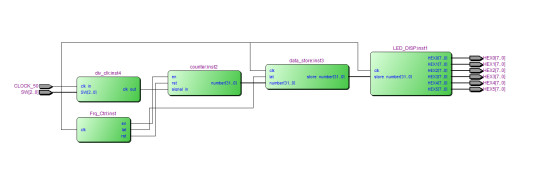

4. RTL图

5. 管脚图

6. 仿真图

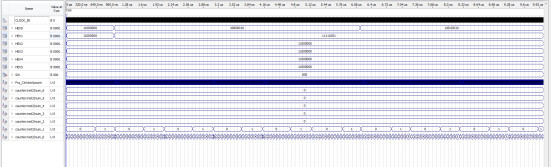

顶层仿真

图中SW为自测频率选择开关,Num6~0为测的频率值,通过数码管HEX5~HEX0显示

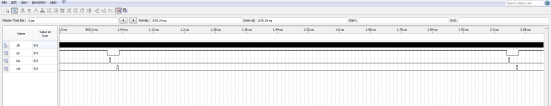

分频模块

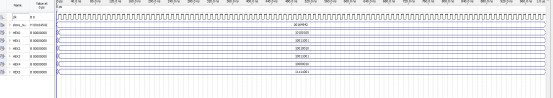

图中SW为自测频率选择开关,通过3个拨码可以控制输出8中不同的自测频率,图中显示了拨码为000~011的输出频率。

控制模块

控制模块用于产生1s闸门信号en,锁存信号lat,清零信号rst

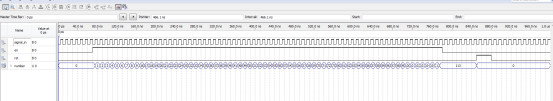

计数器模块

计数器用于在1s闸门信号en为高电平时计数,计数值即为信号的频率

锁存器模块

锁存器用于将计数器模块计数的频率值锁存起来,用于后级显示模块显示

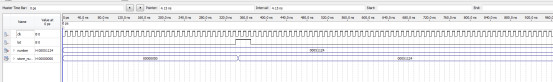

显示模块

本模块用于显示频率值,本图中,频率值为164542Hz,其中HEX5为最高位,HEX0为最低位。

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --计数器模块 ENTITY counter IS PORT ( signal_in : IN STD_LOGIC;--被测信号 en : IN STD_LOGIC;--1S闸门信号 rst : IN STD_LOGIC; number : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)--频率值 ); END counter; ARCHITECTURE behavioral OF counter IS SIGNAL num_0 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL num_1 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL num_2 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL num_3 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL num_4 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL num_5 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL num_6 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; SIGNAL num_7 : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; BEGIN number <= (num_7 & num_6 & num_5 & num_4 & num_3 & num_2 & num_1 & num_0);--单位Hz --计数,计数1s内的信号周期数,计数值就是频率值 PROCESS (signal_in, rst) BEGIN IF (rst = '1') THEN num_0 <= "0000"; num_1 <= "0000"; num_2 <= "0000"; num_3 <= "0000"; num_4 <= "0000"; num_5 <= "0000"; num_6 <= "0000"; num_7 <= "0000"; ELSIF (signal_in'EVENT AND signal_in = '1') THEN IF (en = '1') THEN--计数,低位都是9,则高位加1,低位清零,例如加到9999,则变为10000 IF (num_6 = "1001" AND num_5 = "1001" AND num_4 = "1001" AND num_3 = "1001" AND num_2 = "1001" AND num_1 = "1001" AND num_0 = "1001") THEN num_0 <= "0000"; num_1 <= "0000"; num_2 <= "0000"; num_3 <= "0000"; num_4 <= "0000"; num_5 <= "0000"; num_6 <= "0000"; num_7 <= num_7 + "0001";--低位为9,则高位加1,低位清零 ELSIF (num_5 = "1001" AND num_4 = "1001" AND num_3 = "1001" AND num_2 = "1001" AND num_1 = "1001" AND num_0 = "1001") THEN num_0 <= "0000"; num_1 <= "0000"; num_2 <= "0000"; num_3 <= "0000"; num_4 <= "0000"; num_5 <= "0000"; num_6 <= num_6 + "0001";--低位为9,则高位加1,低位清零 num_7 <= num_7; ELSIF (num_4 = "1001" AND num_3 = "1001" AND num_2 = "1001" AND num_1 = "1001" AND num_0 = "1001") THEN num_0 <= "0000"; num_1 <= "0000"; num_2 <= "0000"; num_3 <= "0000"; num_4 <= "0000"; num_5 <= num_5 + "0001";--低位为9,则高位加1,低位清零 num_6 <= num_6; num_7 <= num_7; ELSIF (num_3 = "1001" AND num_2 = "1001" AND num_1 = "1001" AND num_0 = "1001") THEN num_0 <= "0000"; num_1 <= "0000"; num_2 <= "0000"; num_3 <= "0000"; num_4 <= num_4 + "0001";--低位为9,则高位加1,低位清零 num_5 <= num_5; num_6 <= num_6; num_7 <= num_7; ELSIF (num_2 = "1001" AND num_1 = "1001" AND num_0 = "1001") THEN num_0 <= "0000"; num_1 <= "0000"; num_2 <= "0000"; num_3 <= num_3 + "0001";--低位为9,则高位加1,低位清零 num_4 <= num_4; num_5 <= num_5; num_6 <= num_6; num_7 <= num_7; ELSIF (num_1 = "1001" AND num_0 = "1001") THEN num_0 <= "0000"; num_1 <= "0000"; num_2 <= num_2 + "0001";--低位为9,则高位加1,低位清零 num_3 <= num_3; num_4 <= num_4; num_5 <= num_5; num_6 <= num_6; num_7 <= num_7; ELSIF (num_0 = "1001") THEN

源代码

点击下方的公众号卡片获取

1358

1358

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?