csdn的编辑器不好用,有很多格式显示不出来,我又是一个懒人不想去迁移,所以这篇文章可能看起来比较怪,如果想要看原文的同学可以参考以下链接

在上一章我们说到verilog的结构,分为模块说明和功能模块两部分,本文我们将讨论的assign语句就属于功能模块部分。

assign语句的格式及特点

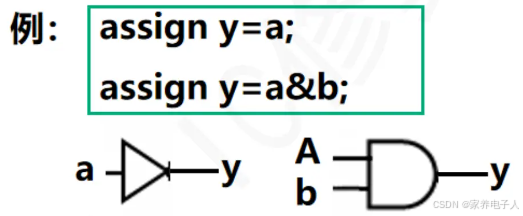

assign语句被称为连续赋值语句,我们首先来看看assign语句的格式:

assign 赋值目标 = 表达式 ;

顾名思义,该语句的作用就是将表达式计算的值赋给赋值目标。

该语句有两个特点:

第一,之所以被称为连续性赋值,是因为只要表达式的值变化,赋值目标的值就会开始被重新赋值,与之相对的是过程赋值语句。

第二,该语句的赋值目标必须是wire型的的数据类型,这样才表示立即变化,因为wire型就像电线一样直接链接。

上面的y在进行端口信号声明的时候必须是wire型。

1522

1522

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?