目录

1.1 关于AHB协议

AHB(Advanced High-performance Bus,高级高性能总线)是一种适用于高性能可综合设计(high-performance synthesizable)的总线接口,是AMBA总线架构的一部分。

它定义了组件之间的接口(interface),例如:

- 主设备(Manager):发起数据传输的组件,如CPU、DMA。

- 从属设备(Subordinates):响应管理器请求的设备,如内存、高速外设。

- 互联模块(interconnect):连接管理器和从属设备,并进行地址译码和数据路由。

AHB实现了高性能、高时钟频率系统所需的功能,包括:

- 突发传输(Burst transfers):一次可以传输多个数据,提高性能。

- 单时钟边沿操作(Single clock-edge operation):数据在时钟的单一边沿传输,更适合综合实现。

- 非三态实现(Non-tristate implementation):使用多路选择器(MUX)代替三态总线,更适合综合实现。

- 可配置的数据总线宽度(Configurable data bus width):可根据需求调整。

- 可配置的地址总线宽度(Configurable address bus width):可根据系统规模调整。

最常见的AHB从属设备包括:

- 内部存储设备(internal memory device)

- 外部存储接口(external memory interface)

- 高带宽外设(high-bandwidth peripherals)。

尽管低带宽外设也可以作为AHB从属设备,但出于系统性能考虑,他们通常位于AMBA高级外设总线(APB)上。AHB和APB之间的桥接是通过一个被称为APB桥(APB bridge)的AHB从属设备实现的。

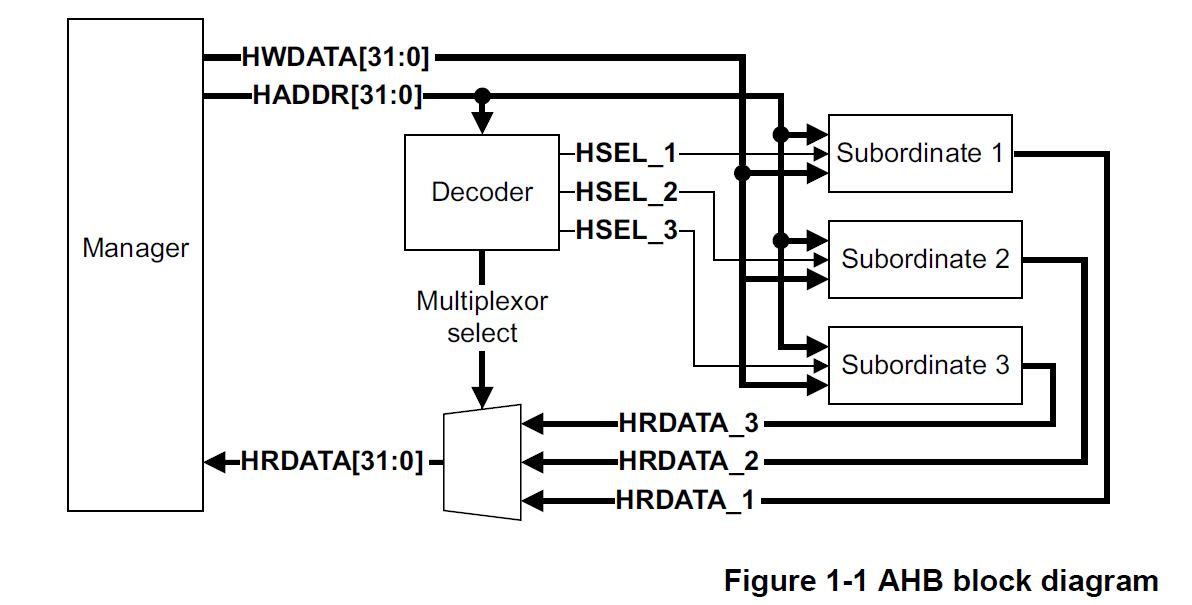

图1-1展示了一个单主设备AHB系统设计,其中包含1个AHB主设备和3个AHB从设备。总线互连逻辑由一个地址译码器(Decoder)和一个多路复用器(MUX)组成。Decoder在地址阶段(address phase)监测来自主设备的地址,以便在数据阶段(data phase)选择适当的从设备。MUX将从设备输出数据路由回主设备。【图中仅展示了主要的地址和数据总线,以及典型的数据路由。并非所有信号都已展示。】

AHB还支持多主设备设计,通过使用一个提供仲裁和路由信号的互连组件,将不同主设备的信号路由到正确的从设备。

-------------------------------------------------------------------------------------------------------------------------------

补充:非三态实现

--------------------------------------------------------------------------------------------------------------------------------

1.1.1 主设备(Manager)

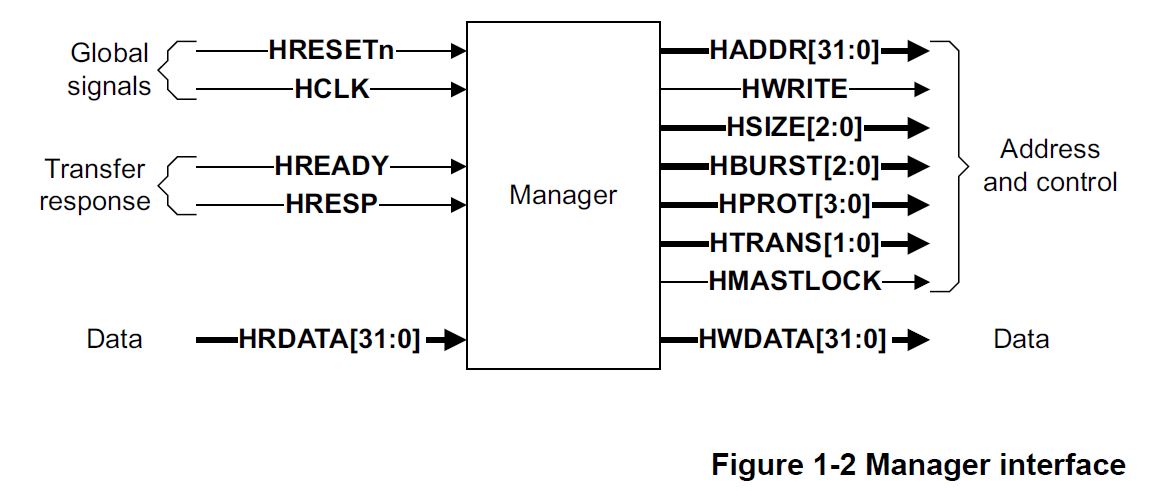

Manager是发起读/写操作的核心组件,负责提供地址和控制信息来驱动数据传输。

图1-2展示了一个AHB主设备接口(未涵盖AHB5中新增的信号)。

1.1.2 从设备(Subordinate)

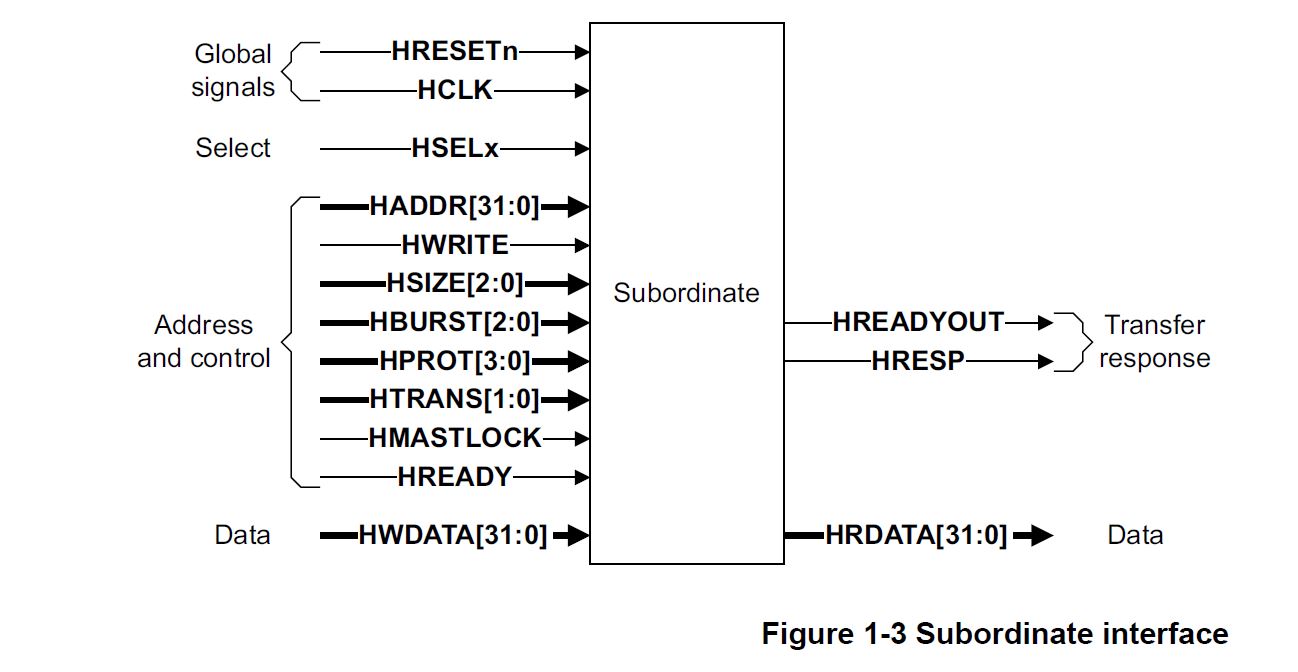

从设备响应系统中Manager发起的传输。从设备通过来自Decoder的HSELx(选择信号)来判断何时对总线传输进行响应。

从设备向Manager反馈以下信息:

- 总线传输的完成或延长。

- 总线传输的成功或失败。

图1-3展示了一个从设备的接口。

1.1.3 互联逻辑(Interconnect)

互联组件(interconnect component)在系统中为Manager和Subordinate之间提供连接。

- 在单Manager系统中,只需要使用Decoder和MUX。

- 在多Manager系统中,需要使用一个互联模块(interconnect),用于执行仲裁,并将来自不同Manager的信号路由到对应的从设备。这种信号路由包括地址、控制信号、写数据信号的传输。

关于多Manager系统中使用的不同互连结构,如单层和多层互联(single layer or multi-layer interconnects),未在本SPEC中做详细说明。如需了解多层AHB的具体实现,请参考Multi-layer AHB Technical Overview (ARM DVI 0045)。

地址译码器(Decoder)

- 该组件对每次传输的地址进行译码,并为参与传输的从设备提供选择信号(select signal)。

- 该组件还为MUX提供控制信号。

- 在所有包含≥2个从设备的系统中,都必须包含一个集中式(centralized)Decoder。

多路复用器(Multiplexor)

- 将读数据和响应信号(response signal)由Subordinate发送至Manager。

- 在所有包含≥2个从设备的系统中,都必须包含一个集中式(centralized)MUX。

1.2 AHB版本说明(revisions)

Issue A描述了AHB-Lite接口。

Issue B引入了AHB5,它在AHB-Lite的基础上增加了一些新功能。

本SPEC为Issue C,新增了以下内容:

(略)

在本SPEC中,术语AHB用于同时表示AHB-Lite和AHB5。

除非特别说明,所有信号适用于AHB-Lite和AHB5。

1.3 操作(Operation)

Manager通过驱动地址和控制信号来启动一次传输。这些信号包含以下信息:

- 地址

- 传输方向(读/写)

- 数据宽度

- 是否为突发传输的一部分

传输类型包括:

- 单次传输(Single)

- 递增突发传输(Incrementing bursts):地址连续递增,但不会在地址边界回绕

- 回绕突发传输(Wrapping burats):在特定地址边界进行地址回绕

数据总线方向:

- 写:Manager → Subordinate

- 读:Subordinate → Manager

每次传输包含两个阶段:

- 地址阶段(Address phase):一个周期,用于发送地址和控制信号

- 数据阶段(Data phase):一个或多个周期,用于传输数据

关于阶段控制:

- 地址阶段:从设备不能请求延长。因此在该阶段,所有从设备必须能够进行地址采样。

- 数据阶段:从设备可以通过HREADY信号请求延长。当HREADY为低时,会插入等待周期(wait state),使从设备有更多时间提供或采样数据。

传输结果反馈:

从设备使用HRESP信号来指示传输的成功或失败。

2531

2531

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?