AHB学习总结

总线概述

作者:阿锋聊数字

AMBA的AHB总线是一个高性能总线,它可以包括masters, interconnects 和 slaves 。

它主要支持:

- 突发传输

- 单时钟边沿操作

- 非三态的

- 数据位宽可配置,64, 128, 256, 512, 和 1024 bits

多数的AHB Slave设备包括,memory设备、外部memory接口和高性能外设。如果你想连接低速设备,可以考虑使用低速总线,例如APB总线。

AHB总线还支持多Master的设计,你可以使用interconnect组件连接多个主,interconnect组件提供了仲裁器和路由机制。

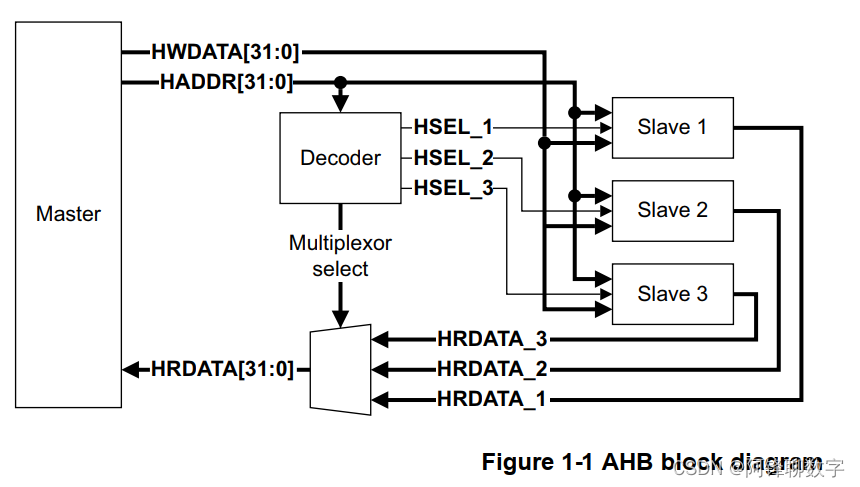

下图举例了一个一主三从的互联结构,图中未展示所有信号。

Master

Slave

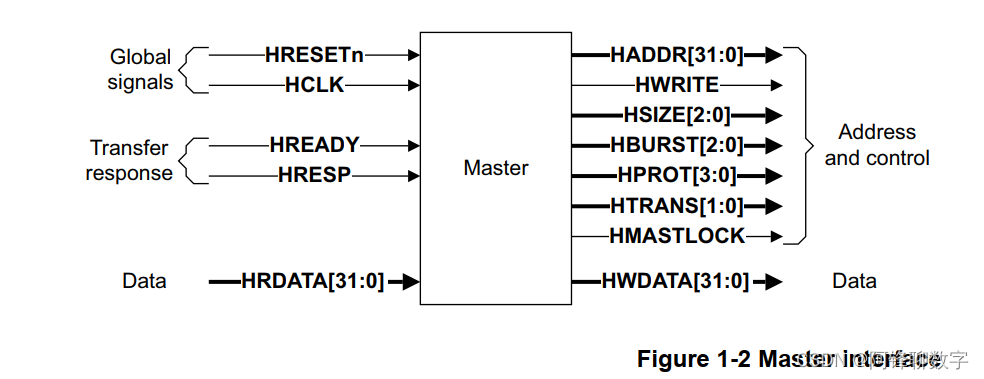

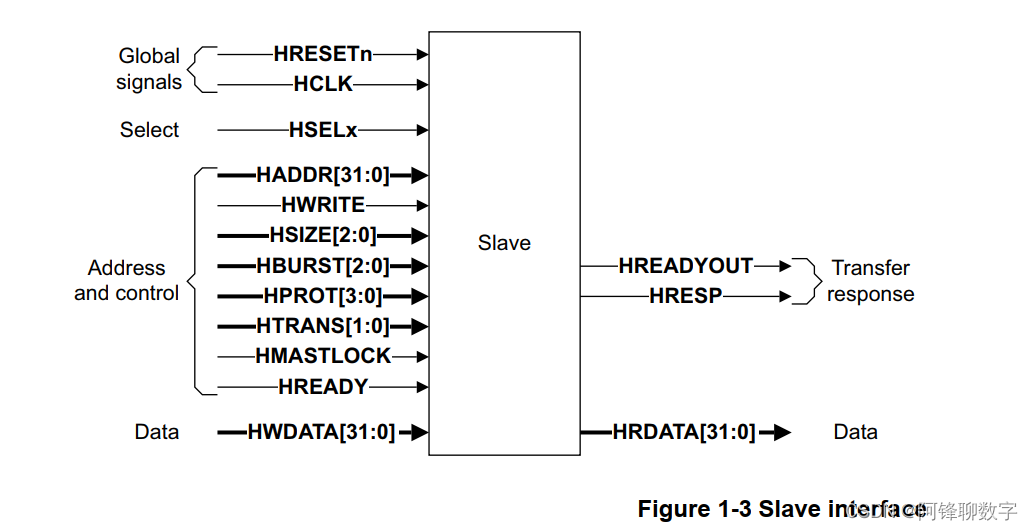

信号描述

传输

基本传输

带读写等待的传输,下图中master 发起的

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8万+

8万+