本篇文章主要介绍verilog里面常用的语句, 包括条件语句、循环语句块语句和生成语句。出了块语句和生成语句,其他的基本和c语言或者m语言一致。

1,if 语句,在需要判断逻辑的时候可以使用if语句,如 从输入a,b中找出最大值。

if (a>b)

max=a;

else

max=b;

这里使用方法和c语言一致。需要注意的一点是在有判断的时候,verilog 希望支路都有默认值。

比如

if (a>b)

c=2;

这里是不建议的写法,建议的写法为

if (a>b)

c=2;

else

c=1;

或者

c=1;

if (a>b)

c=2;

这两个建议的写法都保证了c有一个默认值,这样可以避免在无默认值的时候,实际电路中会出现一个锁存器

2.case 语句, 对于需要多分支选择的条件,可以使用case语句,避免使用大量的if else。

case(a)

2'd0: b=0;

2'd1: b=1;

2'd2: b=2;

default: b=1;

endcase;// 表明case语句的结尾

case(2)

A1: b=0;

A2: b=1;

A3: b=2;

default: b=1;

endcase;// 表明case语句的结尾

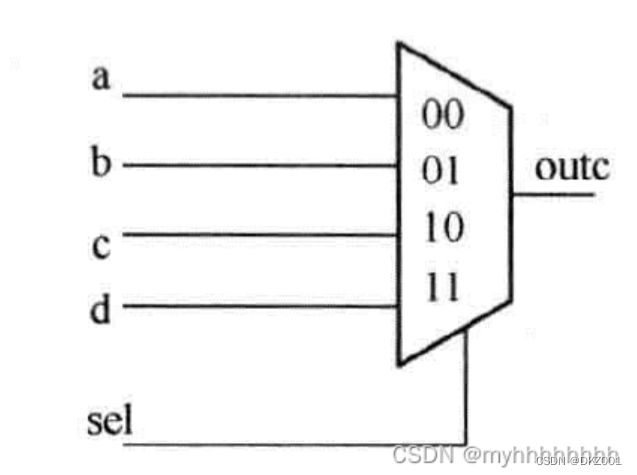

verilog中case 语句不用break。综合后的电路如下:

另外一个和c不同的是

case (1'b1)

sel[0]: b=0

sel[1]:begin .....end

default: b=1;

endcase

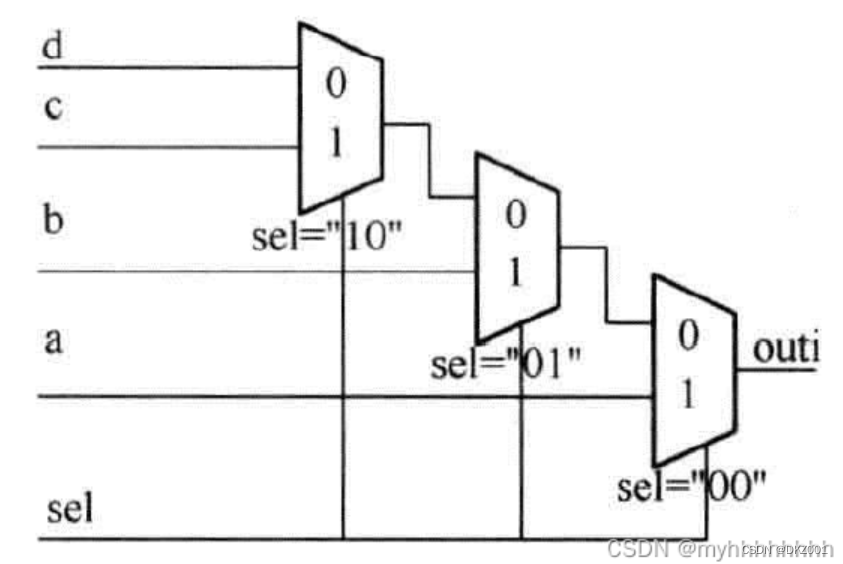

这里case后面跟得是一个常数,下面的选择则为变量,具体含义为sel[n]为1的时候则执行对应的回路,综合后的电路如下

3.循环语句包含for和while, 两者和c语言基本一样。

for(i=1;i<10;i=i+1) a=a+1;

while(a) c=c+1;

此外verilog 还有repeat语句 可以直接定义执行几次;

repeat(8) a=a+1; //该语句执行8次

2. 块语句,有顺序块和并行块。

verilog 语句之间一般是并行关系,但是对于顺序块语句中的程序会顺序执行。

如

initial

#0

a=10;

#10// 本处延迟10个clock

a=20;

#30// 本处延迟30个clock

a=30;

这里a 发生变化 10 20 30

并行块关键词为fork -join

fork

#0

a=10;

#10// 本处相对起始时间延迟10个clock

a=20;

#30// 本处相对起始时间延迟30个clock

a=30;

join

敏感词检测

always @ (敏感词)

begin

检测到敏感词时候的执行工作

end

如:

always(posedge clk) // 当时钟上升沿的时候才触发这里

begin

if (a>10)

b<=20; // 在时序模块中推荐使用非阻塞赋值

end

对于一个关键词后面跟的程序大于一行时,c语言是用{}来进行区分,verilog 则是用begin end 来进行区分,如

if (a>b)

begin

c=2;

d=c*8

end

else

begin

c=5;

d=c*2

end

928

928

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?