采用单相时钟锁存技术的抗噪声互补金属氧化物半导体电路设计

摘要

本文提出了一种基于单相时钟锁存的抗噪声(TSPCL‐NT)动态CMOS电路设计。TSPCL‐NT动态电路能够在噪声进入动态电路之前对其进行隔离和滤除,因此不仅能显著提高动态电路的抗噪能力,还能有效缓解反馈保持器与下拉网络之间的信号争用问题。从而在功耗和工作速度牺牲较小的情况下提升动态电路的抗噪性能。在台积电90纳米CMOS工艺下,16位TSPCL‐NT曼彻斯特加法器的平均噪声阈值能量可提高3.41倍,同时功耗延迟积相较于最先进的16位XOR‐NT曼彻斯特加法器设计提升了5.92%。版权所有© 2014 约翰威立父子有限公司

2013年5月1日收到;2013年9月30日修订;2013年12月6日接受

关键词 :抗噪声;动态电路;单相时钟电路;互补金属氧化物半导体

1. 引言

动态CMOS电路由于其高速特性,是高性能应用中首选的逻辑电路家族之一[1–4]。与静态CMOS电路相比,使用动态CMOS电路实现相同的逻辑功能可节省近一半的晶体管数量、芯片面积和硬件成本。然而,由于在评估阶段浮空节点较为脆弱,动态电路本身容易受到噪声干扰[1–17]。当静态CMOS电路中发生噪声干扰时,仅会导致毛刺,电路仍能保持正确逻辑功能。相比之下,动态CMOS电路中的漏电电荷无法恢复,噪声干扰最终将导致错误逻辑功能。因此,如何防止在动态电路的评估阶段因噪声干扰而导致电荷泄漏,成为一个关键问题[18–22],[31–35]。

在动态电路中,文献[8],[10–14],[23–35]已提出了多种抗噪技术。现有的抗噪声动态电路设计可分为两类:其中一类是防止动态节点悬空,如图1(a)所示。将稳定电压源连接到悬空节点可解决悬空问题并增强噪声免疫能力。这是一种防止动态节点悬空的简单方法。然而,通常为了实现优异的噪声免疫能力,必须在速度、功耗和面积方面付出较高的设计代价,因为它存在反馈保持器与下拉网络之间的信号争用问题。

下拉网络(PDN)。另一种抗噪声方法是提高PDN晶体管的源极电压。提高源极电压可以增加触发PDN中电荷泄漏的阈值,如图1(b)所示[12–19],[21],[28–33]。一般来说,提高PDN的源极电压能更有效地增强动态电路的抗噪能力。然而,这种抗噪技术需要付出更高的设计代价,因为PDN中的每个晶体管都需要添加额外晶体管。

为了降低下拉网络中的硬件开销并避免信号争用问题,我们提出了一种用于动态CMOS电路的新型抗噪声技术。与防止动态节点悬空或防止下拉晶体管导通不同,我们的新抗噪方法是利用单相时钟锁存(TSPCL)机制,在噪声到达动态电路之前将其隔离并泄放掉。通过这种方式,我们可以在较小的性能损失下增强动态电路的抗噪能力。由于噪声源已被隔离,因此无需付出较大的硬件成本或设计代价来提升抗噪能力。因此,在所提出的设计中,动态电路的功耗、工作速度和抗噪能力均可得到改善,且具有更低的开销,同时抗噪能力也更为优越。

2. 动态CMOS电路中抗噪技术的综述

动态CMOS电路中的主要设计问题是评估阶段的浮动问题。由于存在输出浮动节点,其噪声容限仅为一个nMOS晶体管的阈值电压。提高动态电路抗噪能力主要有两种设计方向:一种是防止动态节点悬空[8],[22–27],[34],[35],另一种方法是提高下拉晶体管的源极电压,以防止受噪声影响的晶体管导通[12–20],[28–33]。提高下拉网络(PDN)的源极电压能更有效地增强抗噪能力,但必须付出更高的设计开销。防止动态节点悬空的方法较为简单,但通常仍需付出较高的设计开销。

在速度、功耗和面积方面存在设计代价,以实现抗噪能力的提升,因为这些方法受到保持器与下拉网络之间争用问题的影响。

双晶体管设计[21]和隔离式抗噪设计(INT设计)[31]是通过提升下拉晶体管的源极电压来增强动态CMOS电路抗噪能力的两种最具代表性的设计。双晶体管技术为每个下拉晶体管引入一个额外晶体管,以依赖噪声的方式[21]抬升其源极电压。INT技术进一步增加了一种噪声隔离机制,以保护其抗噪机制免受噪声干扰[31]。至于基于XOR的条件保持器设计[34],,它不仅是通过防止动态节点悬空来提高动态CMOS电路抗噪能力的最具代表性设计,而且是最先进的设计。基于XOR的条件保持器设计能够提供几乎与INT设计相当的抗噪能力,同时具有更低的硬件成本、更小的速度损失和更低的功耗代价。该设计成功的主要原因在于信号争用被大大抑制。

双晶体管技术[21]为每个下拉晶体管增加了额外的nMOS晶体管,如图2(a)所示。附加nMOS晶体管的漏极端子连接到输入端,以提升源极电压,从而增强抗噪声能力。该技术具有噪声依赖特性,因此无需额外的充电路径。它能显著降低面积占用的同时提高抗噪能力。然而,当这些抗噪晶体管的栅极电压无法保持高电平时,电路将完全丧失抗噪声能力;换句话说,抗噪机制会被破坏。

在双晶体管设计中,噪声电荷可以通过抗噪晶体管传输出去,并且源极电压可以被抬高以增强动态电路的噪声免疫能力。抗噪晶体管的栅极电压决定了抗噪能力的强弱。一旦抗噪晶体管的栅极电压无法维持,其抗噪能力将相应下降。防止栅极电压退化可以保护抗噪机制不被破坏。为了保护抗噪机制不被输入噪声破坏,即使噪声能量较高,文献[31]中提出了INT技术。如图2(b)所示,INT技术包含抗噪机制和噪声隔离机制。抗噪机制可提高下拉网络的源极电压,从而增强动态电路的噪声免疫能力。噪声隔离机制能够将抗噪机制与噪声干扰隔离开来,从而有效维持抗噪能力。图2(b)显示,MNT1和MNT2晶体管提供了传输噪声电荷的路径,因此源极电压得以抬高,增强了动态电路的噪声免疫能力。在评估阶段,MNT3和MNT4晶体管由CLKB关断,分别将MNT1和MNT2的栅极与噪声干扰隔离。通过噪声隔离机制,抗噪机制可以

即使输入噪声能量较大,也能保护其不被破坏。因此,抗噪能力可以进一步增强。然而,INT设计较为复杂,导致在提高抗噪能力时性能损失较大。

防止动态节点悬空是提高动态CMOS电路抗噪能力的另一种流行方法[8],[22–27],[34]。在动态电路的悬空节点上使用弱晶体管是实现这一目标的最简单方法。然而,使用保持器会引起严重的信号争用,因为加速所有下拉放电路径与增强抗噪能力以避免充电路径中的电荷损失这两个目标方向相反。为了实现更优的抗噪能力,由于保持器强度增大以及信号争用更加严重,工作速度进一步降低。在图2(c)[34],中,保持器在进入评估阶段前被关断,并在抗噪声方式下导通,或在评估阶段当下拉网络(PDN)放电时被关断;因此,争用电流可大幅减少,从而减小速度损失并同时维持噪声免疫性。因此,基于XOR的条件保持器设计能够同时满足低功耗、高工作速度和高噪声免疫性的要求,这是最先进的抗噪声动态CMOS电路设计。

3. 动态CMOS电路中的真单相时钟锁存抗噪技术

作为现有抗噪声动态电路设计的替代方案,为防止动态节点悬空并提高PDN晶体管的源极电压,我们提出了一种新方法,通过在噪声进入动态CMOS电路之前直接隔离和滤除噪声,从而增强动态CMOS电路的抗噪能力。由于在动态CMOS电路进入评估阶段之前,噪声已被隔离机制滤除,因此无需再通过增大抗噪机制中晶体管尺寸来提升动态CMOS电路的抗噪能力。噪声隔离机制中的几乎所有晶体管均采用最小尺寸。此外,由于所提出的抗噪机制与PDN的放电路径相互独立,因此可以在保持抗噪能力的同时减小信号争用问题。

在图3中,展示了使用所提出的抗噪声单相时钟电路(TSPCL‐NT)技术设计的双输入动态互补金属氧化物半导体与门。TSPCL机制的基本思想类似于TSPC锁存器或寄存器设计,通过应用锁存功能来隔离不需要的噪声。如图3所示,TSPCL机制被插入到每个输入级中

动态互补金属氧化物半导体电路的操作主要由CLK信号控制。在评估阶段,CLK信号变为高电平,信号传播路径被晶体管M切断。如果噪声通过上方的pMOS mp传输,则会被上方的晶体管M阻断;一旦噪声通过下方的nMOS mn传输,也仅会导致节点F进入浮空状态,而不会引发操作错误。与现有的抗噪声方法相比,所提出的方法的优势在于:无需额外的充电路径来防止浮空状态,也无需在下拉网络中增加额外的放电路径来传导不需要的噪声信号。因此,由于增强抗噪能力而引起的信号争用问题可以得到缓解。这样,不仅能够显著降低下拉网络中因信号争用造成的延迟时间和功耗,还能实现更优的噪声免疫能力。

提出的TSPCL‐NT设计的操作可分为两个方面,即正常工作情况和噪声隔离情况。当动态电路处于预充电条件时,晶体管M导通,输入信号通过两级反相器传输到动态CMOS电路中。该操作与传统动态CMOS电路几乎相同。另一方面,如果输入信号A或B为低电平,则晶体管mn导通,节点GA或GB将放电至低电平。如果输入信号A或B为高电平,则节点GA或GB将充电至高电平,如图4(a)所示。一旦时钟跳变为高电平,动态CMOS电路进入评估阶段,并且在评估阶段期间激活噪声隔离机制。输入信号A与节点GA之间或输入信号B与节点GB之间的信号传播路径全部被阻断。输入状态全部存储在GA和GB的内部节点中。如果输入信号A或B为低电平,则在评估阶段节点GA或GB保持为低电平。如果输入信号A或B为高电平,则通过反馈保持器使节点GA或GB保持为高电平,以避免悬空现象的发生,如图4(b)所示。因此,提出的TSPCL‐NT设计在评估阶段的操作也与传统动态CMOS电路几乎相同,但其输入传播路径被隔离,从而避免了噪声干扰。

对于噪声干扰情况,输入信号A被传递到节点GA,输入信号B被传递到节点GB。当通过关断晶体管M来激活TSPCL‐NT噪声隔离机制时,有效的逻辑状态便能可靠地保持在节点GA和GB处。在TSPCL‐NT隔离机制的保护下,输入端A和B可能受到噪声干扰的影响;然而,由于噪声

传播路径被切断。如图5所示,低到高噪声被晶体管M阻断,无法传递到GA。对于高到低噪声,它仅会导致动态CMOS电路的下拉晶体管关闭,不会引起故障。TSPCL‐NT机制中的噪声隔离示意图如图6所示。所提出的TSPCL‐NT机制能够在存在低到高型或高到低型输入噪声干扰的情况下,保持输出信号的正确性。此外,在所提出的TSPCL‐NT设计中,无需额外的充电路径来抑制噪声。因此,信号争用问题得以大幅减弱,从而在保持抗噪能力强的优势的同时,节省功耗并加快传播速度。

4. 性能比较与芯片实现

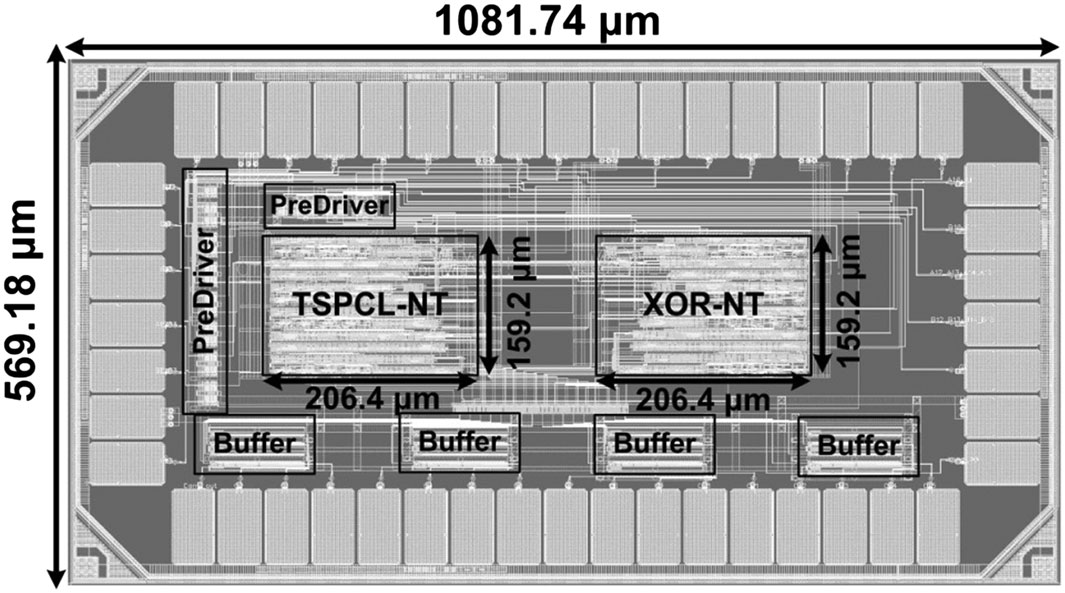

为了展示在噪声存在下抗噪能力的性能,我们将所提出的抗噪技术应用于16位曼彻斯特加法器。在台积电90纳米工艺下,将TSPCL‐NT技术应用于16位曼彻斯特加法器电路,以验证其相较于最先进的XOR‐NT设计具有更优的噪声免疫能力和更低的性能开销。该16位曼彻斯特加法器电路由四个级联的4位曼彻斯特加法器构成,相应的4位曼彻斯特加法器结构如图7所示。性能指标的比较包括噪声免疫、工作速度、功耗以及功耗延迟积。

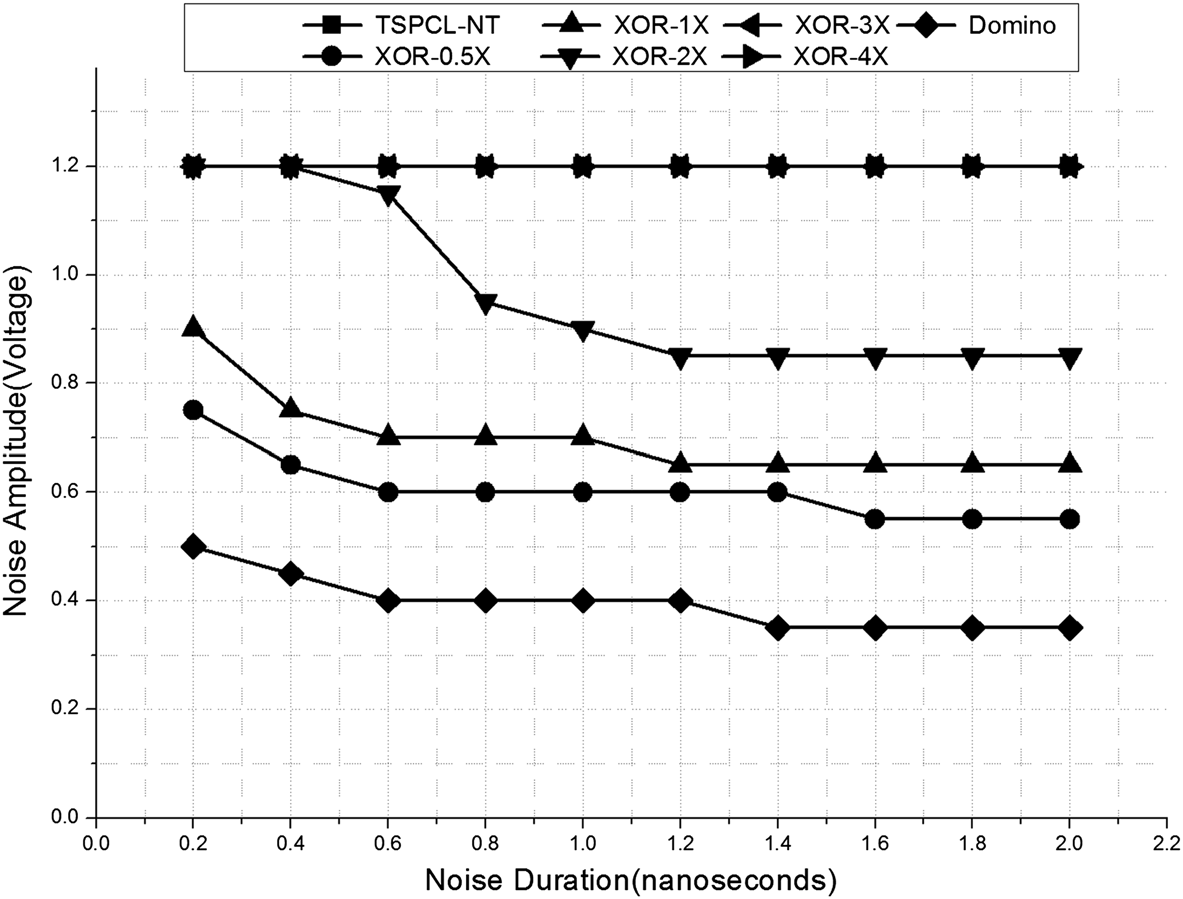

抗噪性能的比较通过噪声免疫曲线(NIC)和平均噪声阈值能量(ANTE)进行评估。我们可以利用NICs[14],[36]来比较应用于16位曼彻斯特加法器的各种抗噪技术的抗噪声能力。该曲线是导致门输出发生翻转的噪声幅度(Vnoise)与宽度(Tnoise)组合的轨迹[14]。NIC方法不仅能满足噪声容限的标准,还考虑了噪声持续时间的影响[36]。ANTE[14]是从NIC直接导出的量化指标,通过对引起功能错误的噪声脉冲能量取平均值得到。ANTE越高,表示电路能够承受的噪声能量越高;换句话说,电路表现出的噪声免疫能力越强[31]。

在图9中,我们绘制了各种抗噪动态电路设计在噪声持续时间为0.2纳秒到2纳秒范围内的噪声免疫容限(NIC)。较高的NIC曲线代表更好的噪声免疫能力。如图9所示,传统动态电路中可容忍噪声幅度仅为0.4伏特,接近晶体管阈值电压。在XOR‐NT设计中,其NIC性能随保持管尺寸的变化而变化。当保持管尺寸为0.5×时,可容忍噪声幅度低于0.6伏特。然而,随着保持管尺寸增大,在保持管尺寸为 1×和 2×的情况下,可容忍噪声幅度分别提升至高于0.65伏特和0.85伏特。在XOR‐NT采用 3× 和 4× 保持器尺寸的设计,可容忍噪声幅度可进一步提升至1.2 V。在提出的 TSPCL‐NT设计中,抗噪机制是通过隔离信号传播路径,而非采用反馈保持器;因此,其对应的NIC位于最上方曲线,且可容忍噪声幅度同样达到1.2 V。从图9可以看出,所提出的 TSPCL‐NT设计在NIC指标上优于最先进的XOR‐NT设计。如表I所示,与传统动态多米诺设计相比,所提出的TSPCL‐NT技术中的ANTE可提升21.14×。与最先进的XOR‐NT设计相比,我们提出的TSPCL‐NT设计中的ANTE对于不同的保持器尺寸可进一步从4.77×提升至1.61×。

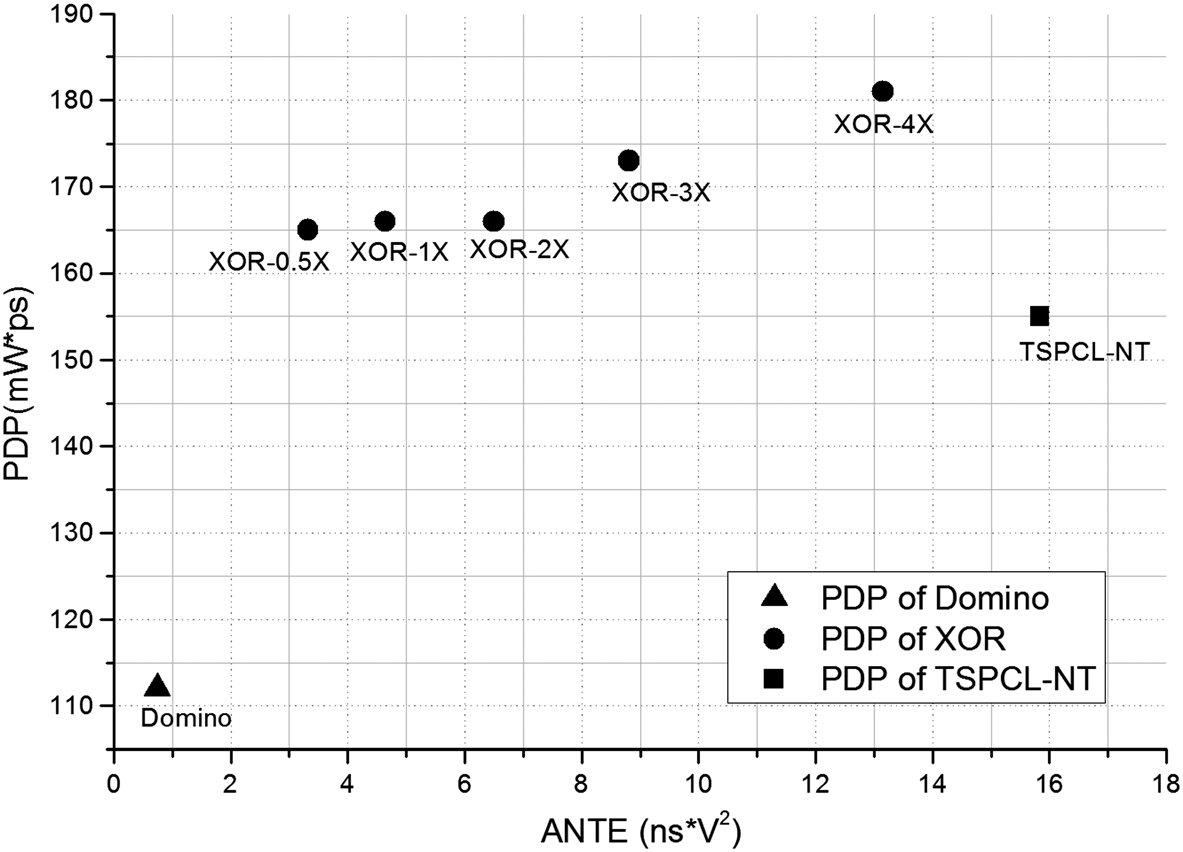

在大多数抗噪动态电路设计中,噪声免疫容限(NIC)会随着保持管尺寸或抗噪晶体管尺寸的不同而变化。然而,在我们提出的TSPCL‐NT设计中,由于噪声传播路径在锁存模式下被隔离,抗噪机制中的晶体管尺寸可以固定为最小尺寸。通过增大保持管尺寸或抗噪晶体管尺寸,可以提高NIC,并增强ANTE以实现更好的噪声免疫能力。然而,设计开销也会随之增加,体现在延迟时间、功耗、功耗延迟积(PDP)和面积方面。我们比较了延迟时间和功耗随不同ANTE的变化情况,针对提出的TSPCL‐NT设计与最先进的XOR抗噪技术在图10中的对比。如图10所示,在计算延迟相近的情况下,提出的TSPCL‐NT设计相比XOR‐2X设计可实现高出2.5倍的ANTE。换句话说,在相同工作速度下,TSPCL‐NT具有更好的抗噪能力。在功耗开销方面,提出的TSPCL‐NT设计始终比XOR‐NT设计消耗更少的功率。即使XOR‐NT采用最小尺寸设计,其功耗仍高于提出的TSPCL‐NT设计。这主要是因为TSPCL‐NT隔离机制的保护作用能够在没有额外充电路径的情况下抑制噪声。因此,由于信号争用减少,功耗得以显著降低。此外,提出的TSPCL‐NT设计相比XOR‐0.5X设计可实现高达五倍的ANTE。换句话说,XOR‐NT设计需要在计算延迟和功耗方面付出更大的设计代价,才能达到与提出的TSPCL‐NT设计相同的ANTE水平。比较结果表明,直接隔离噪声传播路径并释放信号争用问题确实会显著降低抗噪声互补金属氧化物半导体电路中的性能损失。

在图11中,我们进一步比较了提升抗噪能力时在功耗延迟积(PDP)方面的性能损失。如图11所示,TSPCL‐NT设计的PDP和ANTE分别为155 mW*ps和15.84ns*V²。与最先进的XOR‐4X设计相比,PDP降低了16%,ANTE提高了20%。更准确地说,提出的 TSPCL‐NT设计能够在实现更优抗噪能力的同时,带来更小的PDP性能损失。详细的性能对比结果见表I,其中包含了布局前仿真和版图后仿真结果。相比于未采用任何抗噪技术的多米诺电路,NT SIZE为0.5×、4×的XOR‐NT电路以及提出的TSPCL‐NT设计的抗噪能力分别提升了4.43倍、17.57倍和21.14倍。得益于TSPCL‐NT隔离机制的保护,噪声传播路径被隔离,噪声被滤除,且无需额外的充电路径来抑制噪声。因此,功耗显著降低,同时抗噪能力得到增强。在ANTE相当的情况下,TSPCL‐NT电路的功耗延迟积比最先进的XOR‐4X低14%。

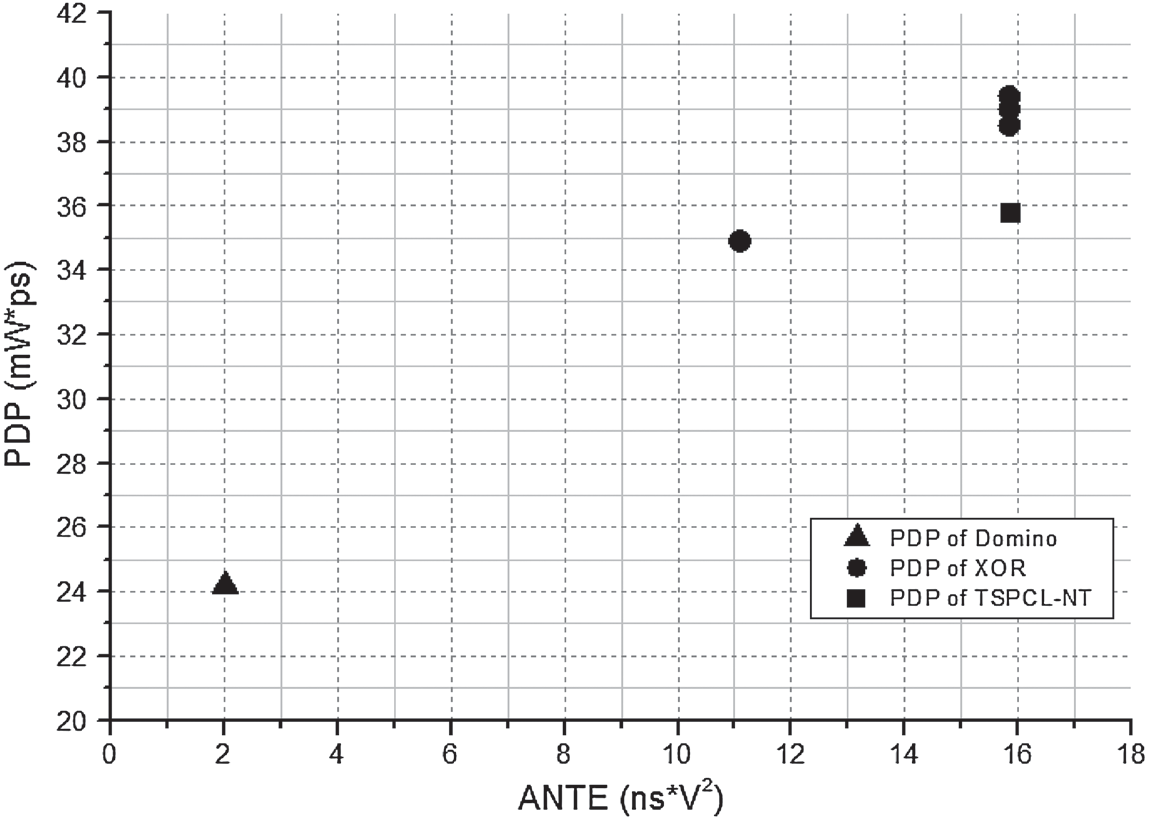

除了曼彻斯特加法器外,所提出的TSPCL‐NT方法还应用于16位动态比较器[37]。在台积电90纳米工艺下,与XOR‐NT设计相比,所提出的TSPCL‐NT比较器也表现出更优的噪声免疫能力和更低的性能开销。与关键路径位于串联连接的下拉网络中的曼彻斯特加法器不同,动态比较器的下拉网络主要由并联连接的晶体管构成。并联连接会导致输出浮动节点处产生更大的寄生电容。因此,在动态CMOS比较器电路中,噪声较不容易引发错误。如图12(a)所示,采用 2×、3×和 4×保持器尺寸的XOR‐NT比较器设计均能容忍1.2 V的噪声幅度。所提出的TSPCL‐NT比较器设计的噪声免疫容限(NIC)仍处于最上方曲线,且可容忍噪声幅度仍可维持在1.2 V。

在动态互补金属氧化物半导体比较器电路设计中,与XOR‐NT模块相比,我们需要应用更多的TSPCL‐NT模块。TSPCL‐NT比较器设计在并联连接的下拉网络架构中会消耗更多功耗。此外,在并联连接的下拉网络架构中,反馈保持器与下拉网络之间的信号争用问题较不明显。因此,在比较器基准电路中,TSPCL‐NT设计在降低功耗延迟积方面的优势较不明显。然而,与提出的TSPCL‐NT设计相比,XOR‐NT设计仍需付出更大的设计代价以实现相同的ANTE。这主要是因为TSPCL‐NT设计可以在无信号争用的情况下实现抗噪能力。与具有 1×保持管尺寸的最先进的XOR‐NT比较器设计相比,所提出的TSPCL‐NT设计中的ANTE可提高1.43×,如图12(b)所示。所提出的TSPCL‐NT设计中的ANTE与具有 2×到 4×保持器尺寸的最先进的XOR‐NT比较器设计相同;然而,所提出的TSPCL‐NT设计中的PDP可分别降低7.5%、8.9%和10.1%。因此,再次证明了所提出的TSPCL‐NT设计能够在动态互补金属氧化物半导体比较器设计中以更小的PDP性能损失实现更优的抗噪声能力。

各类16位抗噪声动态CMOS比较器的NIC比较。(b) 不同16位抗噪声动态CMOS比较器的ANTE与PDP之间的权衡)

5. 结论

本文提出了一种TSPCL‐NT技术,用于增强动态电路中的抗噪能力。在台积电90纳米 CMOS工艺下,与最先进的16位XOR‐NT加法器相比,所提出的16位TSPCL‐NT加法器可实现三倍的ANTE提升,并降低6%的功耗。相对于现有文献设计,提出的TSPCL‐NT设计具有最低的功耗、最短的延迟时间以及更优的噪声免疫性能。

40

40

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?