一款基于90纳米CMOS的K波段可重构脉冲压缩汽车雷达发射机

摘要

本文提出了一款基于90纳米CMOS工艺的K波段超宽带(UWB)脉冲压缩(PC)汽车雷达发射机,该发射机由全集成脉冲发生器、混频器、驱动放大器、锁相环和时序电路组成。采用具有编码增益的脉冲压缩技术可有效提高检测分辨率并改善信噪比(SNR)。所提出的PC发射机实现了快速且精确的码型生成,功耗低、芯片面积小,并具备可重构能力。与此前报道的采用相对简单编码方案的UWB脉冲雷达相比,该发射机采用高速移位寄存器实现更具挑战性的15位伪噪声码设计,可将信噪比提升高达23.5 dB。测量结果表明,不同调制码对应的输出波形正确,频谱严格限制在规范掩模范围内。在调制速率超过3 Gb/s(脉冲重复频率为6.125 MHz)时,可实现5厘米分辨率。

索引词

汽车雷达,CMOS,K波段,脉冲压缩(PC),发射机,超宽带(UWB)

一、引言

T快速增长的市场推动了对低成本、小型化汽车雷达的需求。目前可用的汽车雷达系统大多采用化合物半导体技术实现,集成度相对较低且体积较大。近年来CMOS技术的进步带来了令人印象深刻的晶体管性能,使得CMOS成为微波频段下高度集成且低成本汽车雷达系统的有力候选方案,尤其是在K波段的短程雷达(SRR)应用中。美国联邦通信委员会(FCC)已为22–29 GHz(K波段)的SRR应用制定了标准,规定最大辐射功率为41.3 dBm/MHz[1]。

在严格的发射功率限制下,此类应用采用了超宽带(UWB)雷达技术。UWB方法通过脉冲信号在扩频方式下工作,从而能够更高效地与现有系统共享频谱资源。

先前的研究报道了基于硅锗和CMOS技术的集成K波段超宽带系统在汽车雷达中的良好成果[2]–[9]。一篇全面的教程论文稿件收到日期2014年10月03日;修订于2015年1月12日和2015年1月31日;接受于2015年2月08日。出版日期2015年2月25日;当前版本日期2015年4月02日。本工作由NSC 100‐2628‐E‐007‐030‐MY3项目及台湾科技部(MOST)资助。作者单位为台湾新竹国立清华大学电机工程学系,300号(电子邮件:shhsu@ee.nthu.edu.tw)。本文中一张或多张图的彩色版本可在线获取,网址为 http://ieeexplore.ieee.org。数字对象标识符10.1109/TMTT.2015.2403835

[2]从设计要求和系统架构等不同角度讨论了用于短距离雷达应用的超宽带传感器。本文探讨的一个问题是,系统中分配不同编码以提高抗干扰能力的重要性。然而,为了保持高距离分辨率,需要速度非常快的码生成器。已报道了一款在0.13微米SiGe BiCMOS技术下实现的全集成24 GHz超宽带雷达传感器[4]。该传感器包含一个二进制相移键控(BPSK)调制器以及用于脉冲调制的控制单元。一款在0.18微米SiGe BiCMOS工艺中实现的双频段22–29/77–81 GHz汽车雷达收发器也被展示[6]。尽管芯片中未包含编码功能,但该论文也指出,采用脉冲压缩编码是满足频谱限制并实现与短脉冲相同距离分辨率的有效方案。

最近,有研究报道了一款具备脉冲压缩功能的24 GHz超宽带雷达发射机[7],其采用了2比特双相调制器,并实现了最小距离分辨率为7.5厘米。根据上述文献回顾可以看出,结合适当编码的脉冲压缩技术对超宽带汽车雷达应用具有显著优势。然而,高速编码方案的集成仍然具有挑战性,目前仅报道了如2比特BPSK等相对简单的设计。本研究中,我们报道了一款基于CMOS技术的K波段超宽带发射机,其集成了全集成脉冲发生器,支持15比特可重构编码方案。

本文的结构如下。第二节阐述了脉冲压缩原理以及所提出的发射机架构。第三节详细介绍了基于高速移位寄存器的可重构脉冲发生器设计,以及其他重要基本模块,如混频器和锁相环(PLL)。第四节展示了时域和频谱方面的实验结果。最后,第五节对本文进行了总结。

II. 超宽带雷达中的脉冲压缩

A. 脉冲压缩技术

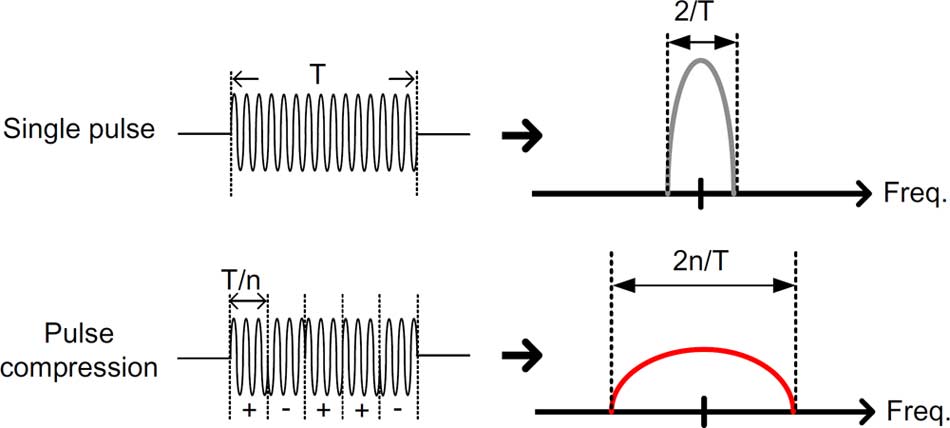

图1说明了脉冲压缩技术的原理,该技术能够提高距离分辨率并改善信噪比(SNR)。如图所示,一个具有脉冲宽度的单脉冲在频谱中具有宽度为(忽略旁瓣)的主瓣。对该脉冲应用比特双相调制后,脉冲带宽扩展为原来的倍,同时信号强度降低。对于超宽带雷达收发器而言,更倾向于使用长脉冲,从而改善信噪比。然而,距离分辨率可能会受到影响。

存在超出辐射功率规定的风险。脉冲压缩技术为此问题提供了解决方案[10],[11]。通过适当地调制信号,可以在时域中使用长脉冲,并在频谱上有效扩展,有助于实现高距离分辨率并保持良好的信噪比,同时满足FCC标准。此外,还可以在脉冲中插入不同的编码方案,以进一步提高超宽带雷达的信噪比。

B. 提出的PC发射机架构

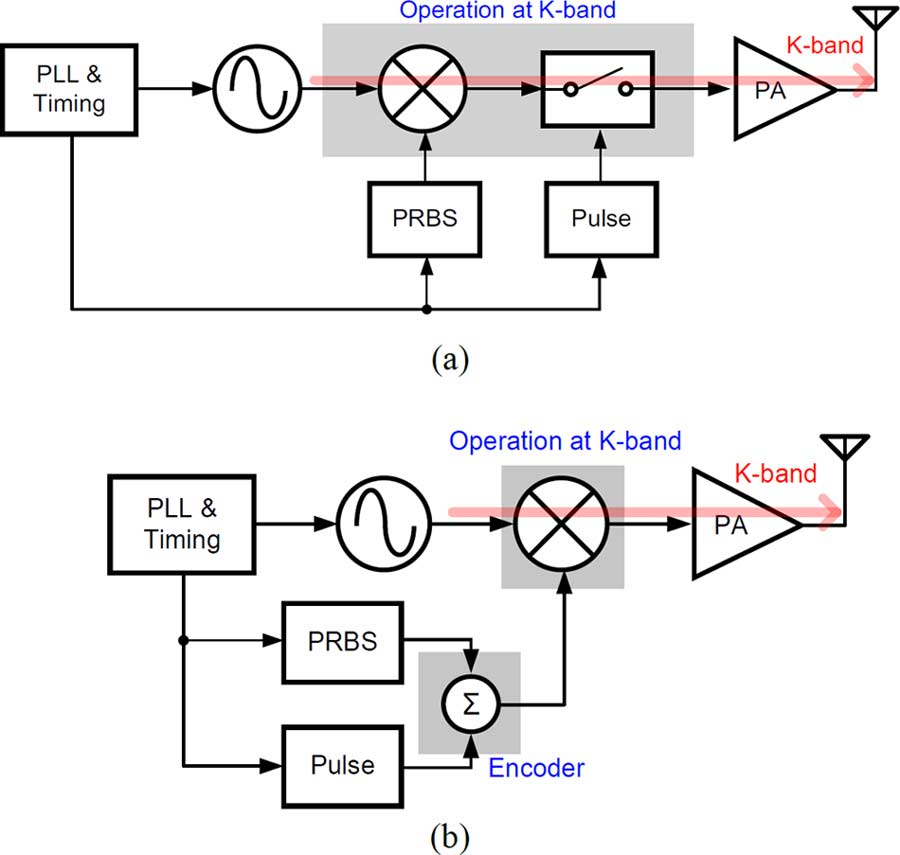

通过使用数字相位调制,可以在发射脉冲中引入伪随机二进制序列(PRBS)码,从而提高信噪比。以往的研究[2]–[4]采用了一种典型的二进制相位调制单脉冲配置,如图2(a)所示。混频器连接到PRBS以改变脉冲的相位,并通过一个开关在输出端控制脉冲的开启与关闭。然而,混频器和开关通常需要感性元件来增强K波段工作的频率响应,导致芯片面积较大。此外,即使脉冲关闭时,混频器仍会持续消耗直流电流,增加了总功耗。在本研究中,我们提出了一种低功耗且面积高效的发射机架构,如图2(b)所示。压缩脉冲在基带合成后,再通过混频器上变频至K波段。与传统设计中PRBS和脉冲按串行顺序处理不同,所提出的架构以并行方式完成该步骤。通过使用高速编码器将相位码和脉冲宽度控制相结合,可生成压缩脉冲。该编码器由静态逻辑门实现,意味着在脉冲关闭期间混频器无额外功耗。同时,不再需要开关,从而实现更小的芯片面积。需要强调的是,在本设计中,脉冲的相位编码和宽度控制均由高速移位寄存器完成。为移位寄存器提供同步时钟对于确保正确的脉冲压缩至关重要,这在实际设计中也是一项极具挑战性的任务。下文将对此进行详细讨论。

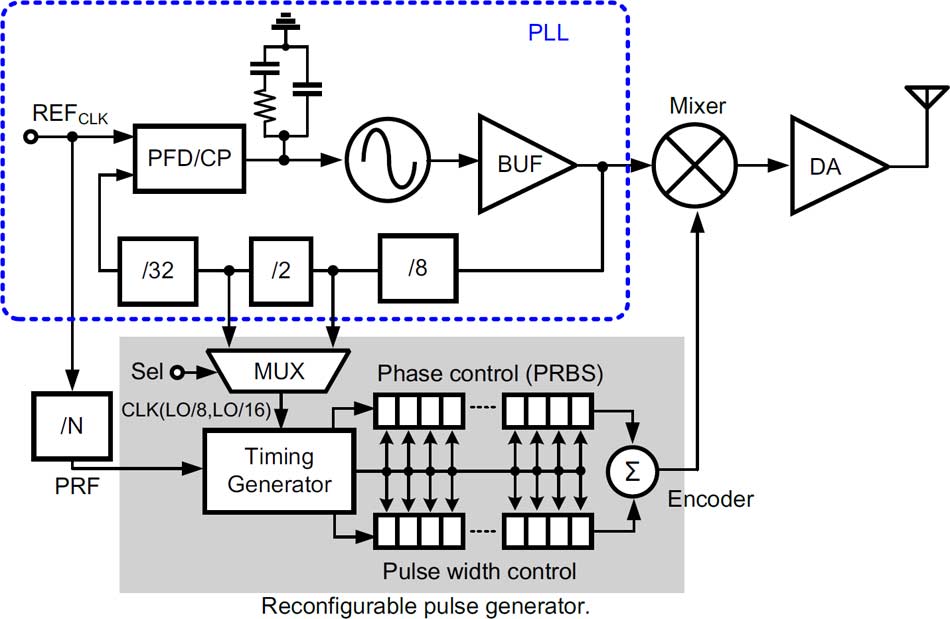

图3显示了提出的PC发射机的详细系统框图,其中包括锁相环(PLL)、时序发生器、可重构脉冲发生器、混频器和驱动放大器(DA)。锁相环为混频器提供K波段本地振荡器(LO)信号,同时作为可重构脉冲发生器的高速时钟信号(CLK)。注意,25.088吉赫兹的频率接近中心频率

该频段(22–29 GHz)被选作PLL工作频段以满足FCC掩模要求。可重构脉冲发生器可提供包含最多15位数字码的基带脉冲,输出脉冲宽度和编码可通过片上串并接口(SPI)在外部软件控制下进行定义。选择15位码长的原因在于可在压缩脉冲中使用巴克码,这非常适用于脉冲雷达应用[2]。理论上,采用15位编码可使信噪比提高23.5 dB。根据具体应用需求,也可采用较短的码长。时序发生器可为高速移位寄存器提供合适的时序信号。混频器将编码后的基带脉冲上变频至K波段。最后,数模转换器提供增益及50 Ω输出,用于测量。

C. 设计参数分析

在超宽带雷达系统中,必须考虑多个设计参数。其中一个重要的参数是脉冲重复频率(PRF),它决定了最大探测距离,如公式(1)所示,其中c为光速,

(1)

对于短距离雷达应用,典型的为20米[2],,这导致脉冲重复频率为7.5兆赫。在此设计中,通过使用分频比为8的分频器,从49兆赫的参考时钟生成6.125兆赫的脉冲重复频率。对应的为24.5米。

距离分辨率在超宽带雷达中也具有至关重要的意义。超宽带脉冲雷达的分辨率可由公式(2)确定,其中为脉冲宽度,为脉冲带宽。

(2)

为了在短距离雷达应用中实现5厘米分辨率,最小脉冲宽度应接近皮秒级吉赫兹。由于发射脉冲的宽度由高速移位寄存器定义,因此输入时钟也需能够在约3吉赫兹下工作。在此设计中,高速时钟可通过锁相环的分频链生成,包括多路复用器的LO/8和LO/16吉赫兹,其中最大时钟速度可达3.136吉赫兹。发射机中提供的多种时钟速度可灵活适用于不同应用,如盲点检测(0.1–0.2米)或泊车辅助(0.05–0.2米)。

另一个重要问题是,发射机的发射功率必须符合FCC规定,即在22–29 GHz范围内,平均等效全向辐射功率(EIRP)应小于41.3 dBm/MHz。发射机的峰值可通过公式(3)计算,其中为相位编码波形的占空比。

dBm MHz

(3)

通过完全集成的锁相环生成本振、时钟信号和信号,可以表示如下:

PRF

(4)

其中,为PLL的总分频数(本例中为512),为可重构脉冲发生器的分频数,为PRF的分频数,为工作期间启用的调制位。考虑输出最大脉冲带宽的情况(、均设为8),假设射频端合理的带宽为2 GHz,则可计算为0.029。根据公式(3),PC发射机对应的为12 dBm。在典型天线增益为15 dBi的情况下,PC发射机的输出功率应约为3 dBm。由此可见,采用脉冲压缩技术所需的输出功率小于单脉冲雷达,这使得基于CMOS技术的全集成发射机更加实用。同时,系统的直流功耗也可有效降低。

III. 脉冲发生器及其他基本模块

A. 可重构脉冲发生器

精确获得脉冲宽度以及同步相位码和脉冲宽度控制序列较为困难

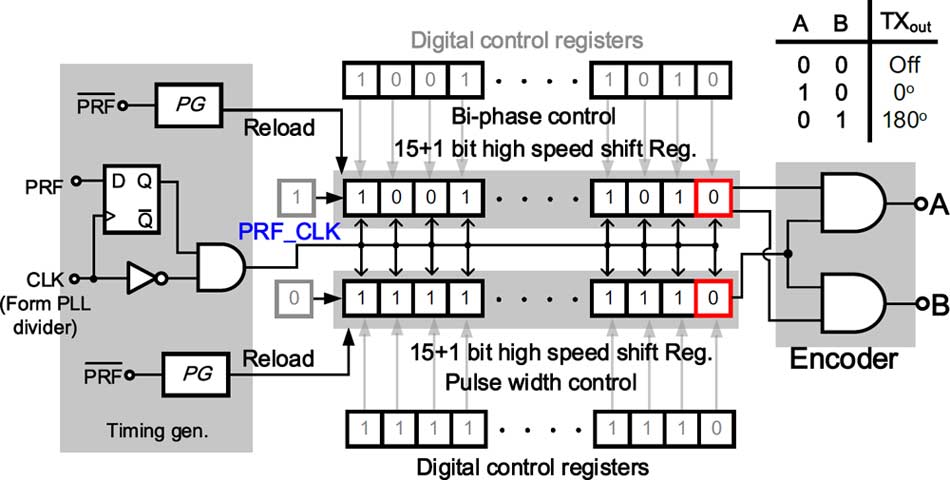

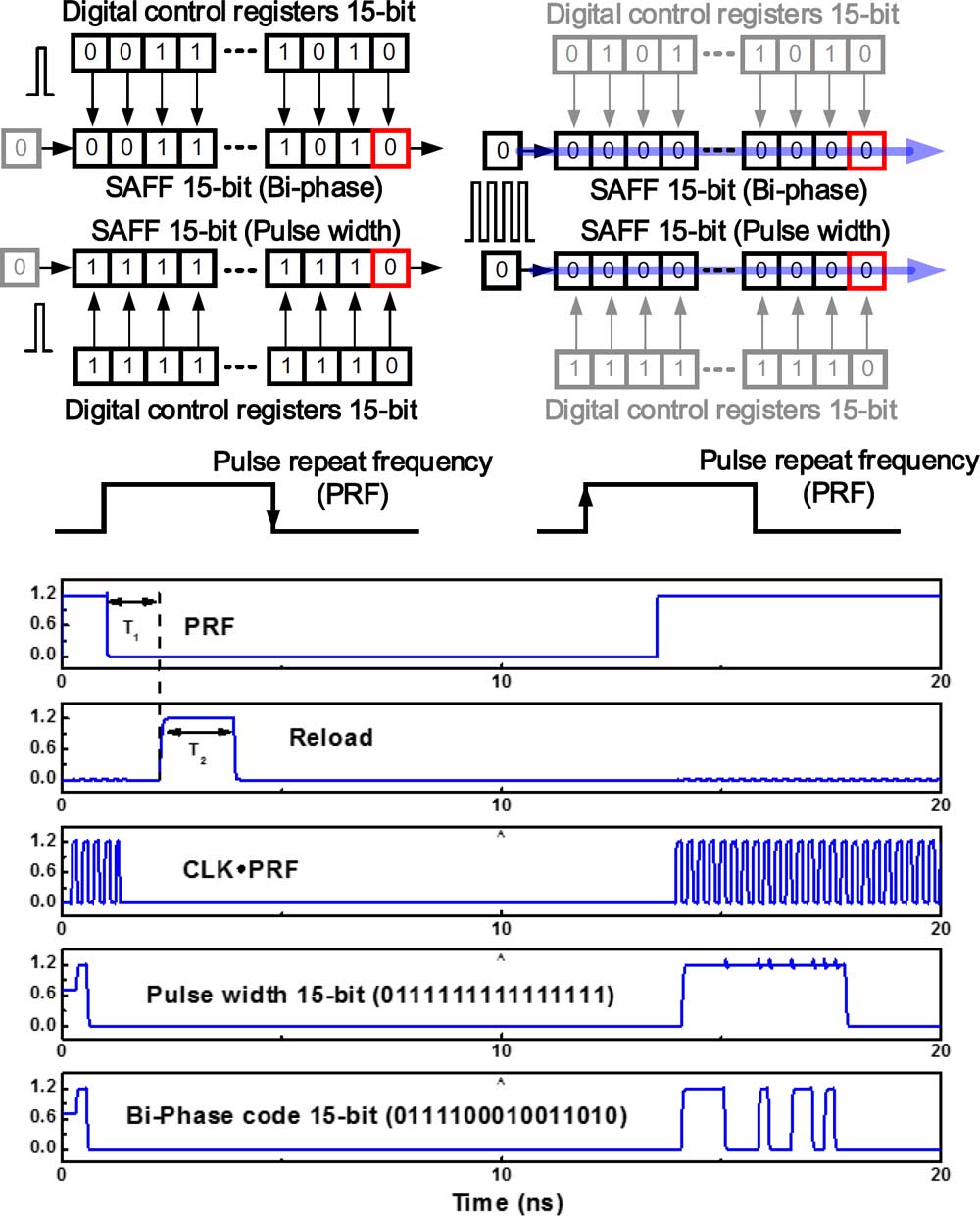

图4展示了所提出的可重构脉冲发生器,它由两个并联的16位高速移位寄存器组成,分别用于控制波形的二进制相位和脉冲宽度。需要注意的是,第一位仅用于初始化脉冲生成,实际可编程位为15位。

如图4所示,来自锁相环分频器的时钟和脉冲重复频率信号首先在时序发生器中同步。通过使用与逻辑,可生成用于驱动高速移位寄存器的时序信号()。脉冲发生器(记为PG)将启动从SPI存储的值向高速移位寄存器的重载操作。在此步骤之后,时钟会将寄存器(并入串出)的值移位至编码器。该编码器由两个与逻辑组成,以实现三态发射机输出,包括“ , ,”、“ , ,”和“ , ,”,分别表示关断状态、0相位和180相位。注意,“ , ”不会出现在编码器的输出端。

图5展示了使用40兆赫的脉冲重复频率信号和4吉赫时钟信号的仿真时序序列和操作细节。在PRF信号下降沿之后,脉冲的重载信号(记为Reload)出现,其中是为避免与Reload之间发生时序重叠而设置的延迟,且的宽度应确保初始值能从SPI准确重载到高速移位寄存器中。在本设计中,和分别为850皮秒和2纳秒。在PRF信号上升沿,高速移位寄存器中的相位码和脉冲宽度的值将被移位至编码器。请注意,脉宽控制寄存器中的“1”的数量必须与相位控制寄存器中的码长相同。如图5所示,当脉宽控制链中存储的值在脉宽控制的第一位被移位为“0”时,PC发射机将被关闭。另一方面,当脉宽控制中存储的值为“1”时,发射机输出信号的相位由双相控制位决定。通过进一步将编码器输出信号与本振混频,可在数模转换器输出端生成K波段相位编码波形。

B. 高速移位寄存器

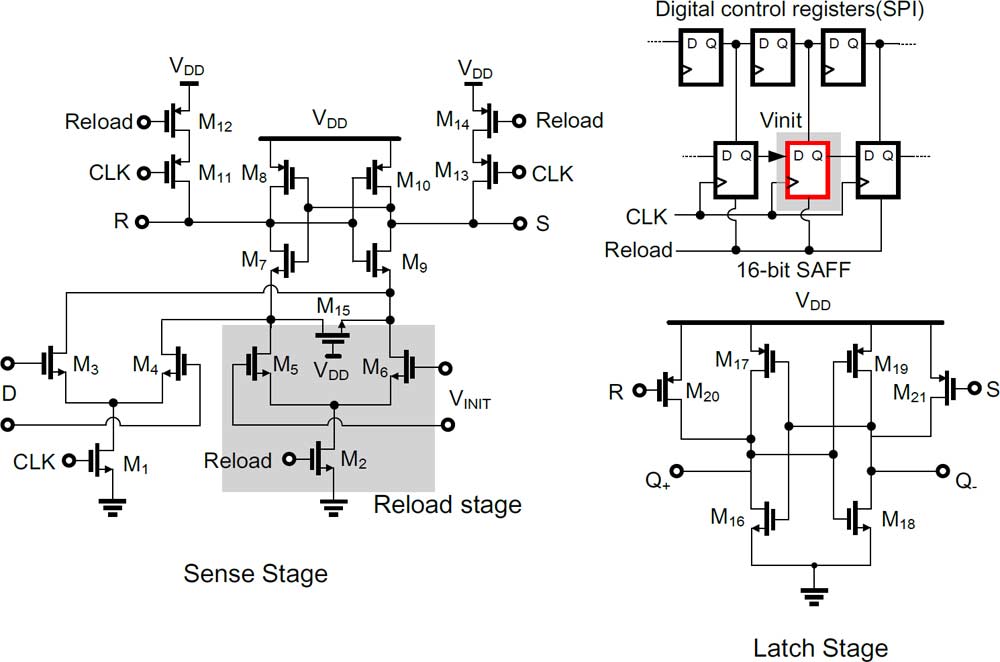

用于千兆赫操作的高速移位寄存器通常由电流模逻辑(CML)实现,但其相对较大的功耗是一个主要问题[9]。已有研究提出了一种基于灵敏放大器的触发器(SAFF)[12],该触发器表现出优异的高速操作能力且功耗降低。本研究采用了基于灵敏放大器的逻辑

在具有重载级的高速移位寄存器设计中,实现了用于脉冲压缩的并入串出功能,如图6所示。在脉冲重复频率信号的导通期间,感应级的输入端与前一级的输出端相连,可实现串行数据传输。同时,重载级的输入端连接至SPI寄存器,以便在重载信号上升沿到来时将初始值并行加载到灵敏放大器型触发器中。当时钟信号和重载信号关闭时,锁存级能够保持灵敏放大器输出的电平值。基于灵敏放大器的D触发器应能支持高达3.136吉赫兹的串行输出。需要注意的是,具有额外寄生参数的电路使得高速操作更具挑战性。具体而言,重载级带来的额外寄生电容增加了负载并降低了性能。

锁存器的速度。在此设计中,使用了相对较大的尺寸以消除输入级的速度瓶颈,而则保持较小以减少重载级的寄生效应。尽管较小的和也会减缓重载操作,但重载操作无需高速运行。如前所述,重载信号接近2纳秒,足以完成信号的重载。

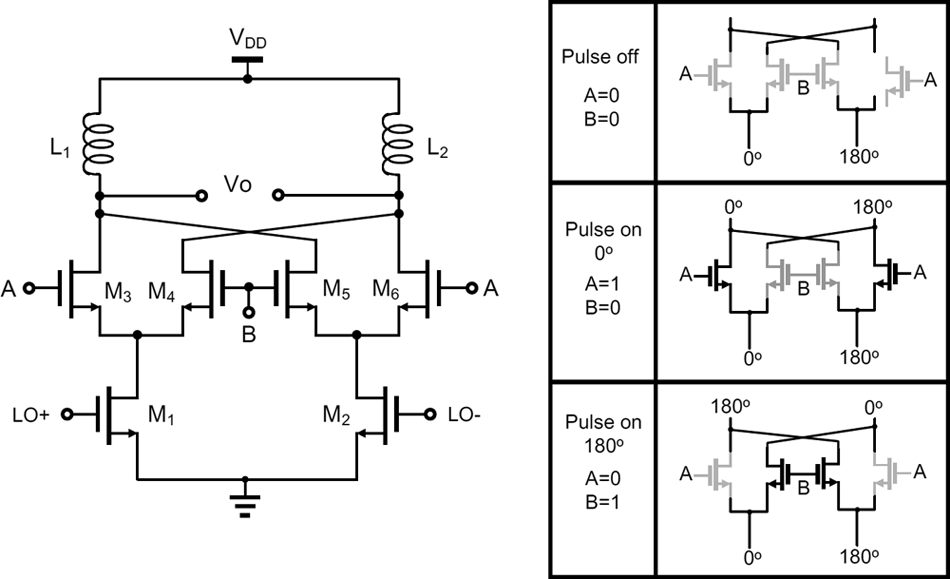

C. 混频器和数模转换器

在所提出的设计器件中,混频器的功能有两个:一是开关K波段本振,二是生成BPSK调制信号。图7展示了电路结构及其工作原理。当脉宽链的值变为“0”时,编码器A和B的输出可以将混频器关闭;当该值变为“1”时,双相控制链可以控制混频器的相位。输出。如图所示,输出路径的相位可以保持不变或进行切换,从而生成BPSK调制信号。基于所提出的混频器和编码器,该发射机无需额外的电路来切换本振信号,能够有效降低功耗和芯片面积。

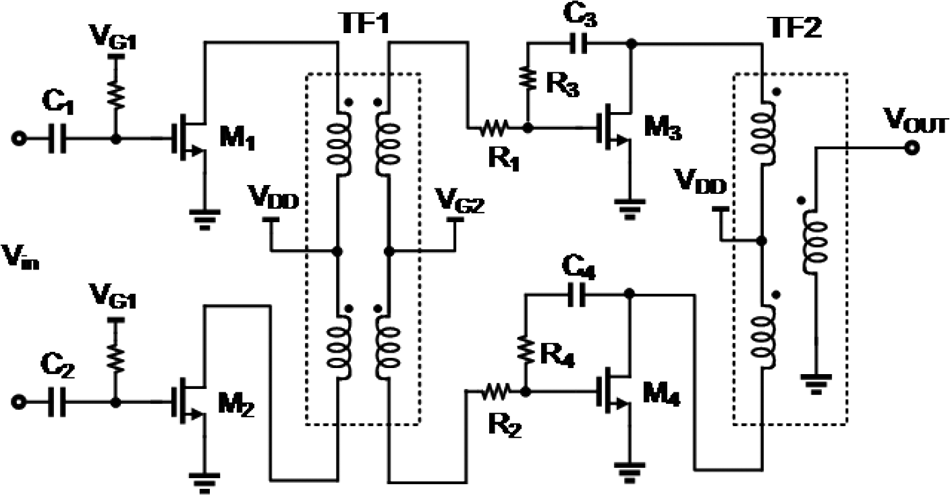

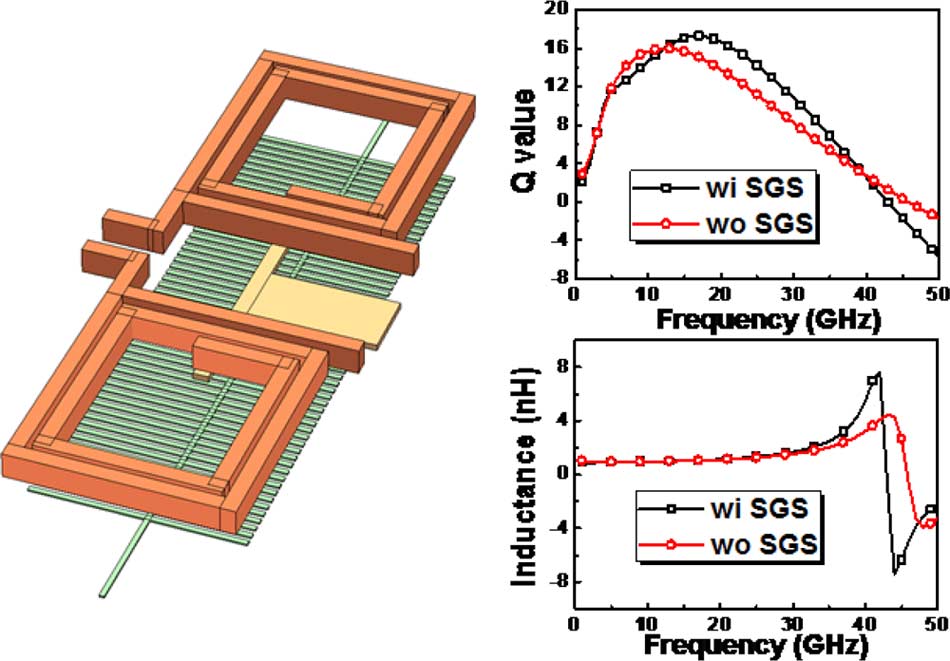

图8显示了采用两级共源放大器拓扑设计的数模转换器,以提高输出功率并改善混频器的隔离度。变压器用于级间和输出端以实现匹配。采用堆叠结构用于变压器以提高耦合系数。通过调节驱动放大器的栅极偏置,PC发射机的输出功率可在0到10 dBm范围内可调。此外,在混频器和数模转换器设计中,电感元件采用了图形化地屏蔽(PGS)技术,以降低来自压控振荡器(VCO)的衬底耦合。需要强调的是,即使在发射机输出被关闭的情况下,通过衬底泄漏的VCO信号仍可能严重劣化电路性能。PGS技术为此问题提供了有效解决方案,显著改善了各模块的衬底隔离度[13]。本文还采用了简单地屏蔽(SGS)技术[14],该方法在仿真和实现上相对简便。与未使用SGS的情况相比,SGS技术可使电感的(25 GHz时的nH)提高约27%,如图9所示。

D. 锁相环

发射机的锁相环采用集成架构设计,以实现高频工作,其中包括基于LC谐振槽的压控振荡器(VCO)、512分频链、鉴相鉴频器(PFD)和电荷泵(CP)。环路滤波器采用片外元件,以减小芯片尺寸。基于

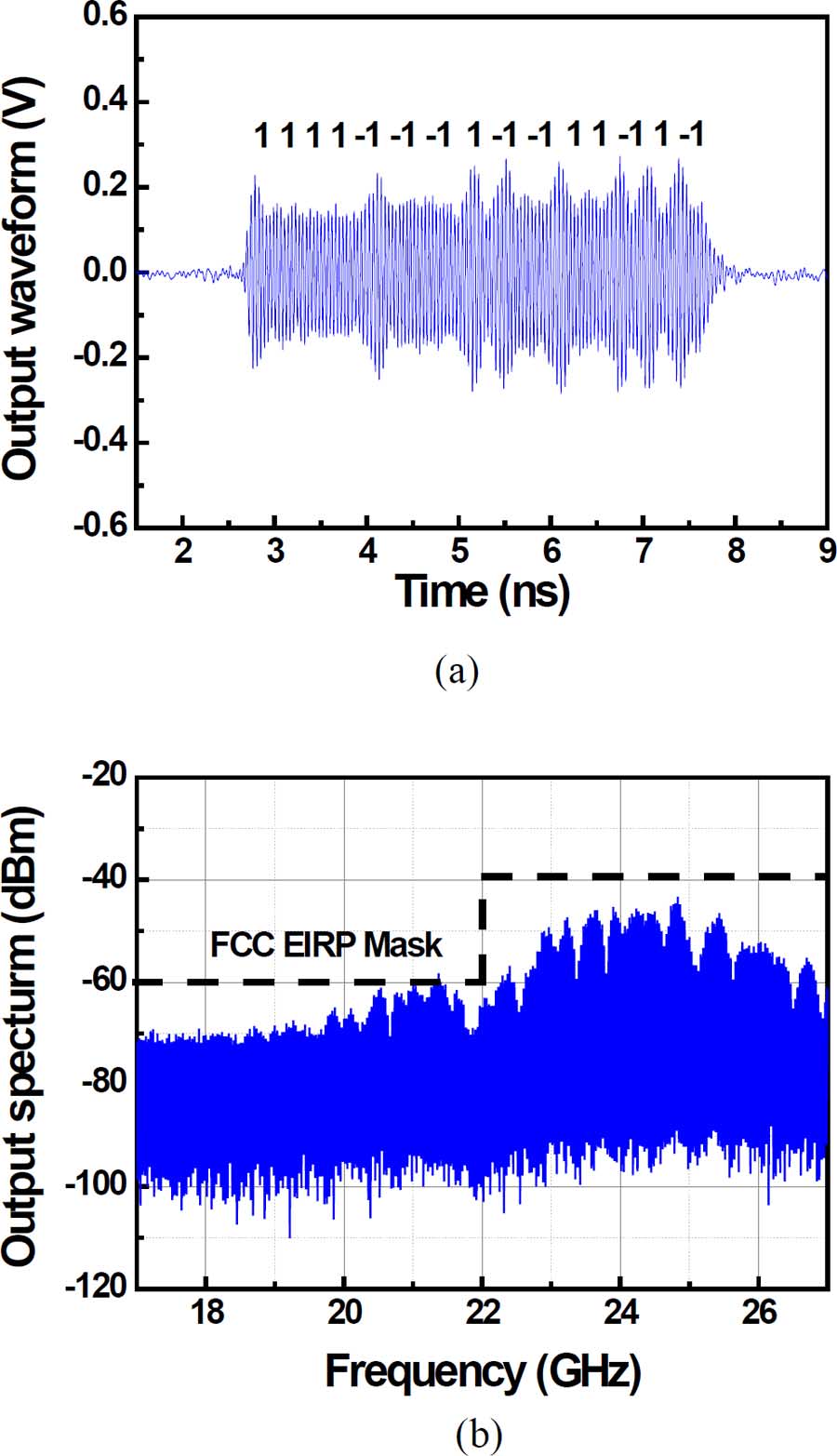

超宽带雷达发射机在15位双相调制下的输出波形和 (b) 归一化输出频谱)

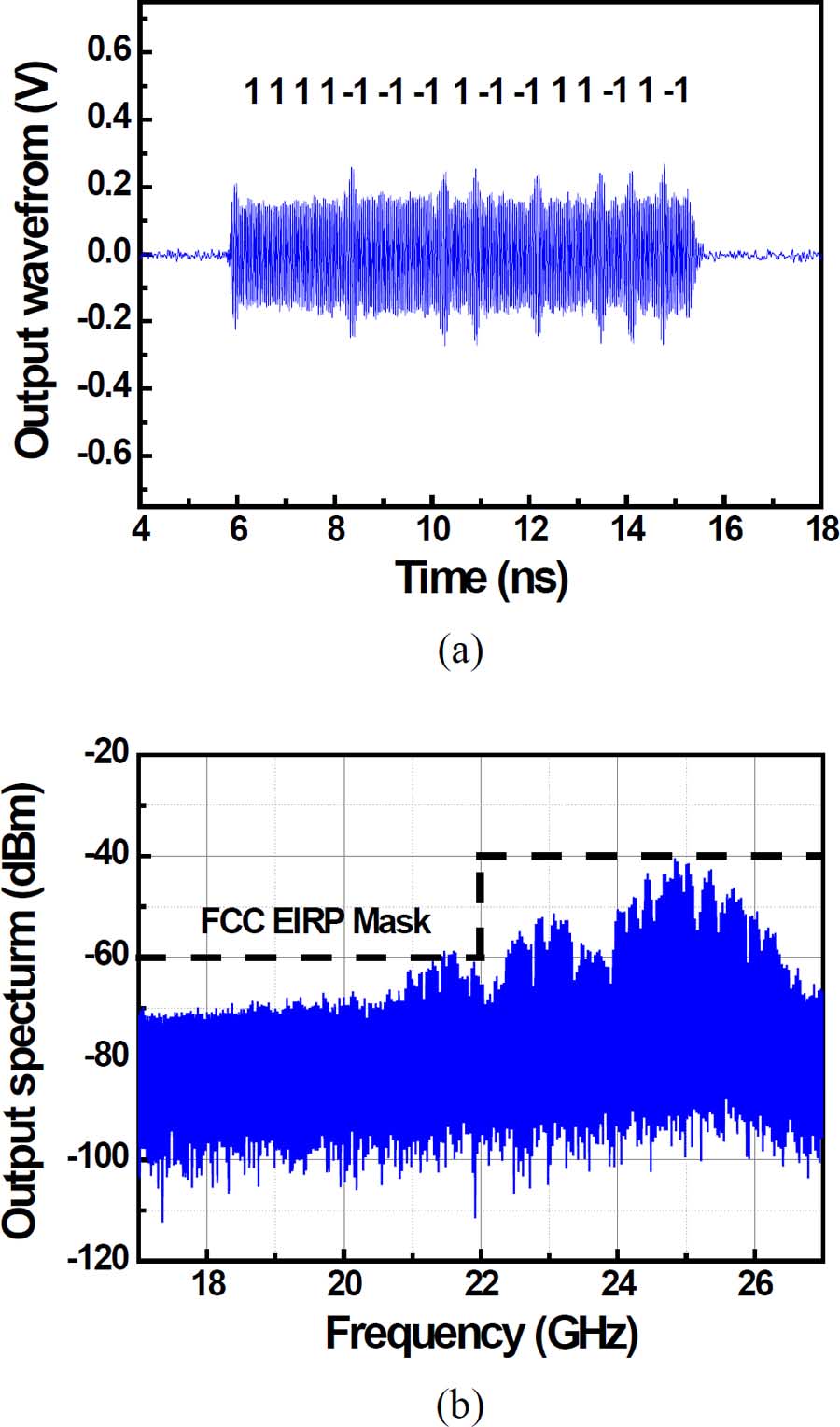

超宽带雷达发射机在15位双相调制下的输出波形和 (b) 归一化输出频谱)

根据仿真结果,压控振荡器的调谐范围为24.7至27.25吉赫兹,能够覆盖锁相环在25.088吉赫兹的期望工作点。第一级采用基于环形的注入锁定/4分频器[15]以减小锁相环的面积。该分频器在仿真基础上可在19至27吉赫兹频率范围内工作,并支持200毫伏信号注入。第二级分频器采用CML实现,低频分频链则通过扩展型单相时钟(E-TSPC)实现。在49兆赫兹参考时钟下,鉴相频率检测器设计中采用基于单相时钟(TSPC)的结构以实现高速操作,电荷泵中采用电流导向技术。此外,与电流模多路复用器并联的分频链在分频器输出节点和处为可重构脉冲发生器提供时钟。

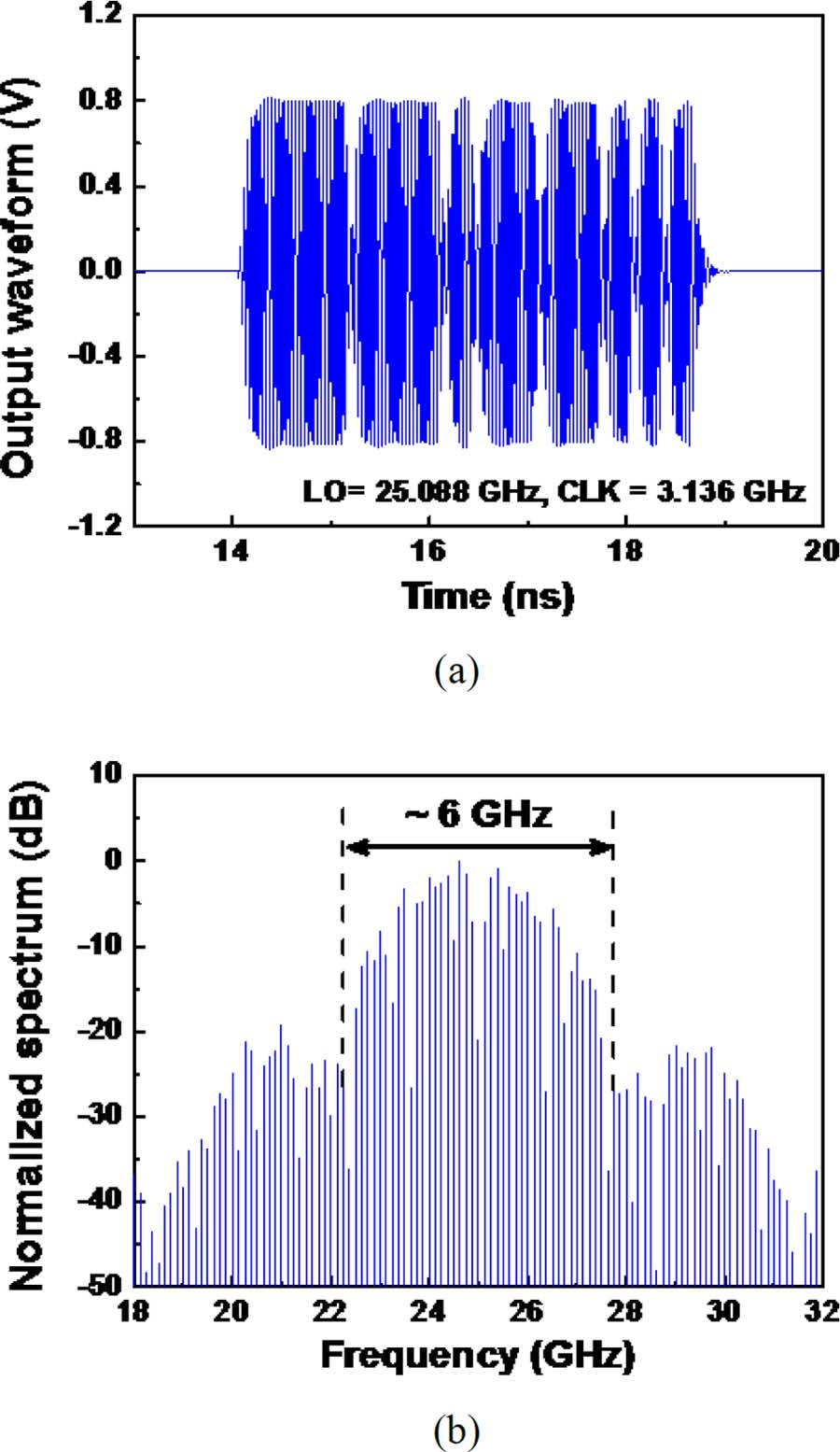

图10(a)和(b)分别显示了超宽带雷达发射机的仿真输出波形和频谱。请注意,本振和时钟吉赫时钟吉赫使用了理想信号源,以保持合理的仿真时间。调制长脉冲5纳秒的仿真结果表明输出中存在预期的双相调制波形。此外,输出频谱显示出接近6吉赫兹的主瓣,这是由于脉冲压缩导致频谱扩展的证据。

IV. 测量结果

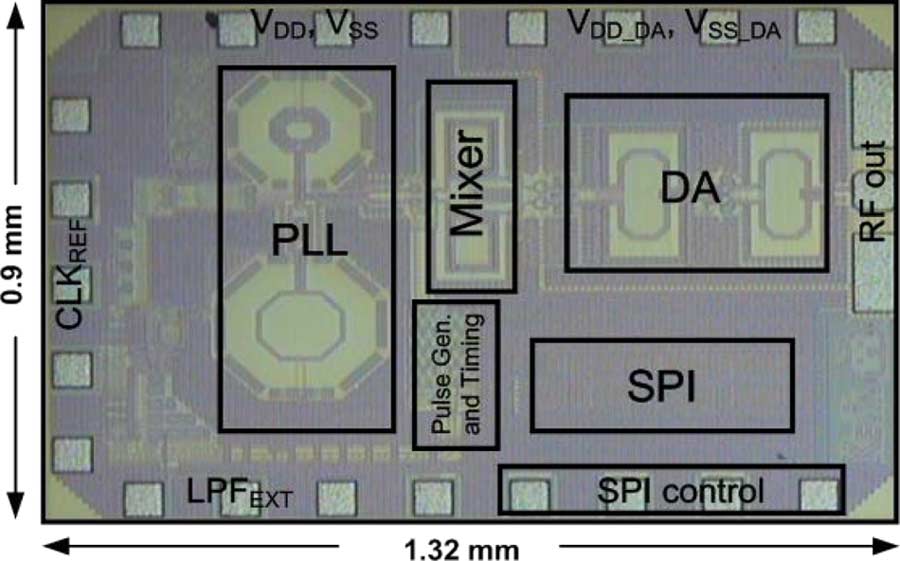

提出的PC发射机采用90纳米1P9M CMOS工艺实现。芯片显微照片如图11所示,芯片尺寸为1.32毫米×0.9毫米 =1.188平方毫米,包括探针焊盘(有源区仅为0.66平方毫米)。PC发射机安装在印刷电路板(PCB)上,通过键合线使用外部电源提供直流偏置。射频特性在晶圆上通过探针台测得。测试芯片还包括SPI,用于提供数字控制信号。时域瞬态波形和频域特性分别使用安捷伦DSOX92504A 80GSa/s实时示波器和安捷伦E4440A 26.5GHz频谱分析仪测得。锁相环环路带宽接近100千赫兹,工作范围为24.37至26.98吉赫兹。在1.2伏特供电电压下,参考时钟为49兆赫兹,锁相环输出频率为25.088吉赫兹。在锁相环锁定状态下,相位噪声为96.15分贝每赫兹,杂散电平为44.25分贝。图12(a)和(b)显示了测得的

时域和(b) 频域 兆赫)

时域和(b) 频域 兆赫)

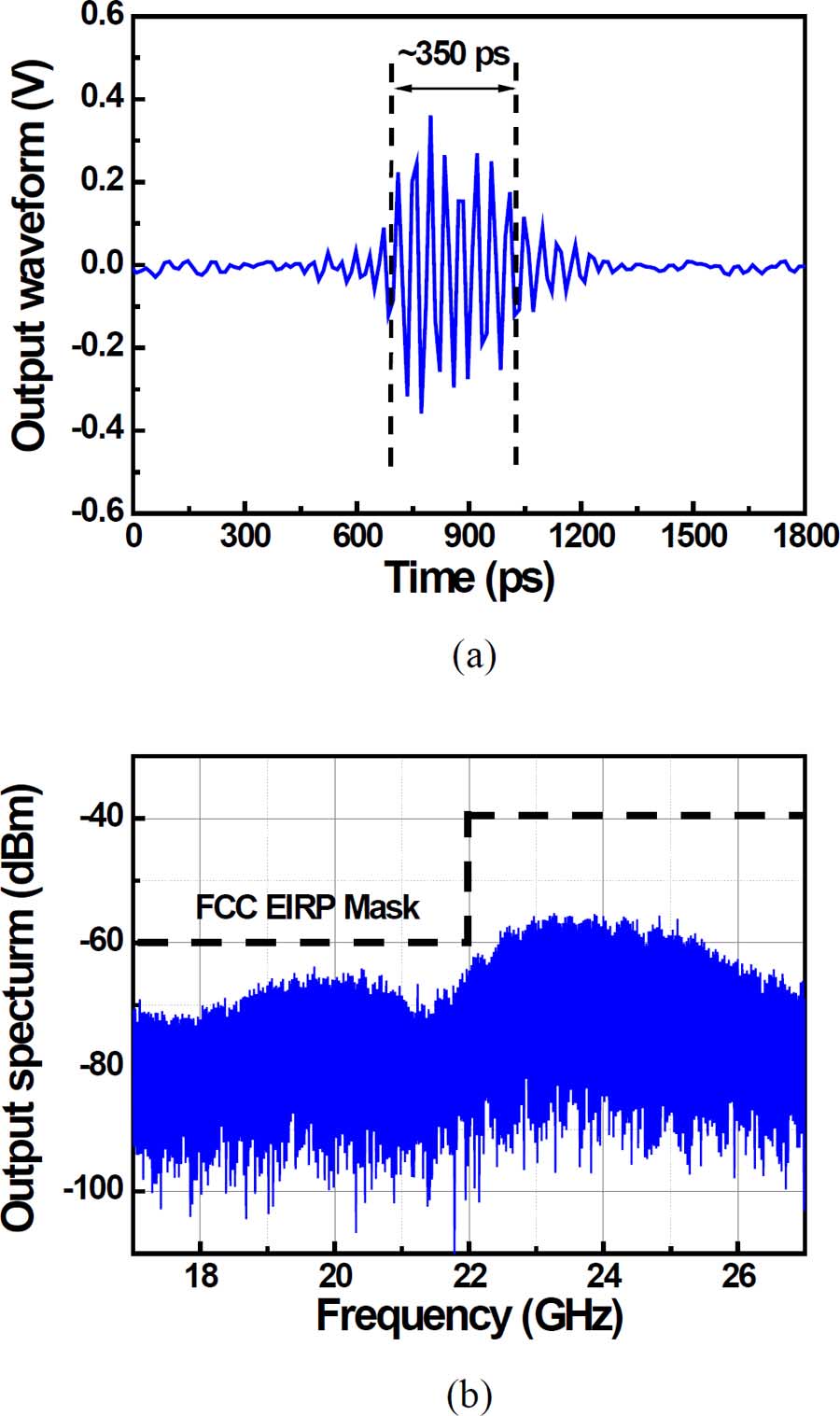

分别为时域和频域中的单脉冲。注意,频谱测量的分辨率带宽(RBW)为1 MHz,且频谱的最大频率受测量设备限制。单脉冲通过在脉宽序列链中仅使能1位生成。来自PLL的注入时钟频率为3.136吉赫兹(25.088 GHz /8),脉冲宽度接近350 皮秒。图13显示了测得的15位BPSK脉冲压缩波形,其中脉宽序列的15位寄存器链全部使能,并采用最大长度序列(MLS)码(1111–1–1–11–1–111–11–1)进行双相控制,时钟速度为3.136吉赫兹。总脉冲宽度接近5.25 纳秒(5.25 ns = 350 皮秒 × 15)。图14(a)和(b)显示了当时钟变为1.568 GHz(LO/16)时的测量结果。注意,在这两种情况下,旁瓣在测量频率范围内均低于FCC等效全向辐射功率掩码。此外,应指出的是,图13所示的测量结果在脉冲宽度和频谱扩展方面与仿真结果(见图10)具有非常好的一致性。基于时域和频域的测量结果,所提出的K波段雷达发射机成功实现了具有15位调制的可重构输出脉冲压缩波形。表I总结了所提出的K波段雷达发射机的性能及其与先前工作的比较。

时域和 (b) 频域 兆赫)

时域和 (b) 频域 兆赫)

时域和 (b) 频域 兆赫)

时域和 (b) 频域 兆赫)

| 表I | PERK波段汽车雷达发射机性能总结及与先前工作的比较 |

|---|---|

V. 结论

已在90纳米CMOS技术中实现了一款K波段超宽带可重构脉冲压缩雷达发射机。压缩脉冲可同时提高雷达的检测概率和分辨率。通过采用基于灵敏放大器的具有并入串出功能的移位寄存器,实现了高速、低功耗、高面积效率的脉冲发生器。与以往仅支持2位BPSK设计的研究相比,所提出的汽车雷达发射机能够支持15位可重构编码方案,并实现超过3 Gb/s的调制速率。测量结果表明,输出波形正确,频谱严格符合FCC规定。借助片上集成锁相环,该K波段汽车雷达发射机可实现5厘米分辨率,最大探测距离达24.5米。

776

776

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?