文章目录

这一部分是对于内存的学习,这一部分要理解的东西很多,需要很多前提知识,我的建议还是得先了解内存的工作原理,这样后续接触到新概念将会快速的理解和记住。

推荐B视频:用最好的动画为你讲解–内存的原理_哔哩哔哩_bilibili

本次主要讲解:

- 多模块存储器

DRAM && SRAM

这里的具体讲解可以参考B站视频:先收藏!考前必看!一个视频搞定 DRAM和SRAM~_哔哩哔哩_bilibili

| SRAM VS DRAM | ||

|---|---|---|

| 类型特点 | SRAM | DRAM |

| 存储信息 | 触发器(双**稳**态) | 电容(MOS + 电容) |

| 破坏性读出 | 非 | 是 |

| 读出后需要重写?(重生) | 不需要 | 需要 |

| 运行速度 | 快 | 慢 |

| 集成度 | 低 | 高 |

| 发热量 | 大 | 小 |

| 存储成本 | 高 | 低 |

| 易失/非易失性存储器 | 易失(断电后容易消失) | 易失(断电后容易消失) |

| 需要“刷新”? | 不需要 | 需要 |

| 送行列地址 | 同时送 | 分两次送 |

| 作用 | 常用作Cache | 常用作主存 |

DRAM的地址引脚复用技术:

在学习DRAM时,最不能绕开的就是DRAM芯片的地址引脚复用技术,但是理解这个技术,我们必须先对DRAM与SRAM的物理结构有个大致的想象和了解。

SRAM和DRAM的存储结构:

通过对前面知识点的学习,我们知道对于数据的存储,往往是需要一个地址来存储起来的,同时当CPU去存储器早数据时,也是通过地址来找的!

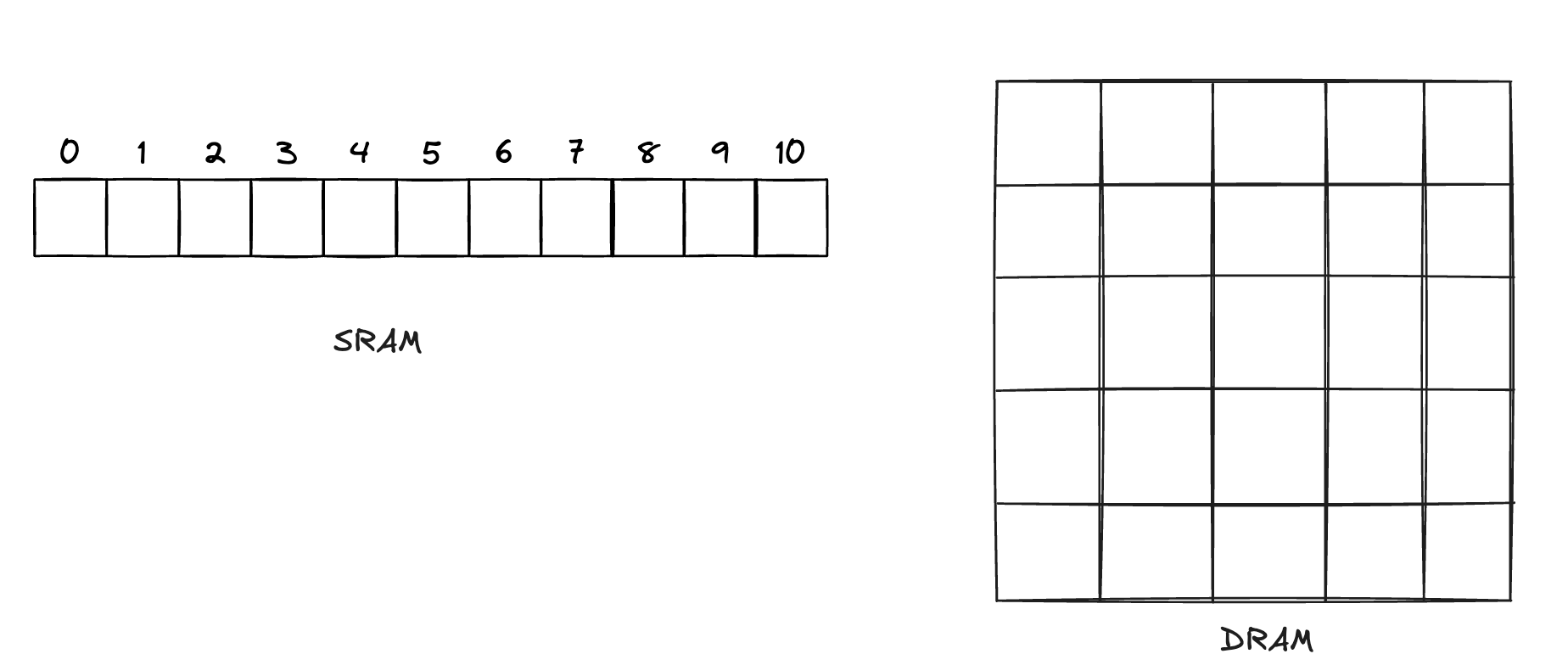

- 先来说说SRAM,SRAM的存储结构类似于一个“数组”,每个地址可以直接访问,非常适合做缓存。

- 但是对于DRAM呢,DRAM的芯片容量较大,地址位数较多,如果我们依然采用“数组”的方式,这个数组将会特别的“长”,因此聪明的科学家为了**减少控制复杂度和节省布线,采用了“行列复用”的矩阵结构,更像一个“二维表格”**,通过分段的地址选择来读取数据。(如下图所示,这样子来看,查找效率就大大增加)

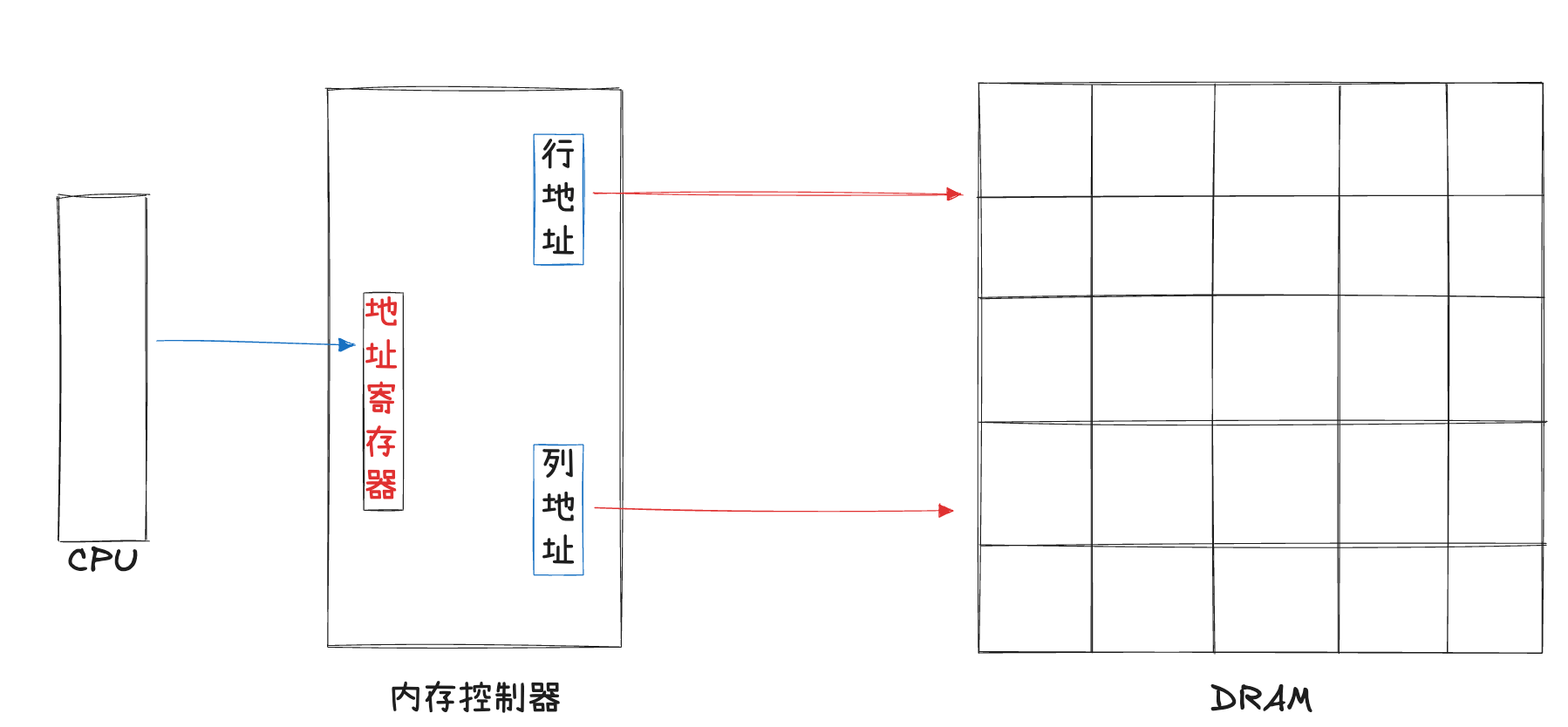

CPU怎么查找到DRAM的具体位置?

理解DRAM结构的优势

首先我们要知道,地址线和地址的关系,我们应该用二进制的方式去理解二者的关系。

2根地址线,就能表达出4个地址,从2进制的角度来看也很好理解。(不理解的话,我觉得是C语言指针部分学习不是很充分,可以去搜一搜指针,那部分会有顺带介绍的)

所以如果当我们的DRAM芯片达到了$ 2^{20} $的容量时

如果我们不采用地址引脚复用技术,那只是开数组,就要开辟**十万多个地址线**,但是正因为有了地址复用技术,使得其结构变为了一个“二维数组”,我们就会发现,我们就只需要1024行 * 1024列,就能实现存储了。

1024行,不就是$ 2^{10} $嘛,所以对于行来说,只需要10根地址线,那对于列地址,不也只需要10根地址线嘛,所以总共需要20根地址线。(从十几万根的地址线 -> 20根地址线,这个升级可想而知)

引入地址复用技术

到这里,我默认大家已经了解好了地址线和地址的关系。那我在这里就想补充一点,地址线是数据在传输过程中的逻辑“线路”,用于传输地址信号。

而有一个东西是用来连接地址线的 —— 地址引脚

地址引脚十分的宝贵,秉持着能省则省的原则,即便我们已经从十几万根地址引脚 优化到了 20根地址引脚,聪明的科学家仍然不满足于此,所以就有了 —— “地址引脚复用技术”

具体操作

第一步:CPU 发地址

- CPU 通过总线发送完整的地址(假如是 11 位地址,用来访问 2K × 1bit 的 DRAM)

第二步:地址寄存器拆分

- 地址被加载到控制器中的地址寄存器

- 然后拆分为“行地址”和“列地址”(例如拆成 5 + 5 位)

第三步:行地址阶段(RAS)

- 控制器先通过地址引脚把“行地址”发送给 DRAM

- 同时发送一个 行地址选通信号(RAS, Row Address Strobe)

- DRAM 接收行地址,选中目标“行”

第四步:列地址阶段(CAS)

- 紧接着,同样的地址引脚再次发送“列地址”

- 同时发出 列地址选通信号(CAS, Column Address Strobe)

- DRAM 根据列地址选中列

第五步:定位数据单元

- 通过行地址 + 列地址确定 DRAM 中的某个“交叉单元格”

- 读取(或写入)对应的数据位(1bit)

最终如图所示,DRAM只需要准备5个地址引脚就可以满足CPU访问存储器的操作了!!!

DRAM的刷新操作

DRAM 为什么要刷新?

在比对 DRAM 和 DROM 的构成时,我们会发现 DRAM 是由多个电容所构成的,**而电容的电荷会自然泄漏,所以必须定期刷新以保持数据不丢失。 **

DRAM电容上的电荷一般只能维持1~2ms,因此即使电源不断电,信息也会自动消失。此外,读操作会使其状态发生改变(破坏性读出),需读后再生,这也是称其为_**动态存储器的原因。 **_

为了防止数据丢失,DRAM 设计了刷新机制(Refresh Cycle):

- 定期地读取每一行的数据,然后再写一遍回去,以“重充电”。

- 通常每个存储单元每 64ms 都要被刷新一次。

刷新方式

刷新可以采用读出的方法进行,根据读出内容对相应单元进行重写,即读后再生。对同一行进行相邻两次刷新的时间间隔称为刷新周期**,通常取2ms。**常用的刷新方式有以下3种:

集中刷新:在一个刷新周期内,利用一段固定的时间,依次对存储器的所有行进行逐一再生,在此期间停止对存储器的读写操作,称为“死时间”,又称访存“死区”。优点是读写操作时不受刷新工作的影响;缺点是在集中刷新期间(死区)不能访问存储器。

分散刷新:将一个存储器系统的工作周期分为两部分:前半部分用于正常的读写操作;后半部分用于刷新。这种刷新方式增加了系统的存取周期,如存储芯片的存取周期为0.5us,则系统的存取周期为1us。优点是没有死区;缺点是加长了系统的存取周期。

异步刷新:结合了前两种方法,使得在一个刷新周期内每一行仅且刷新一次。具体做法是将刷新周期除以行数,得到相邻两行之间刷新的时间间隔t,每隔时间t产生一次刷新请求。这样就使“死时间”的分布更加分散,避免让CPU连续等待过长的时间。

$ t \ = \ \frac{刷新周期}{行数} $

DRAM的刷新需要注意以下问题:

①刷新对CPU是透明的,即刷新不依赖于外部的访问;

②动态RAM的刷新单位是行,由芯片内部自行生成行地址;

可以参考下列视频所讲述的:计算机组成原理 | 求解需要的芯片数量 如何计算刷新间隔时间 什么是异步刷新 什么是集中刷新_哔哩哔哩_bilibili

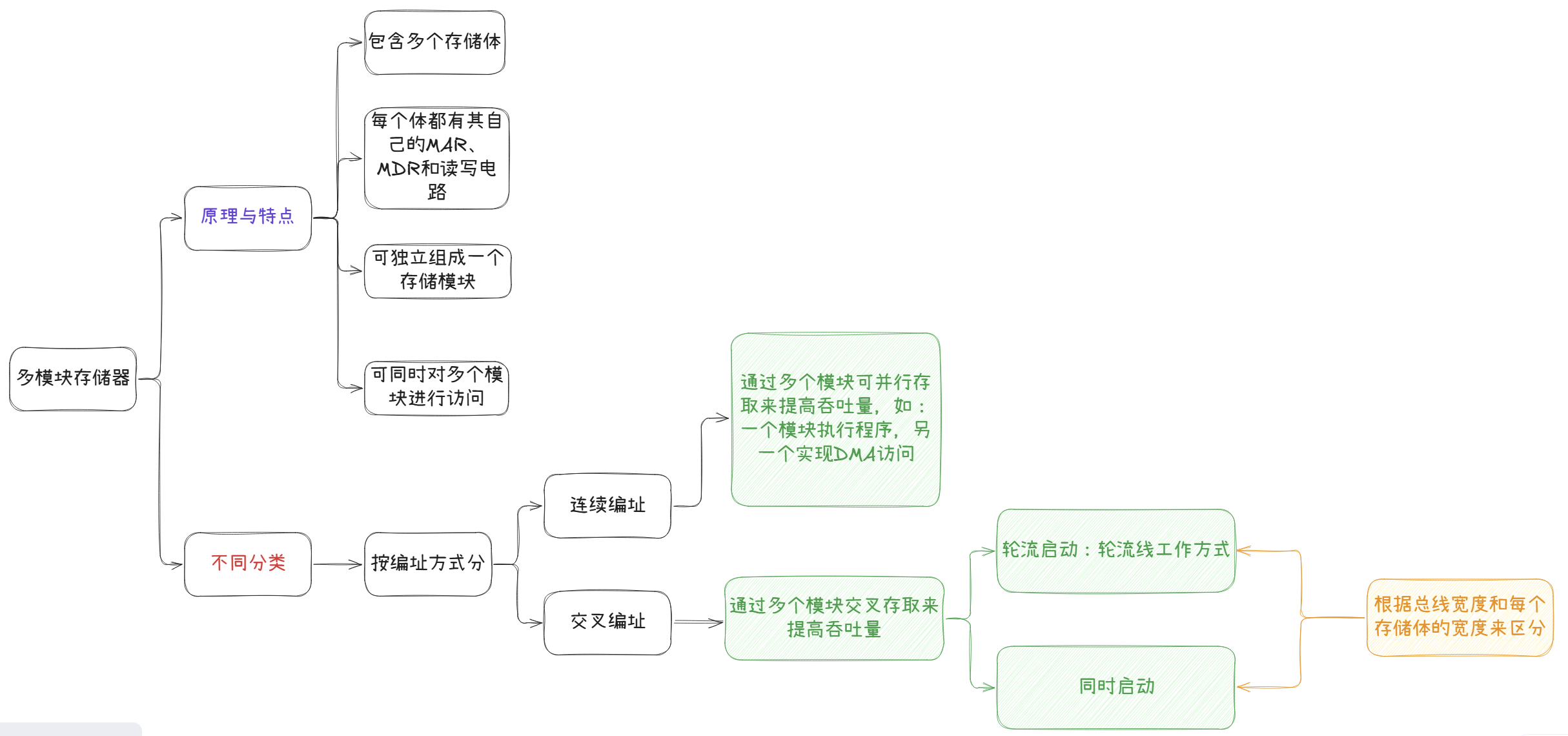

多模块存储器

这个视频阐述的到位:

计组3.2 多模块存储器(高位交叉编址 & 低位交叉编址)_哔哩哔哩_bilibili

多模块存储器得出现是为了提高存储器速率。

经典例题

:::color2

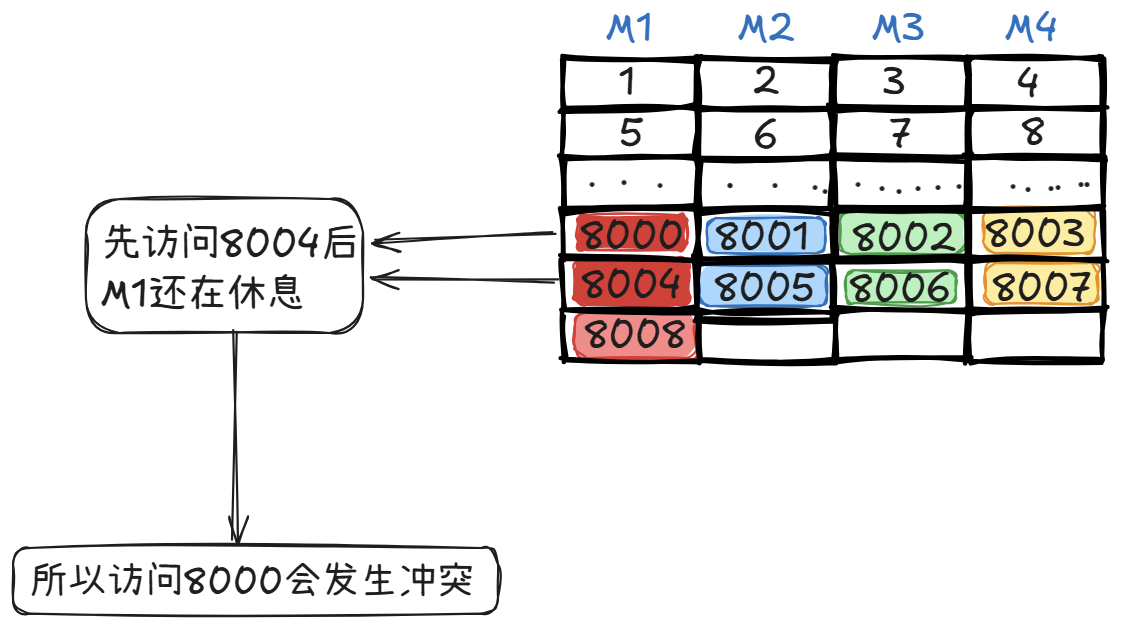

某计算机使用四体交叉编址存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生访存冲突的地址对是()。

A.8004 和 8008

B.8002 和 8007

C.8001 和 8008

D.8000 和 8004

:::

3529

3529

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?