1、仲裁机制

仲裁机制用来确保任意时刻只有一个主机能够访问总线。仲裁器的功能是检测许多不同的使用总线的请求和决定当前请求总线的主机中哪一个的优先级最高。

在一次AHB传输开始之前总线主机必须被授予访问总线。这个过程开始于总线主机向仲裁器断言一个请求信号。仲裁器指示主机何时能够被授予使用总线。被授予的总线主机通过驱动地址和控制信号来发起一次AHB传输。这些信号提供关于地址、方向和传输宽度的信息,以及表示传输类型是否为突发传输的部分。

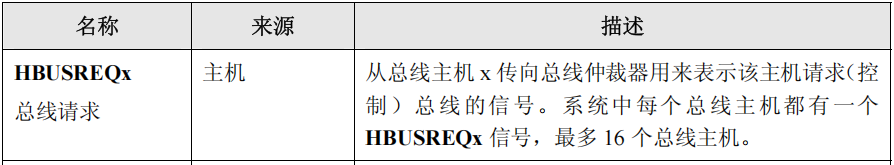

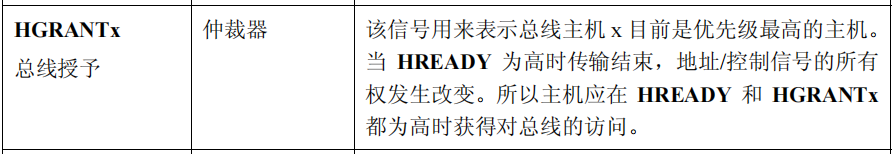

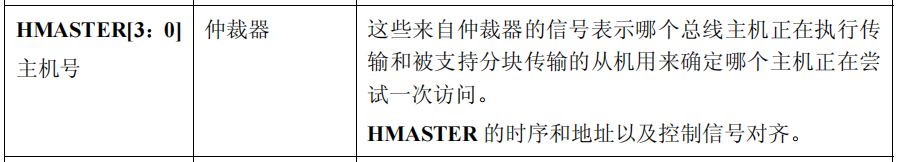

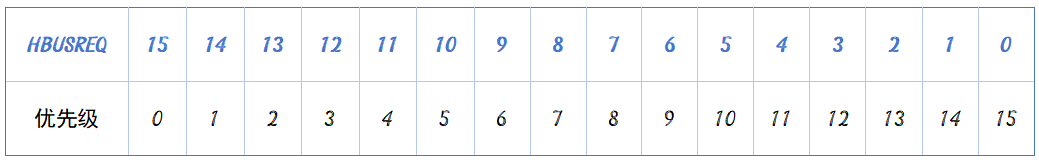

相关信号说明:

2、实验目标

本次实验中我们需要设计AHB总线的仲裁器模块,并使用固定优先级和轮转优先级两种方法实现。

2.1 固定优先级仲裁器设计

本实验中将最低位主机优先级设为最高,最高位主机优先级设为最低, 即当HBUSREQ=16'hFFFF时,仲裁器将赋予0号主机总线使用权。

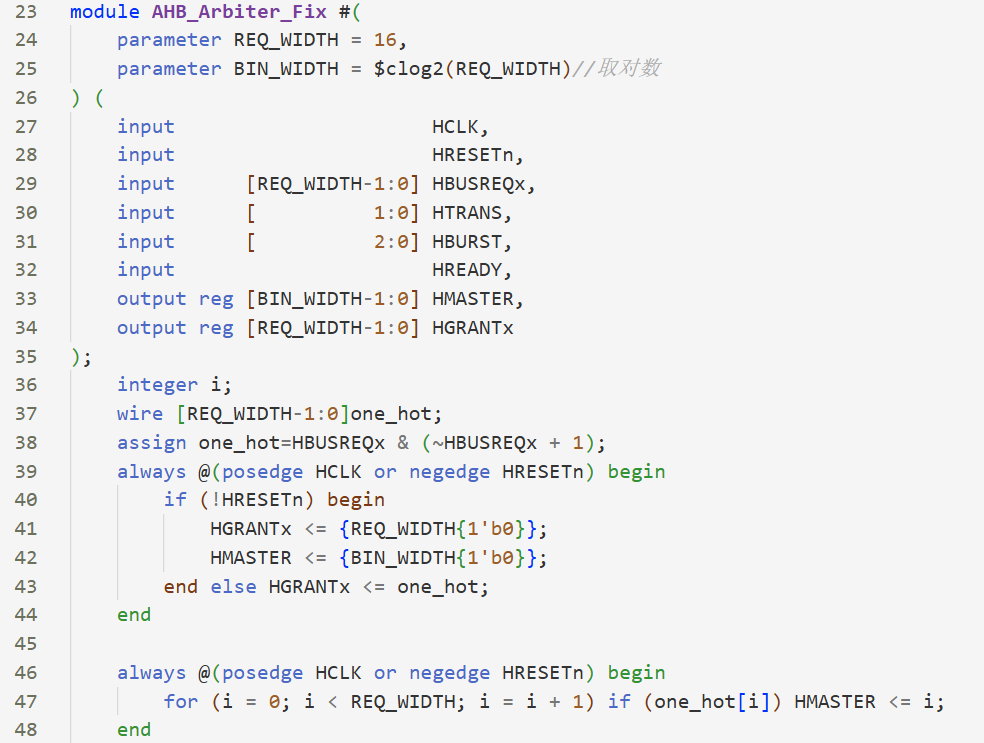

因此我们需要确定HBUSREQ中从最低位开始第一个1出现的位置,通过分析可知,二进制数与它的补码相与所得到的独热码即为我们要赋给HGRANTx的值,如00001011&11110101=00000001,该二进制数第一个1出现的位置为0。我们将这个位置赋值给HMASTER即为对应的主机号。可参数化仲裁器模块代码如下图所示,输入输出信号可由实验手册中的模块框图确定:

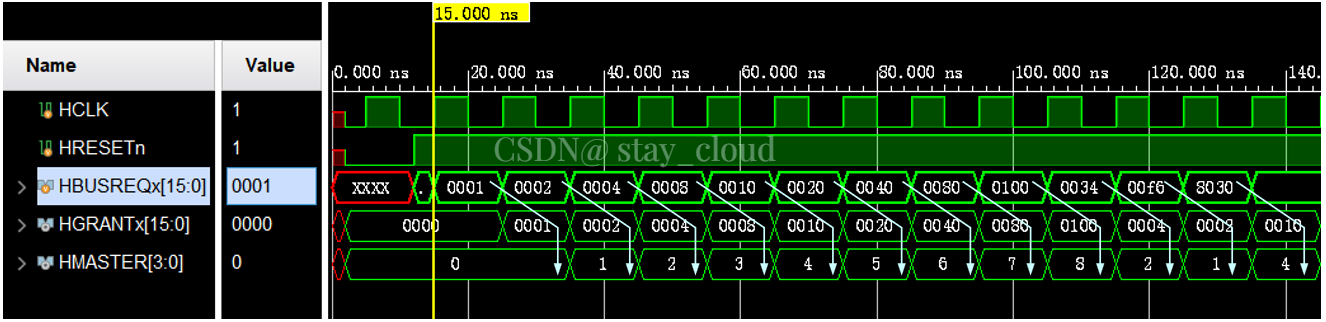

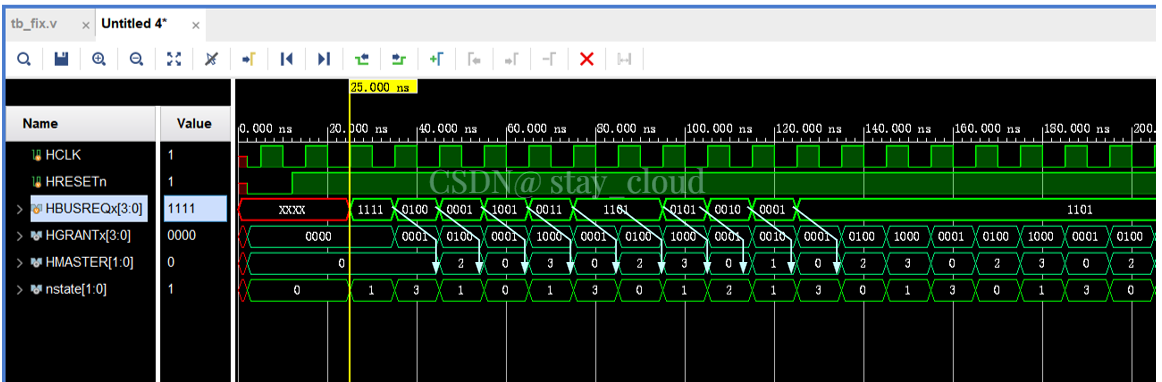

最后我们需要在激励中给出HBUSREQ信号进行测试,仿真结果如下图所示,本设计中的总线授予信号HGRANTx和主机号HMASTER均在主机发出总线请求后的下一个时钟周期给出。仿真结果与预期一致。

2.2 轮转优先级仲裁器设计

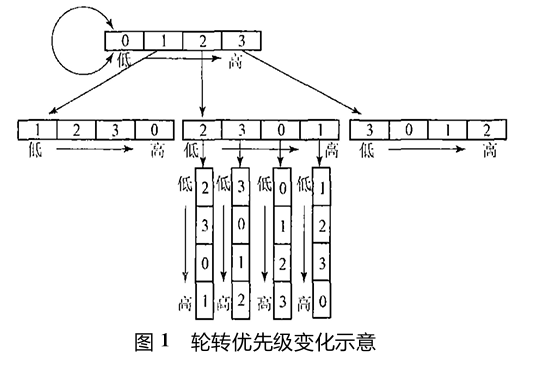

轮转优先级是在固定优先级基础上优先级循环移动,当前占有总线的主设备在下一次总线申请中有最低的优先级随后的高序号主设备享有最高优先级。如图,保持优先级轮转顺序不变,当某一主设备获得响应,比它优先级高的主设备和它同时降低优先级。4个主设备的优先级轮转排序顺序组合只有4种。

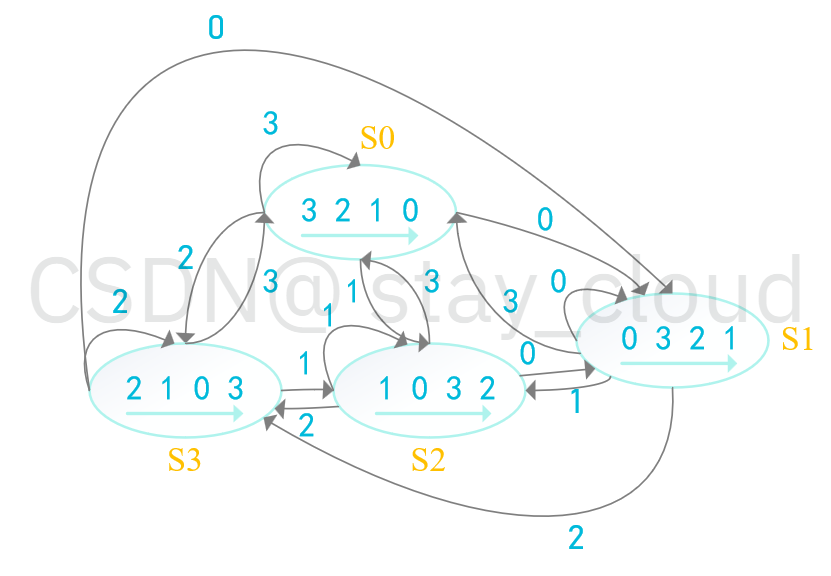

我们可以使用有限状态机来完成设计。由于只有四种排列组合,因此只需四个状态,我们可以画出状态转换图:

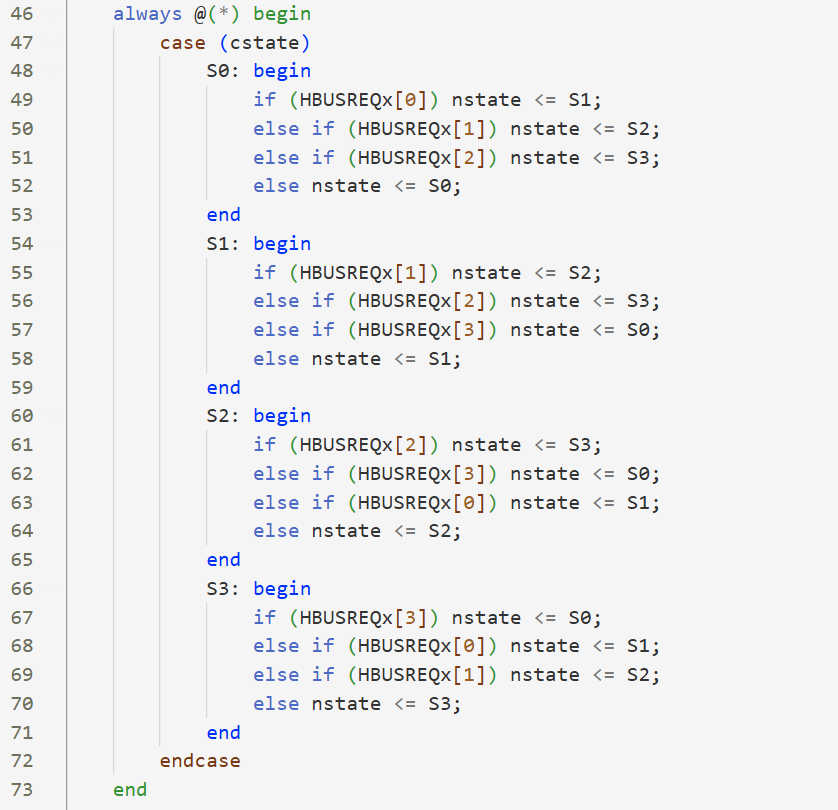

弧线上数字表示发出请求的主机号,当多个主机同时发出请求时,响应优先级最高的那个。S0为初始状态,3号主机优先级最低,0号主机优先级最高。

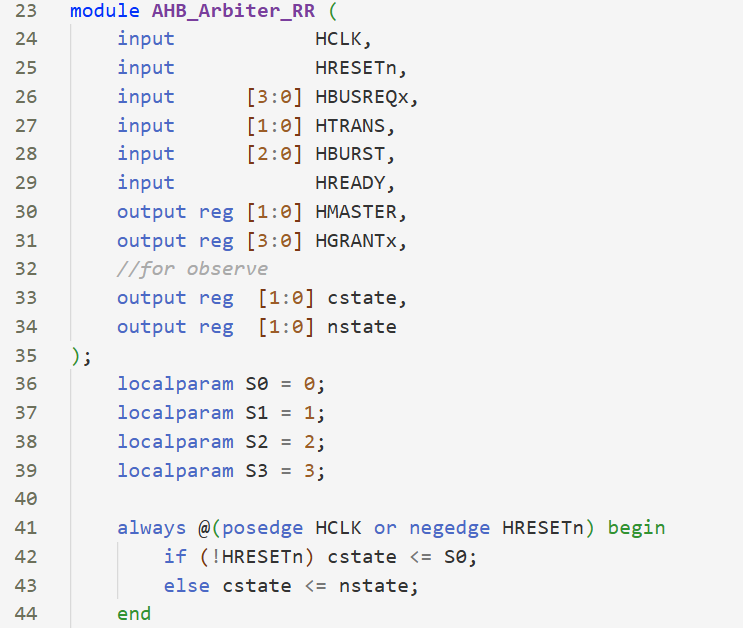

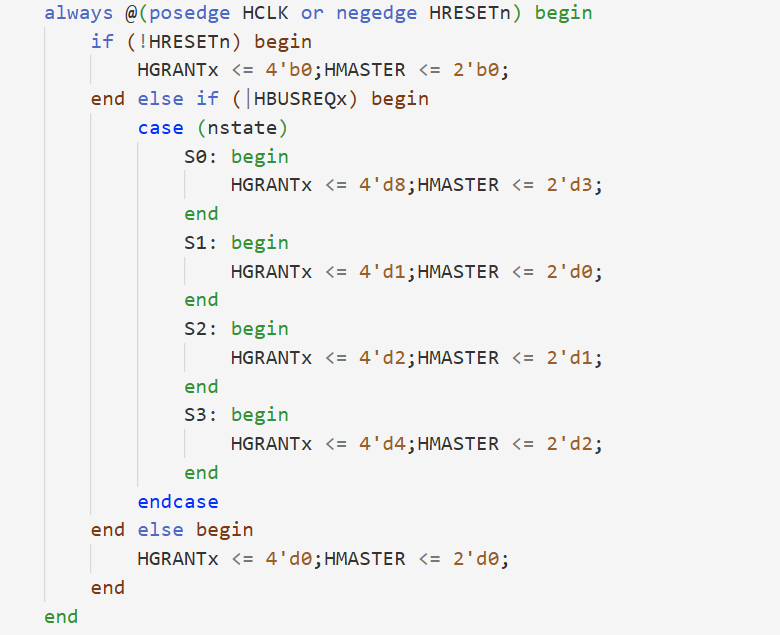

三段式状态机代码如下,为了仿真时便于观测状态变化,将cstate和nstate作为输出信号。

使用if-else语法完成优先级仲裁:

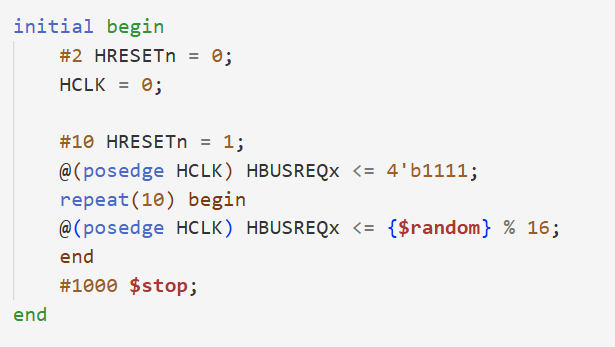

给出随机数激励 :

仿真结果如下图所示 ,总线授予信号和主机号均在发出总线请求后的下一个周期给出:

下表为对部分激励与响应的说明:

大家可以自己设计激励,观察nstate等信号,验证设计的正确性,也可以将4位主机扩展为8位、16位等,画出状态转换图,之后的设计方法相同。

本实验还可以参考文章【AHB接口协议】固定优先级和轮询仲裁器的Verilog实现 - Toy模板网,提供了轮转优先级实现的其他方法。

2682

2682

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?