文章目录

摘要

文章为学习记录。以配置Native接口、双时钟FIFO为例,介绍FIFO IP 核配置过程中选项卡的各个参数。

一、FIFO IP 核简介

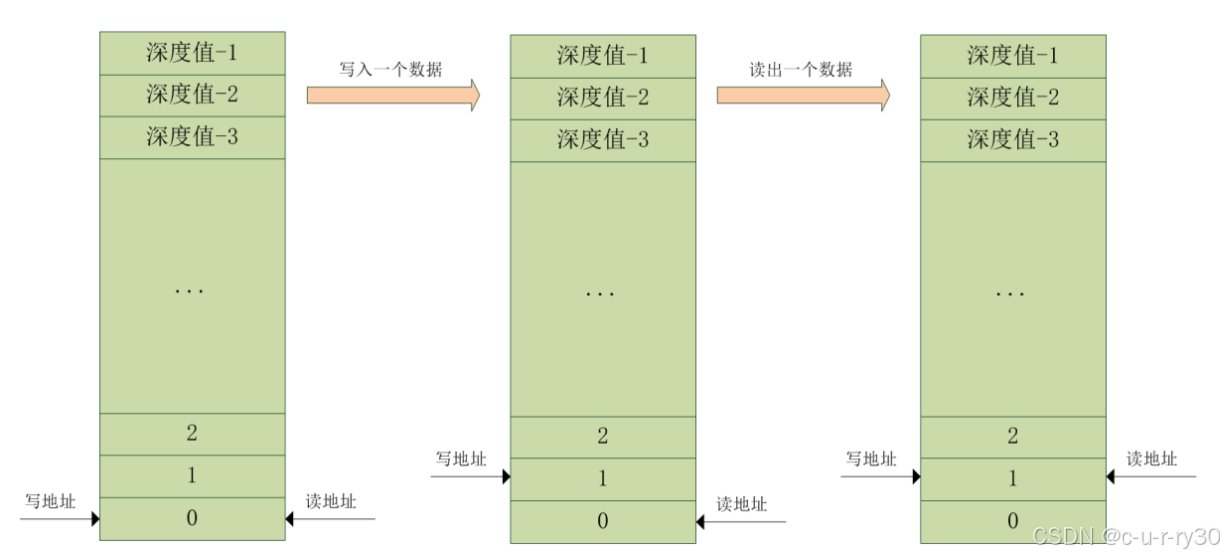

FIFO(First In First Out),即先进先出。

应用于数据的缓存、数据位宽转换、跨时钟域数据处理。

它与普通存储器的区别是没有外部读写地址线,使用起来相对简单。缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加 1 完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

二、FIFO IP 核生成与配置

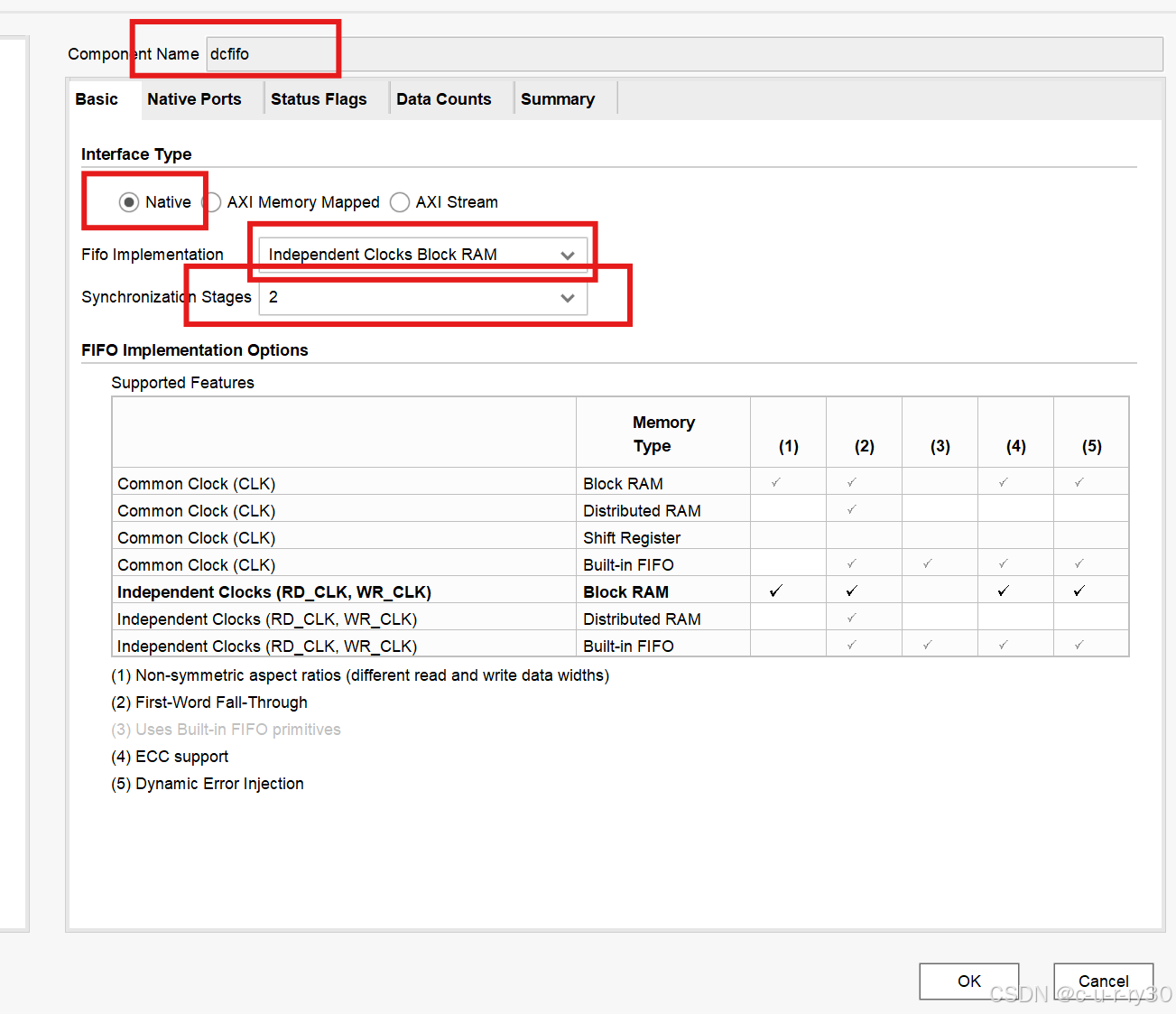

1.Basic Tab

Interface Type

FIFO Implementation:单时钟 FIFO:读写共用一个时钟。双时钟:写相关的信号同步于写时钟 wr_clk,读相关的信号同步于读时钟 rd_clk 。

Synchronization stages:跨时钟域逻辑的同步器阶数。

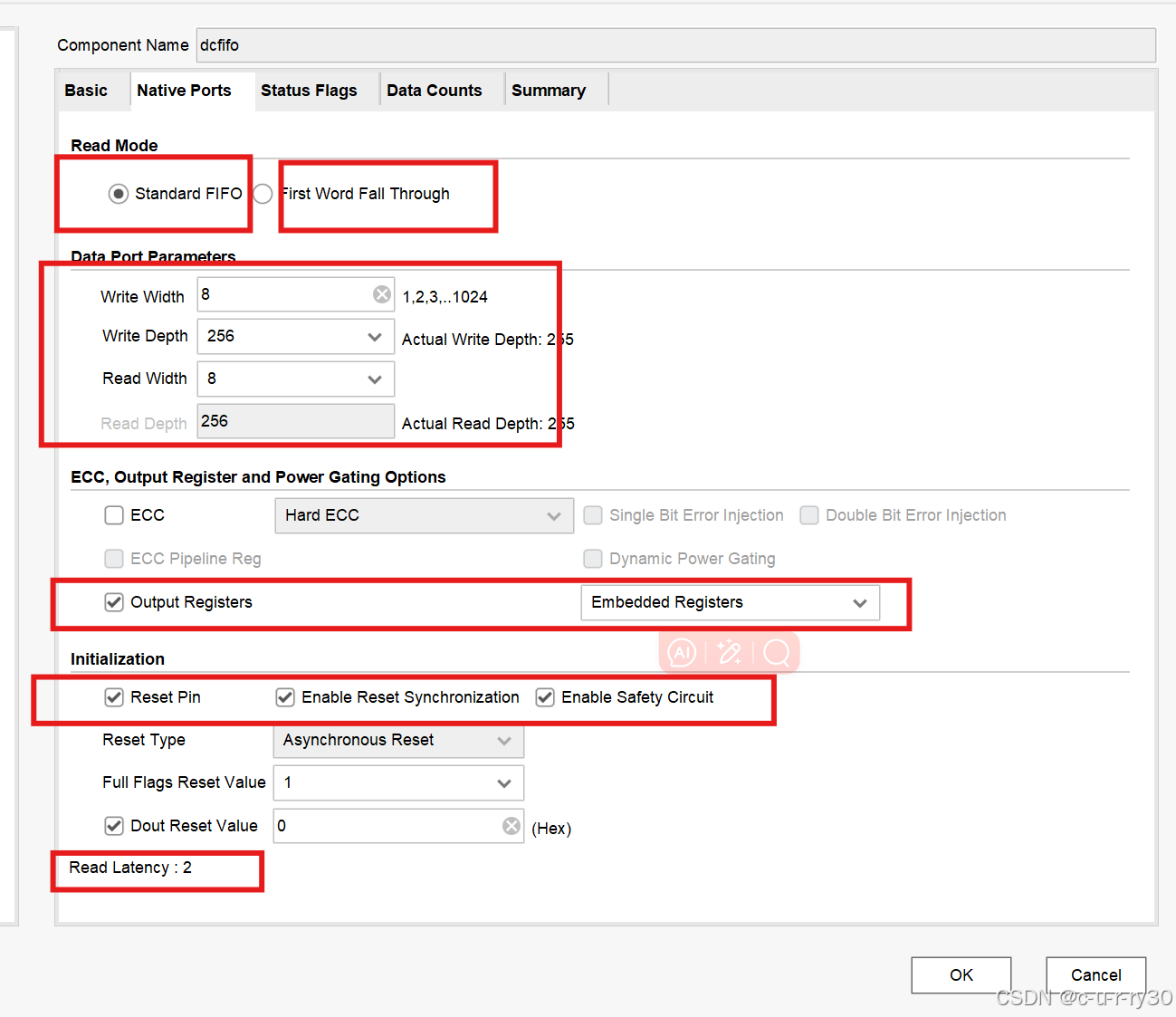

2.Native Ports Tab

Read

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8751

8751

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?