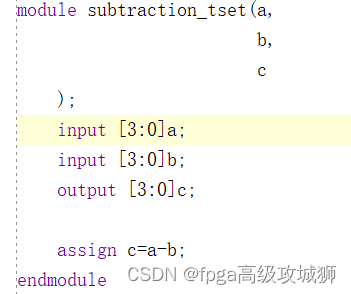

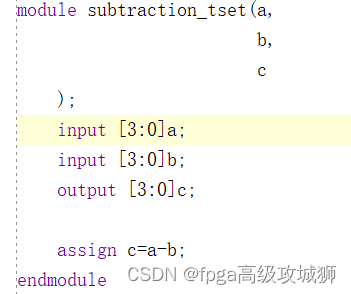

源代码:

testbench:

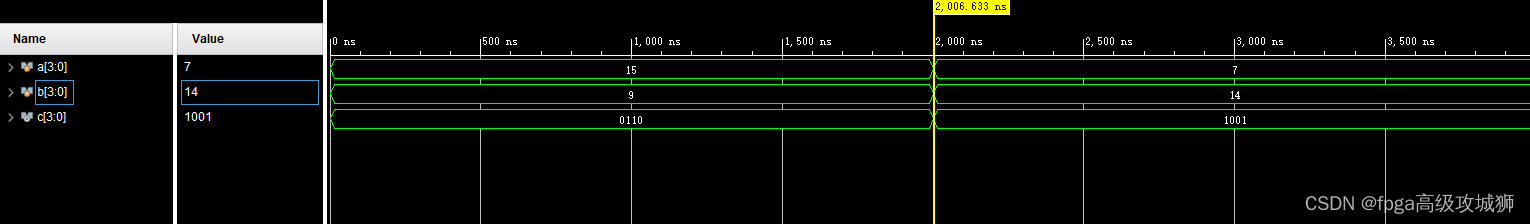

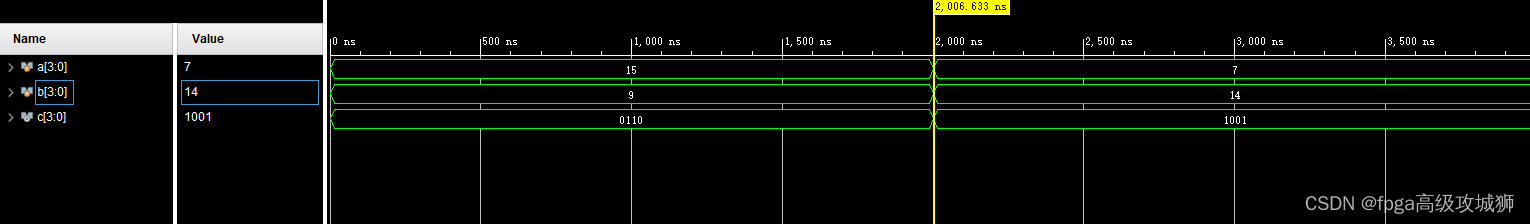

结果:

总结:

在fpga中实现两数相减,若是正数,相减之后的是二进制补码(但正数的补码和原码相同)

若是负数。相减之后的是二进制补码

只判断两个数相减结果的正负: 1、定义一个相减结果寄存器

2、判断结果寄存器的最高位是0或者1即可

源代码:

testbench:

结果:

总结:

在fpga中实现两数相减,若是正数,相减之后的是二进制补码(但正数的补码和原码相同)

若是负数。相减之后的是二进制补码

只判断两个数相减结果的正负: 1、定义一个相减结果寄存器

2、判断结果寄存器的最高位是0或者1即可

954

954

745

745

3490

3490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?