推荐一篇非常好的文章:

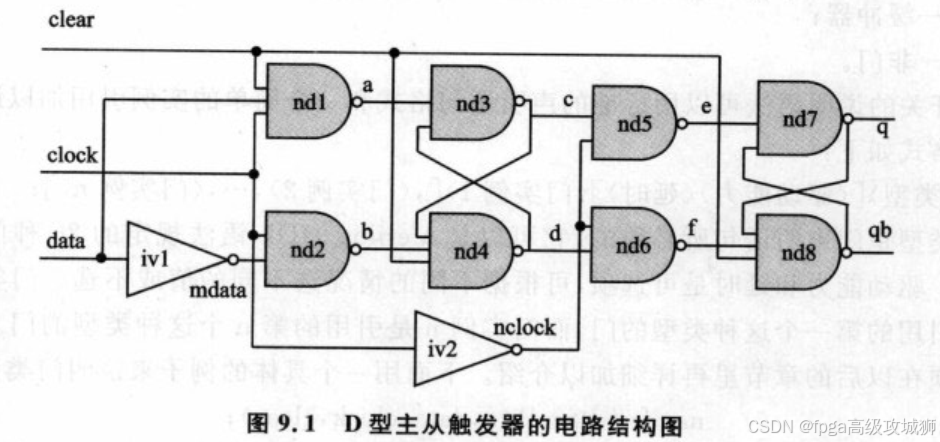

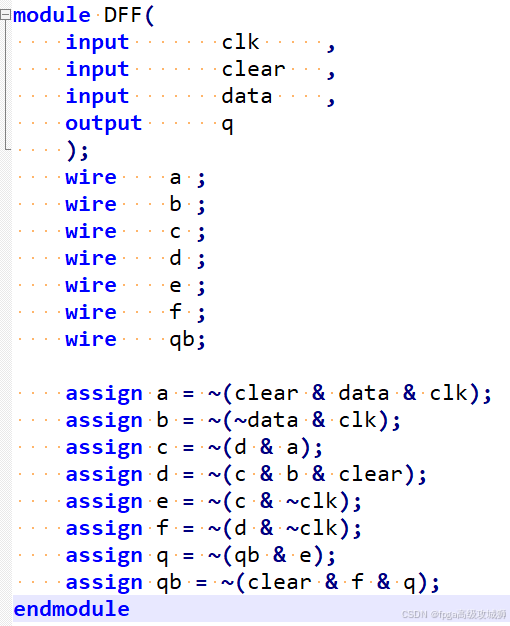

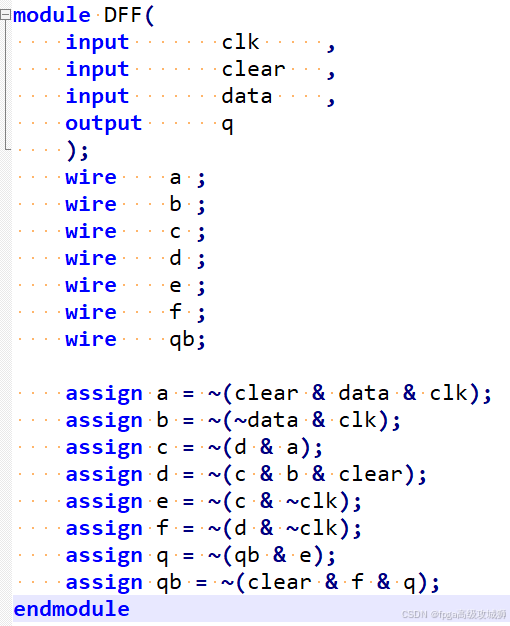

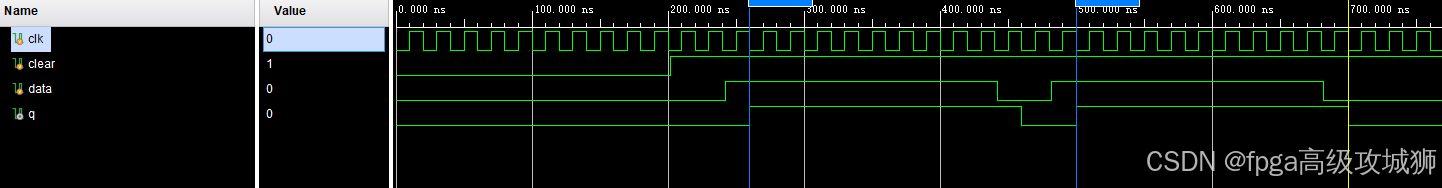

上图中,nd1、nd2、nd3、nd4是一个RS锁存器,nd5、nd6、nd7、nd8是一个RS锁存器

前边的锁存器:

clock为1的时候,输入信号有效

当data=1时,c=1

clock=0,即nclock=1时,后边的锁存器输入有效

c=1时,q=1

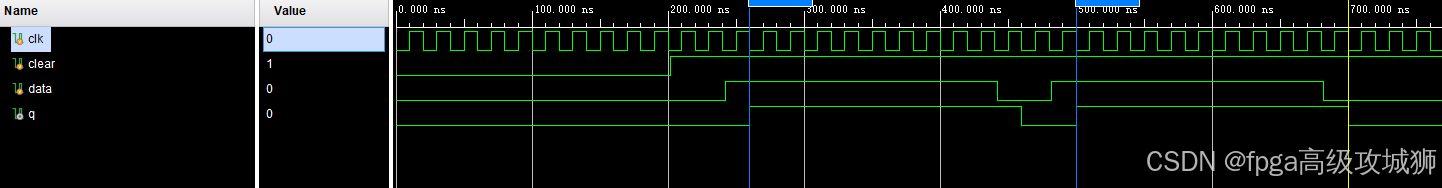

这样两个串联的锁存器就可以组成DFF,这是一个低电平复位,下降沿采样的DFF

推荐一篇非常好的文章:

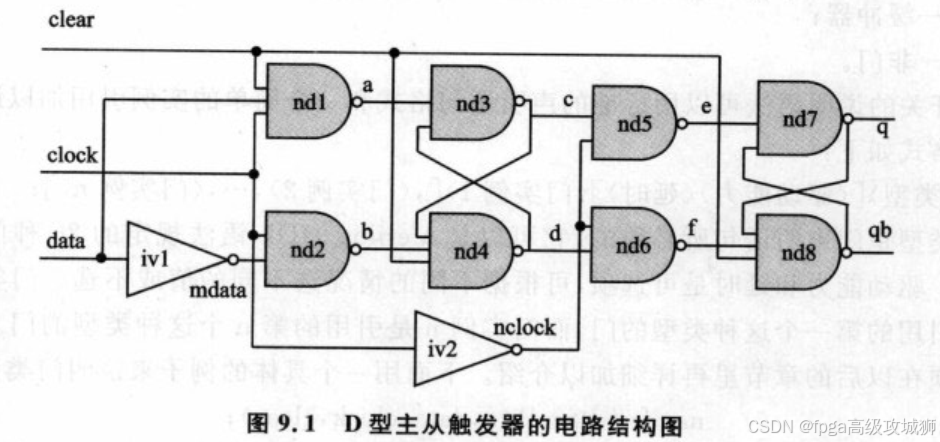

上图中,nd1、nd2、nd3、nd4是一个RS锁存器,nd5、nd6、nd7、nd8是一个RS锁存器

前边的锁存器:

clock为1的时候,输入信号有效

当data=1时,c=1

clock=0,即nclock=1时,后边的锁存器输入有效

c=1时,q=1

这样两个串联的锁存器就可以组成DFF,这是一个低电平复位,下降沿采样的DFF

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?