一、说明

实现平台:vivado2018.3

实验设备:领航者V2(ZYNQ7020),示波器一台

二、原理

在大多数实验项目中,所需要的时钟频率不尽相同,因此需要根据需求产生特定的时钟频率。

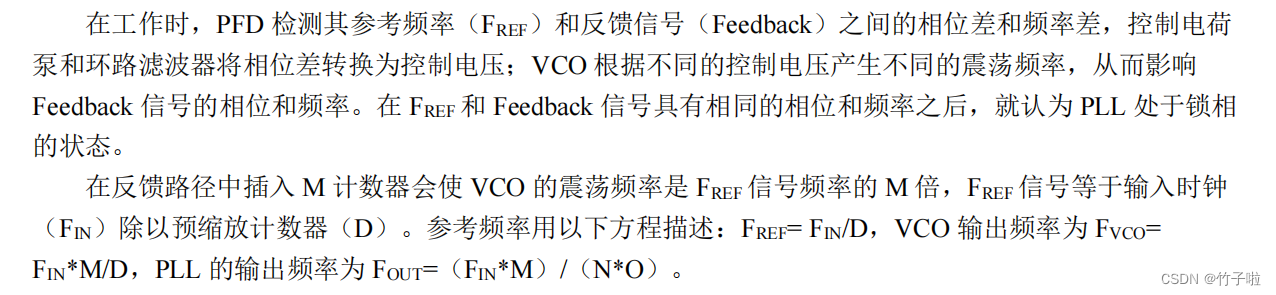

PLL(Phase Locked loop),锁相环,是一种反馈控制电路。对时钟网络进行系统级的时钟管理和偏移控制,又有时钟倍频、分频、相位偏移和可编程占空比的功能。使用锁相环即可产生我们所需的特定时钟频率。

PLL组成部分:

-

前置分频计数器(D计数器)

-

相位-频率检测器(PFD,Phase-Frequency Detector)电路

-

电荷泵(Charge Pump)

-

环路滤波器(Loop Filter)

-

压控振荡器(VCO,Voltage Controlled Oscillator)

-

反馈乘法器计数器(M计数器)

-

后置分频计数器(O1-O6计数器)

在FPGA中产生锁相环无外乎两种方式:手写锁相环代码和调用IP核。实际使用中调用IP核即可:)。

在FPGA中产生锁相环无外乎两种方式:手写锁相环代码和调用IP核。实际使用中调用IP核即可:)。

三、内容

1. 调用Clocking_Wizard IP核,输出4个不同时钟频率或相位的时钟;

2. 产生4个时钟 100MHZ,100MHZ+相位180度,50MHZ以及25MHZ,连接到开发板上4个扩展IO上;

3. 在Vivado中进行仿真以验证结果;

4. 生成比特流文件并将其下载到开发板上,使用示波器来测量时钟频率以验证结果。

四、步骤

1.新建空白工程,添加PLL IP核。在 Vivado 软件的左侧 “Flow Navigator”栏中单击“IP Catalog”,“IP Catalog”按钮以及单击后弹出的“IP Catalog”窗口,在该窗口中搜索Clocking Wizard,结果如下图所示。

2.配置PLL IP核。首先双击“Clocking Wizard”,弹出“Customize IP”窗口界面,如下图所示:

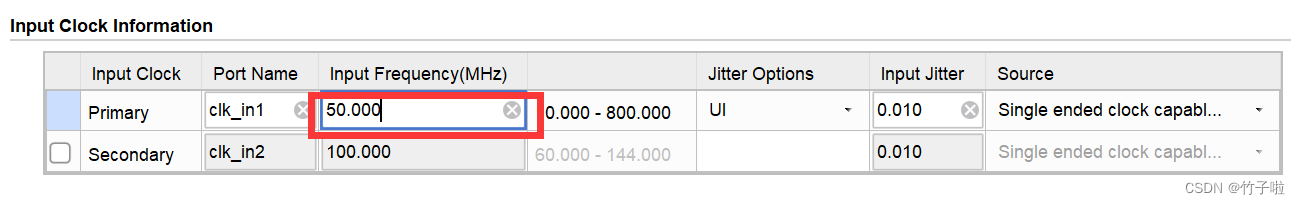

在“Primitive”选项中选择MMCM或PLL均可,MMCM的功能是PLL的超集,其功能相较于PLL更强,此处选择默认的MMCM即可。在下方的“Input Clock Information”中,将“Primary”时钟的输入频率设置为开发板上的时频频率,此处设置为50MHZ,其他设置保持默认即可。

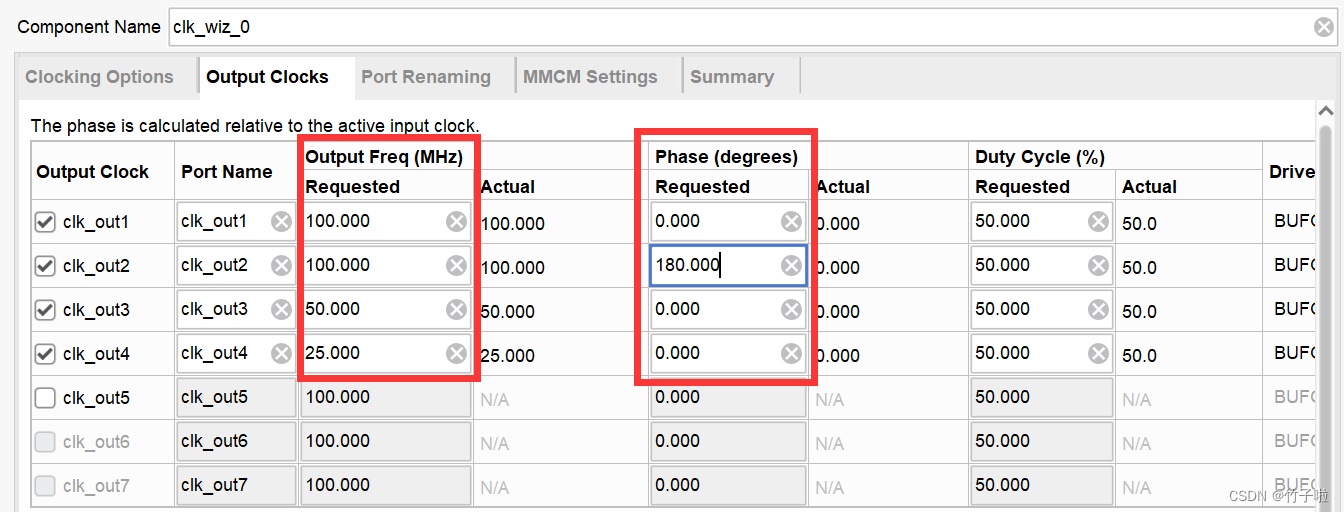

3. 输出4个时钟。在IP核界面上方选择“Output Clocks”选项卡,勾选前四个时钟,并分别设置时钟频率为100、100、50和25,其中第二个100MHZ时钟的相移设置为180,,产生我们所需输出的4个时钟,如下图所示。

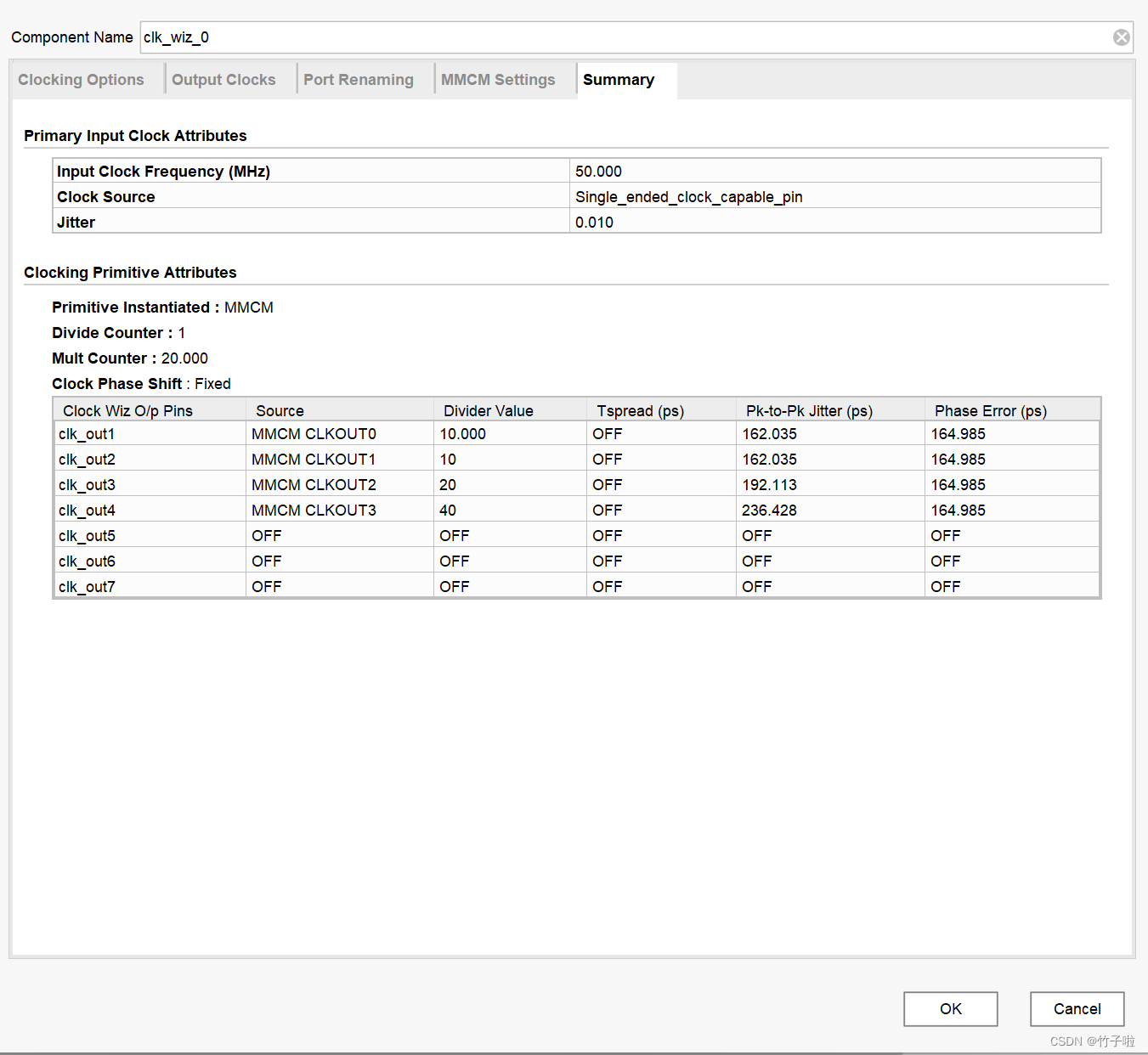

其他设置默认即可,最后可查看“Summary”选项卡,看是否设置正确,如下图所示。

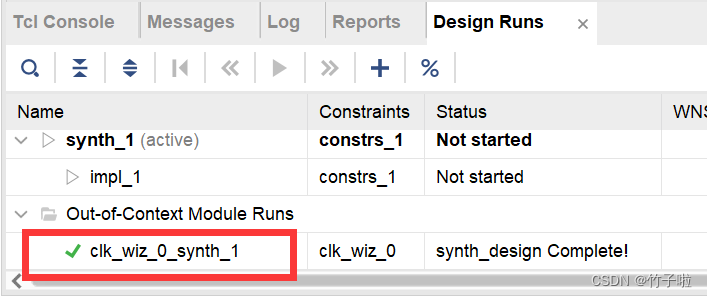

4. 综合IP核。配置完成后,接着选择OK,产生IP核,等待综合完成即可。在Vivado界面下方的Design Runs可以看到红框部分,ip核名称前出现红勾即表示综合完成,如下图所示。

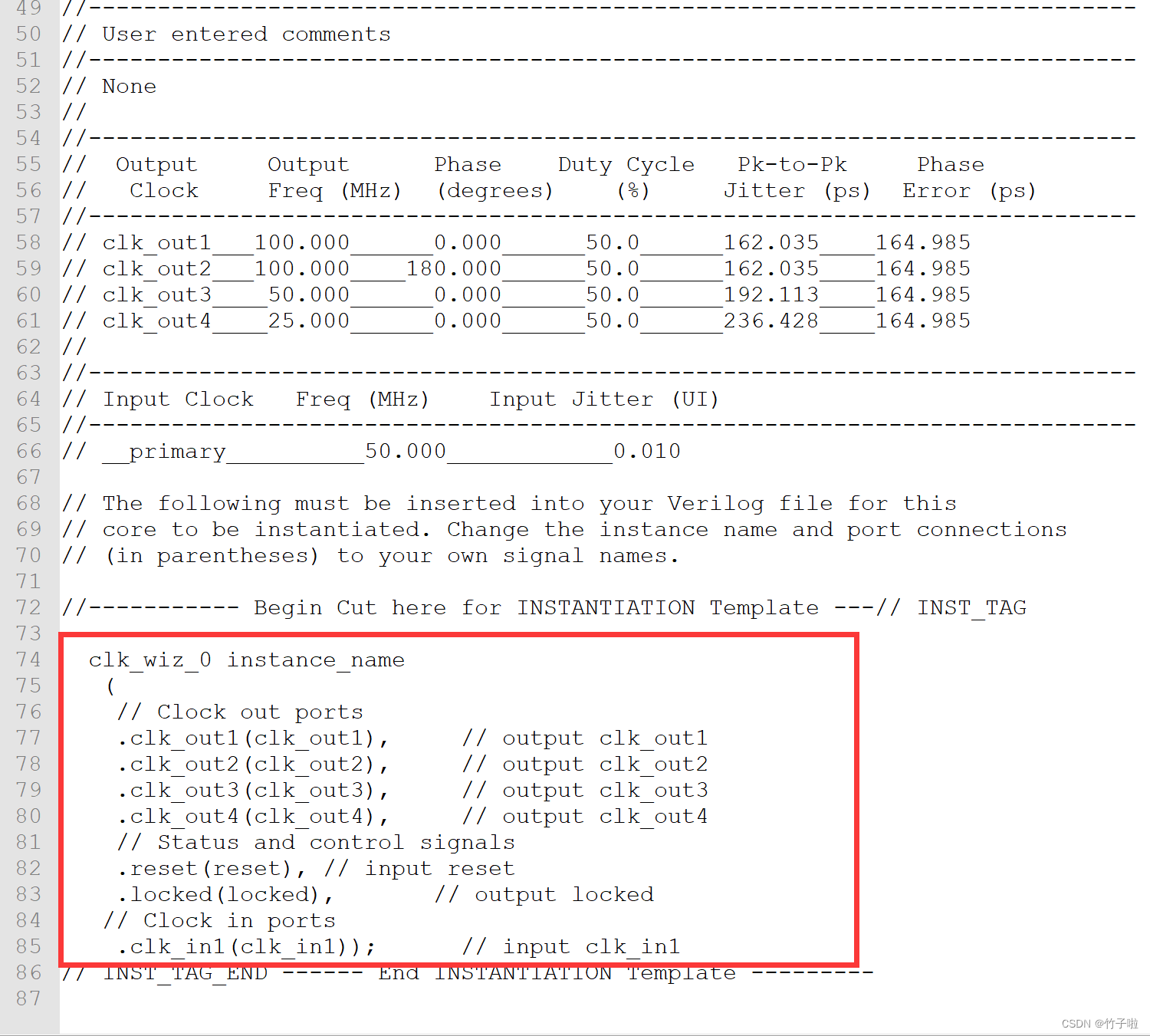

5. IP核例化模板。想要调用例化IP核,查看“Source”窗口中的“IP Source”选项卡中,找到“Instantiation Template”中的“clk_wiz.vio”,如下图所示。

打开“clk_wiz.vio”,找到例化代码复制即可,如下图所示。

五、程序编写

1.主程序代码编写:

module ip_clk_wiz(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位,低电平有效

//输出时钟

output clk_100m, //100Mhz时钟频率

output clk_100m_180dge,//100Mhz时钟频率,相位偏移180度

output clk_50m, //50Mhz时钟频率

output clk_25m //25Mhz时钟频率

);

wire locked;

//例化PLL

clk_wiz_0 u_clk_wiz_0

(

// Clock out ports

.clk_out1 (clk_100m ), // output clk_out1

.clk_out2 (clk_100m_180dge), // output clk_out2

.clk_out3 (clk_50m ), // output clk_out3

.clk_out4 (clk_25m ), // output clk_out4

// Status and control signals

.reset (~sys_rst_n ), // input reset IP核默认高电平

.locked (locked ), // output locked

// Clock in ports

.clk_in1 (sys_clk ) // input clk_in1

);

endmodule2.TestBench仿真测试代码程序编写:

module tb_ip_clk_wiz();

reg sys_clk;

reg sys_rst_n;

wire clk_100m;

wire clk_100m_180dge;

wire clk_50m;

wire clk_25m;

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200

sys_rst_n = 1'b1;

#2000

$stop;

end

//例化

ip_clk_wiz u_ip_clk_wiz(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.clk_100m (clk_100m),

.clk_100m_180dge(clk_100m_180dge),

.clk_50m (clk_50m),

.clk_25m (clk_25m)

);

always #10 sys_clk = ~sys_clk;

endmodule六、仿真结果

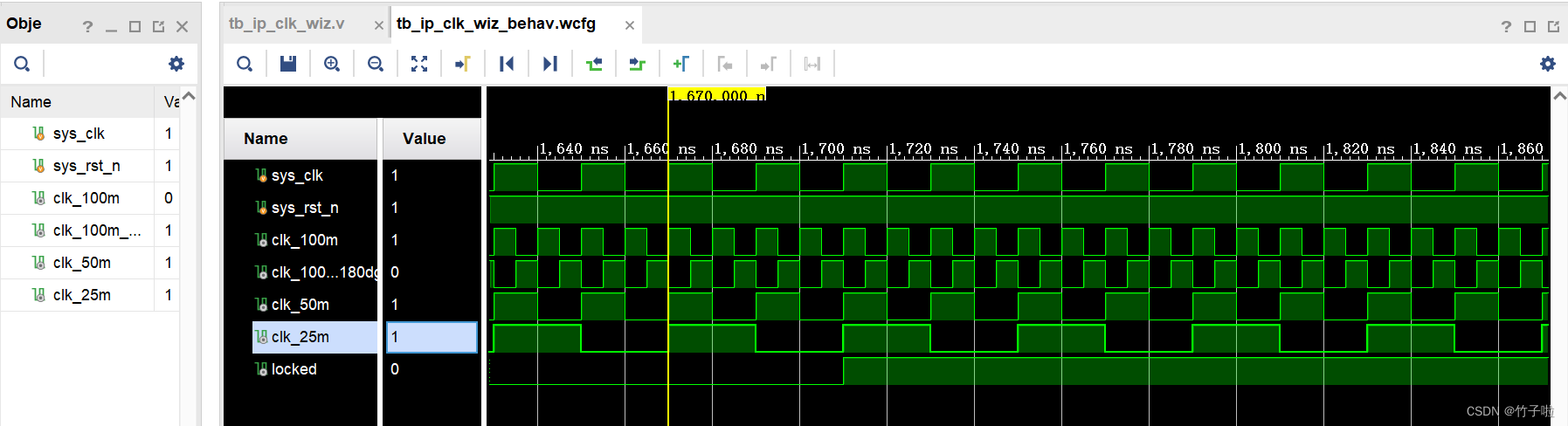

如图所示,clk_100m一个周期所用时间是10ns,即100MHZ的时钟频率;可以看到clk_100m_180dge的波形和clk_100m的波形相同,但时钟相位刚好相反,即相位偏移了180度;同理,clk_50m和clk_25m一个周期所用的时间分别为20ns和40ns,即50MHZ和25MHZ的时钟频率,仿真验证正确。

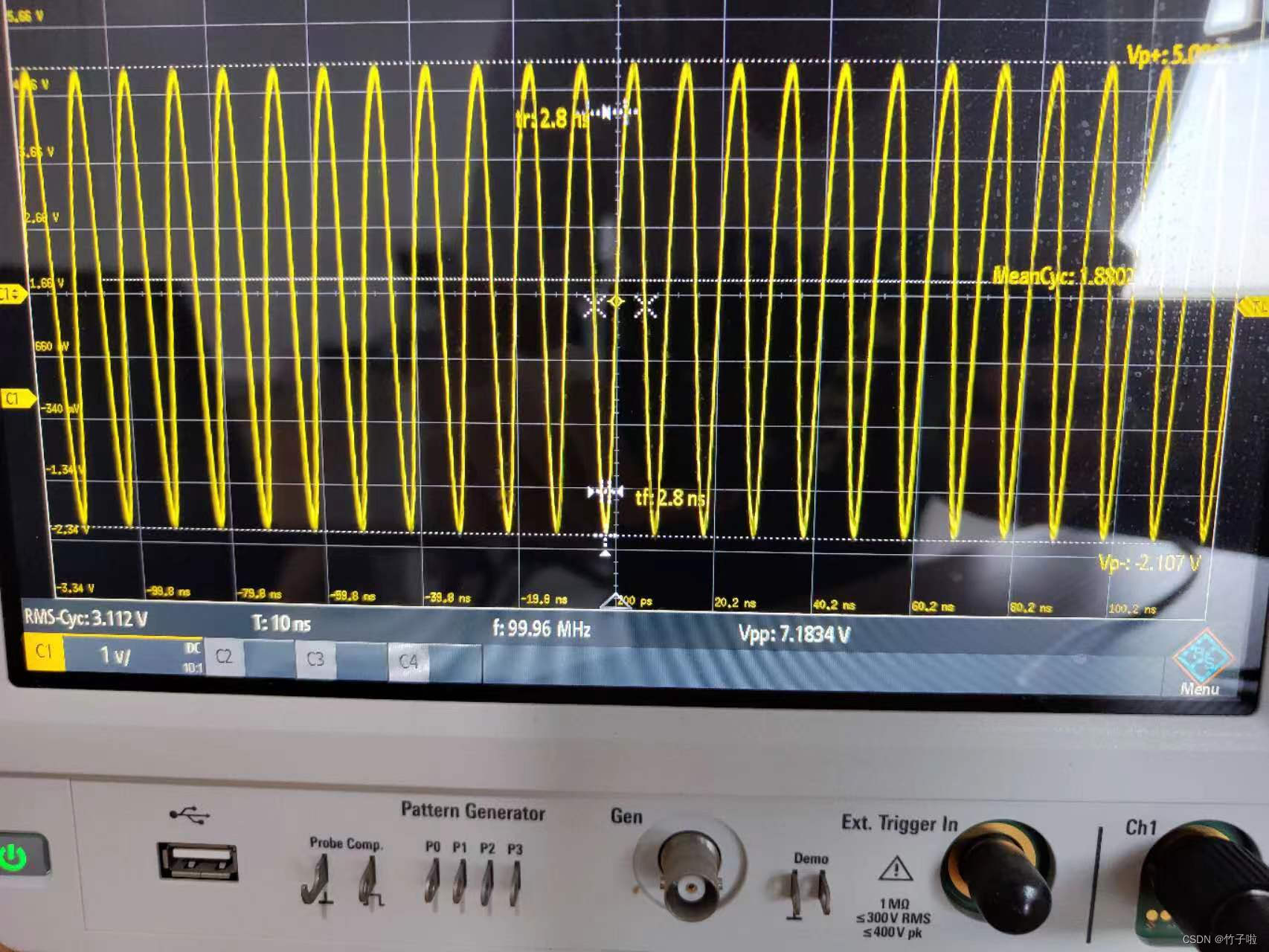

七、上板验证结果

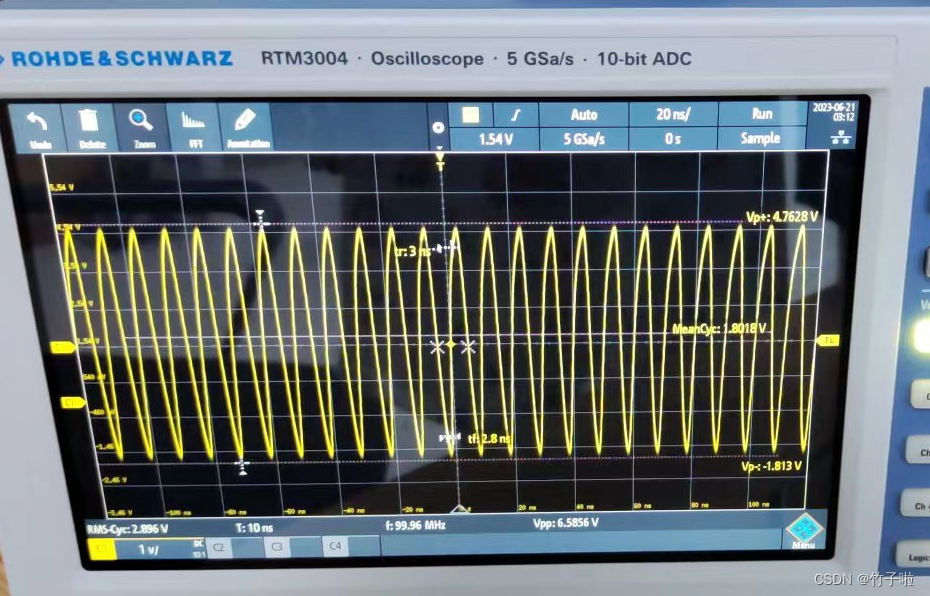

编译工程生成比特流文件后,下载到开发板上。使用示波器探针测量开发板对应管脚,观察对应波形。如下图所示为clk_100m管脚测得的波形,可以看到时钟频率为100MHZ。

其他时钟的频率如下所示:

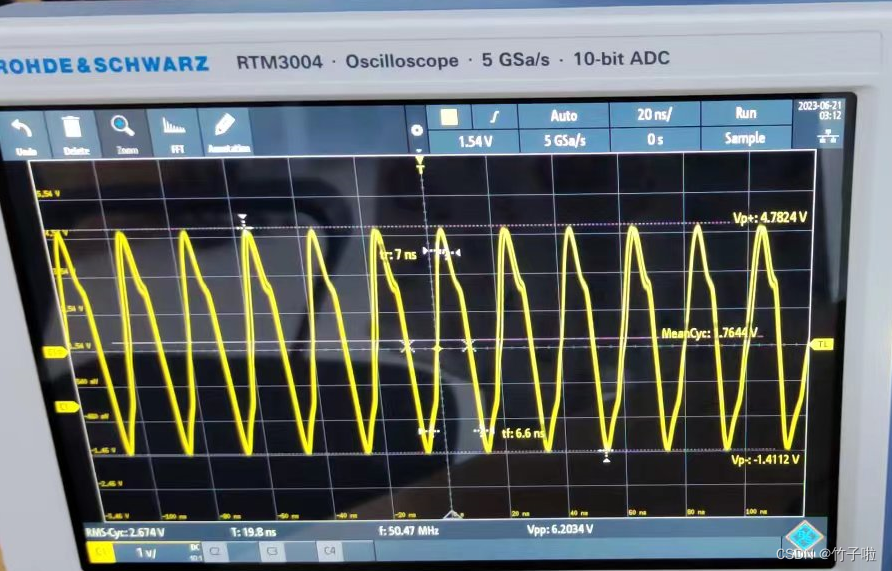

clk_100m_180dge:

clk_50m

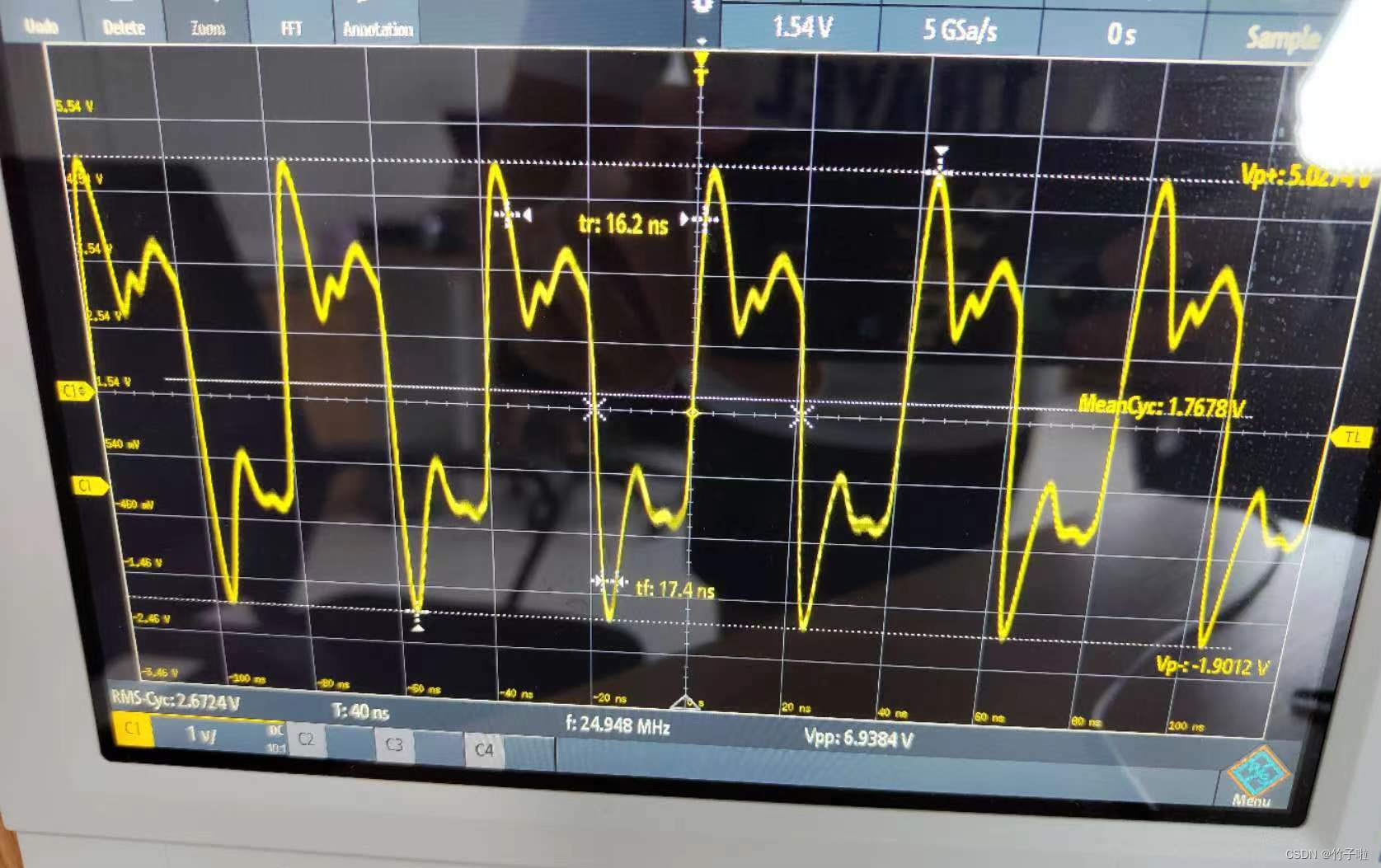

clk_25m

时钟频率均符合预期,上板测试验证正确。

本文详细介绍了如何在Vivado2018.3环境下,利用ClockingWizardIP核为ZYNQ7020FPGA配置和产生100MHz、100MHz+180度相位差、50MHz和25MHz四种不同频率的时钟。通过设置IP核参数、编写Verilog代码、仿真验证及最终上板测试,确保时钟信号的正确性。

本文详细介绍了如何在Vivado2018.3环境下,利用ClockingWizardIP核为ZYNQ7020FPGA配置和产生100MHz、100MHz+180度相位差、50MHz和25MHz四种不同频率的时钟。通过设置IP核参数、编写Verilog代码、仿真验证及最终上板测试,确保时钟信号的正确性。

664

664

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?