这一节我们介绍 Design Compiler 进行优化的三个阶段:结构级、逻辑级以及门级,在 不同的阶段,DC 运用的方法和优化余地是不一样的,通过这一节的学习,你将对这几个阶段的特点和优化方法有一个比较清楚的了解,其中有一些方法我们在前面的章节中已经提及 过,这里一起归纳一下,希望能加深大家的认识。

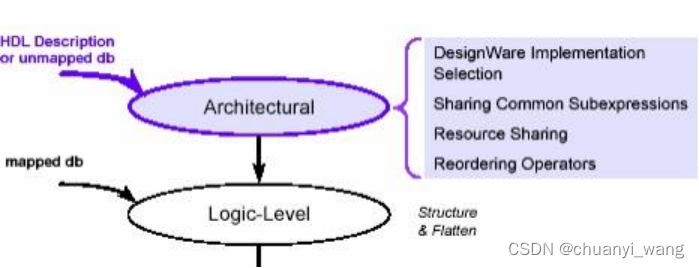

上图是这三个阶段的关系图,可以看到,结构级属于最高的抽象层次,当读入 Verilog 代码或者没有经过映射的 db 文件后,DC 的优化从这个阶段层次开始,可以说,结构级是 优化的最高层次 ,所以对 DC 来说 ,这个层次的综合可以称为高层次综合(High-Level Synthesis) 。结构层的下一个优化阶段是逻辑级阶段,也是读入映射过的 db 文件的 DC 的初始优化阶段。再往下一个阶段是门级阶段,也是优化的最后阶段,这里所要作的工作主要就 是 GTECH 到工艺库的映射。

文章目录

7.1 结构级优化

因为结构级是优化过程中层次最高的一级,因此它也是 DC 可以采用的优化方法最多的一级,它的主要优化方法如下图所示——

1. DesignWare 选择

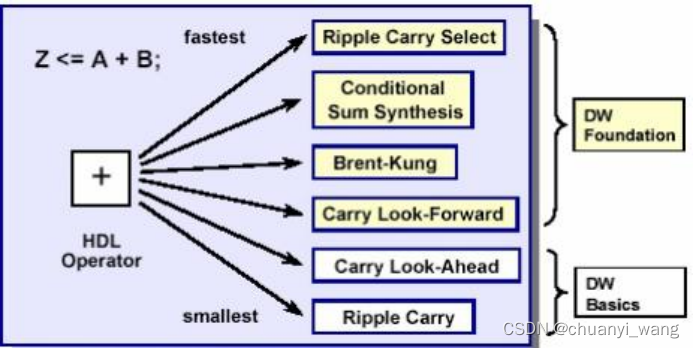

DW 选择是结构级优化的一个很主要的特点,在这个阶段 DC 能够根据设计者施加 的时序或者面积的约束在DW 的不同实现方式中找到它认为最佳的实现方案。比如加法 器的实现方式一共有如下几种——

其中DW Foundation 需要有专门的 license ,而且使用之前还要设置综合库(synthetic library)。

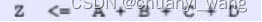

2. 共享子表达式(Sub-Expressions)

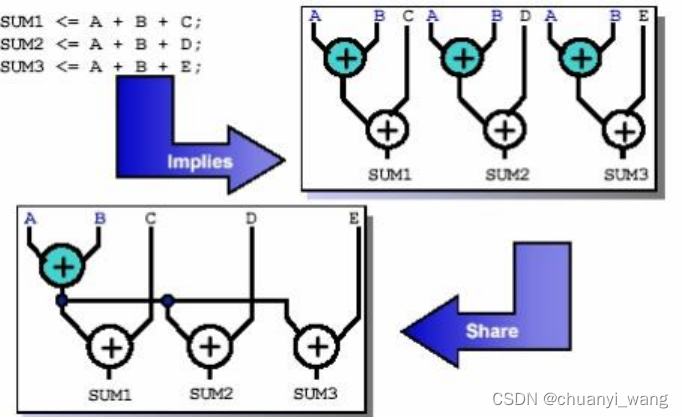

这里的子表达式主要是指数学表达式,比如下面这个例子,如果按照原来的语句综合,会包含 6 各加法器,但是如果表达式之间的公共项提取出来,便可以大大的减小面 积,如下图——

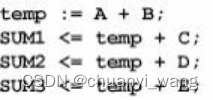

如果要直接综合出共享后的电路,可以在编写 RTL 代码的时候强制指定共享项——

3. 资源共享(Resource Sharing)

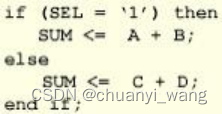

资源共享的原理与共享子表达式类似,只不过这里指的所谓资源是一些 HDL 的运 算符和表达式, 比如加(+) 、减(-) 、乘(*) 、除(/)以及大于(>) 、大于等于(>=) 、小于(<) 、 小于等于(<=) 。这里举的例子,在前面的章节里也见过,比如给定一个语句——

它可能有下面两种电路实现——

DC 会根据具体的约束条件综合出最符合要求的结构来。

4. 运算符排序(Operator Reordering)

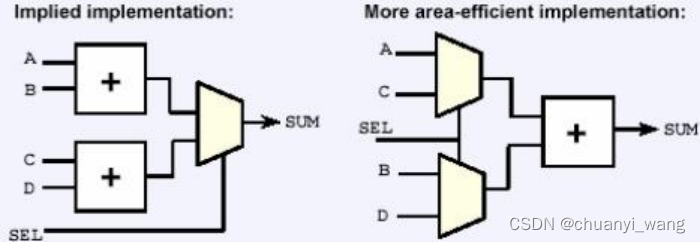

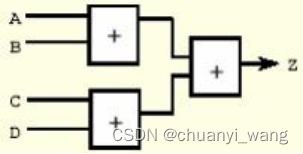

对于下面这个表达式 (输出 Z 是施加了一定时序约束),

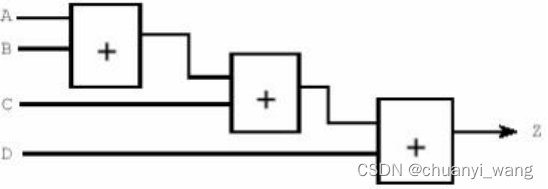

DC 最初是按照从左至右的顺序计算的,也就是说它最初的排序如下——

如果几个输入信号到达的时间相同,DC 会通过运算符排序优化成下图的平衡的结构,减小延时——

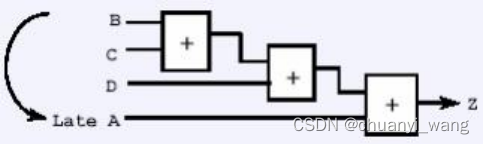

如果A 信号较迟到达,则综合出的电路结构会如下——

7.2 逻辑级优化

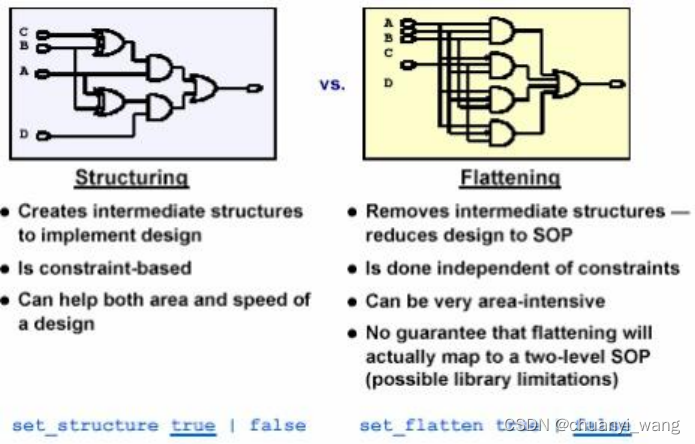

在经过结构级优化之后,电路被转化成了工艺无关的 GTECH 库的形式,这级也称为逻 辑级,对于逻辑级优化来说,只有一个方法,那就是—— 结构化 (structure)或者扁平化 (flatten)。

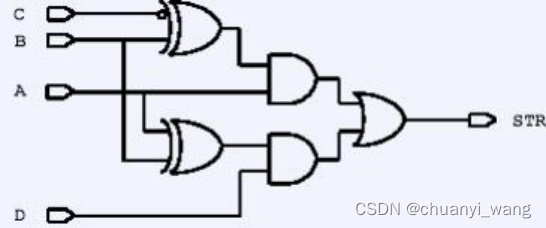

1. 结构化(structure)

结构化是 DC 在逻辑级的默认的优化方法,它是指:使用电路的一些中间项构成一 个多级的电路结构。如下图的电路一共有三级逻辑,下一级的输入是上一级的输出,使 用这种优化方法一般情况下能综合出兼顾时序和面积的电路来。

结构化电路的典型是奇偶校验电路。

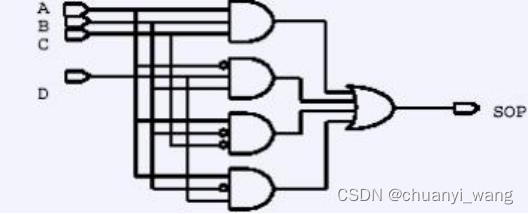

2. 扁平化(flatten)

扁平化是将所有的组合逻辑打平成乘积项和(SOP) 的两级结构① ,类似与可编程阵列 逻辑(PAL) 。使用这种结构的特点由于没有利用中间项,综合后电路面积将会变得很大, 但是却不一定能取得较好的时序。

扁平化结构的电路和设置扁平化的 DC 命令如下所示——

综合结构化和扁平化的特点,可以归纳如下——

由于 DC 默认是用结构化的方式综合逻辑级电路 ,而且这种方式可以得到兼顾时序 和面积的结果,因此我们可以先用这种方式优化。在优化后的电路中找出关键路径,看看关键路径上有没有符合使用 SOP 电路的模块 ,再将这些方便使用 SOP 的模块 set_flatten ,以便取得最佳的效果。

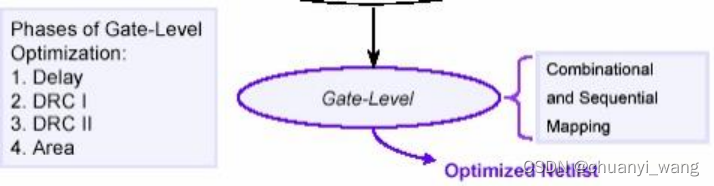

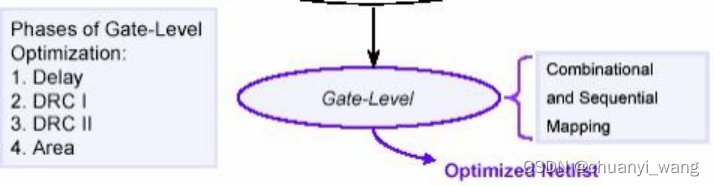

7.3 门级优化

门级优化是优化的最后阶段,它所要完成的任务就是将 GTECH 的电路映射到最终的工 艺库中,并且保证映射后的电路不违反设计规则(Design Rule)。

1. 工艺映射

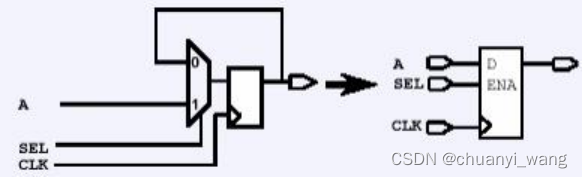

工艺映射包括组合逻辑映射和时序逻辑映射。组合逻辑映射是指 DC 使用工艺库中的各种门替换GTECH 单元,并选择能实现相同逻辑的符合时序及面积要求的单元——

时序逻辑映射的方法和组合逻辑相类似,也是出于速度和面积的考虑,尽量使用复杂的时序单元吸收一部分组合逻辑。

2. 设计规则检查(DRC)

对于工艺库的单元而言,Foundry 都指定了每个单元的工作条件的限制,比如最大 电容(max_capacitance)等等,这些限制也可以称为设计规则(Design Rule) ,在设计规则限 定的范围内,Foundry 提供的参数才有实际的意义。比如一个单元允许的最大电容为 5pf,而 实际工作电路中出现的电容值为 10pf,那么这时,便违反了设计规则,单元的参数也就 不能确保是准确的了。

因此,DC 在作门级优化的时候,在映射的过程中也会检查电路的设计规则,一般 的做法是在单元中插入 buffer 增加驱动能力,或者将小驱动的单元替换为大单元。设计 规则检查分为两个过程——DRC I 和 DRC II 。

DRC I 是指 Design Compiler 在不影响电路的时序和面积的前提下修正违反规则的 一些单元,如果在这个前提下不能完全修正,则要进行下一步的检查,即 DRC II ,这一 步的修正必然是以牺牲一部分时序和面积为代价的。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?