一、DC综合简介

1.1 什么是综合?

概括地说:综合就是把行为级的RTL代码在工艺、面积、时序等约束下转换成对应的门级网表。

综合是使用软件的方法来设计硬件,然后将门级电路实现与优化的工作留给综合工具的一种设计方法。它是根据一个系统逻辑功能与性能的要求,在一个包含众多结构、功能、性能均已知的逻辑元件的单元库的支持下,寻找出一个逻辑网络结构的最佳实现方案。即实现在满足设计电路的功能、速度及面积等限制条件下,将行为级描述转化为指定的技术库中单元电路的连接。

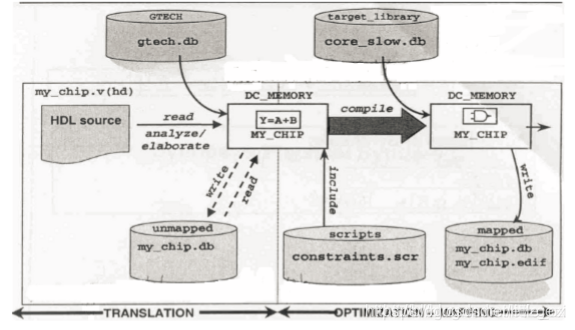

综合主要包括三个阶段:转换(translation)、优化 (optimization)与映射(mapping)。

- 转换阶段综合工具将高层语言描述的电路用门级的逻辑来实现,对于 Synopsys 的综合工具 DC 来说,就是使用 gtech.db1库

中的门级单元来组成 HDL 语言描述的电路,从而构成初始的未优化的电路。 - 优化与映射是综合工具对已有的初始电路进行分析,去掉电路中的冗余单元,并对不满足限制条件的路径进行优化,然后将优化之后的电路映射到由制造商提供的工艺库上。

常用的工具:

Synopsys: DC(用的较多)

Candance:Genus

1.2 综合需要的文件

- RTL文件;

- 标准单元的库文件;

- 其他库文件。如IO库P库等等(不一定有)

1.3综合输出的文件

- 综合后的门级网表;

- 带时序约束信息的sdc文件:

- 其他一些后端需要用的特殊配置,如dont_touch设置等;

- 保留综合结果的ddc文件(之后可以直接load这个文件,查看综合结果);

1.4 电路综合的要求

1.4.1 综合脚本的要求

综合脚本必须是可重用的。脚本的可重用主要有两方面的含义:

- 在 整个电路设计过程中,当后端工具提取出线负载模型后作综合或者在布局布线完成之后再做综合,保证添加的限制条件与初始时的综 合是相同的。

- 当系统的一些参数改变时,比如,一个模块从 16 位变为 32 位,而模块的功能没有改变,可以不改变综合的脚本,只需要改变其中的参数就可以实现该目标。即要保证综合脚本是参数化的。

在添加限制条件时,必须对如下的对象施加限制条件:

- 电路中需要有时钟的定义一般情况下,希望综合之后的电路是同步的数字电路(异步电路以及模拟电路需要单独处理),而同步电路中都需要设置时钟或者虚拟时钟。

- 保留时钟网络,不对时钟网络做综合

- 综合的时候需要指定线负载模型,用于估计连线延迟。

- 限制模块中组合路径的输入输出延迟。

- 限制输出的带负载能力(Loading budget)以及输入的驱动单元(driving cell)。

- 模块同步输出的输出延迟(output delay)的限制,以及同步输入延迟(input delay)的限制。

- 多周期路径(multicycle path)以及非法路径(false path)的限制。

- 工作环境的给定。

1.4.2 综合结果的要求

- 综合的结果中没有时序违反(timing violation),即综合的结果必须满足时序性能的要求。

- 综合之后的门级网表必须已经映射到工艺库上。

- 综合之后的门级网表中应避免包含如下电路结构:

在同一个电路中同时含有触发器和锁存器两种电路单元。

在电路中出现有反馈的组合逻辑

用一个触发器的输出作为另外一个触发器的时钟

异步逻辑和模拟电路未单独处理 使用的单元电路没有影射到工艺库中

411

411

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?