verilog简介

Verilog HDL(简称 Verilog )是一种硬件描述语言,用于数字电路的系统设计。可对算法级、门级、开关级等多种抽象设计层次进行建模。

Verilog 继承了 C 语言的多种操作符和结构,与另一种硬件描述语言 VHDL 相比,语法不是很严格,代码更加简洁,更容易上手。

Verilog 不仅定义了语法,还对语法结构都定义了清晰的仿真语义。因此,Verilog 编写的数字模型就能够使用 Verilog 仿真器进行验证。

Verilog HDL可用较少的语句描述较为复杂的电路和灵活的可扩展性,为数字集成电路设计带来了极大的便捷。

FPGA 和 CPLD 是实现这一途径的主流器件。他们直接面向用户,具有极大的灵活性和通用性,实现快捷,测试方便,开发效率高而成本较低。

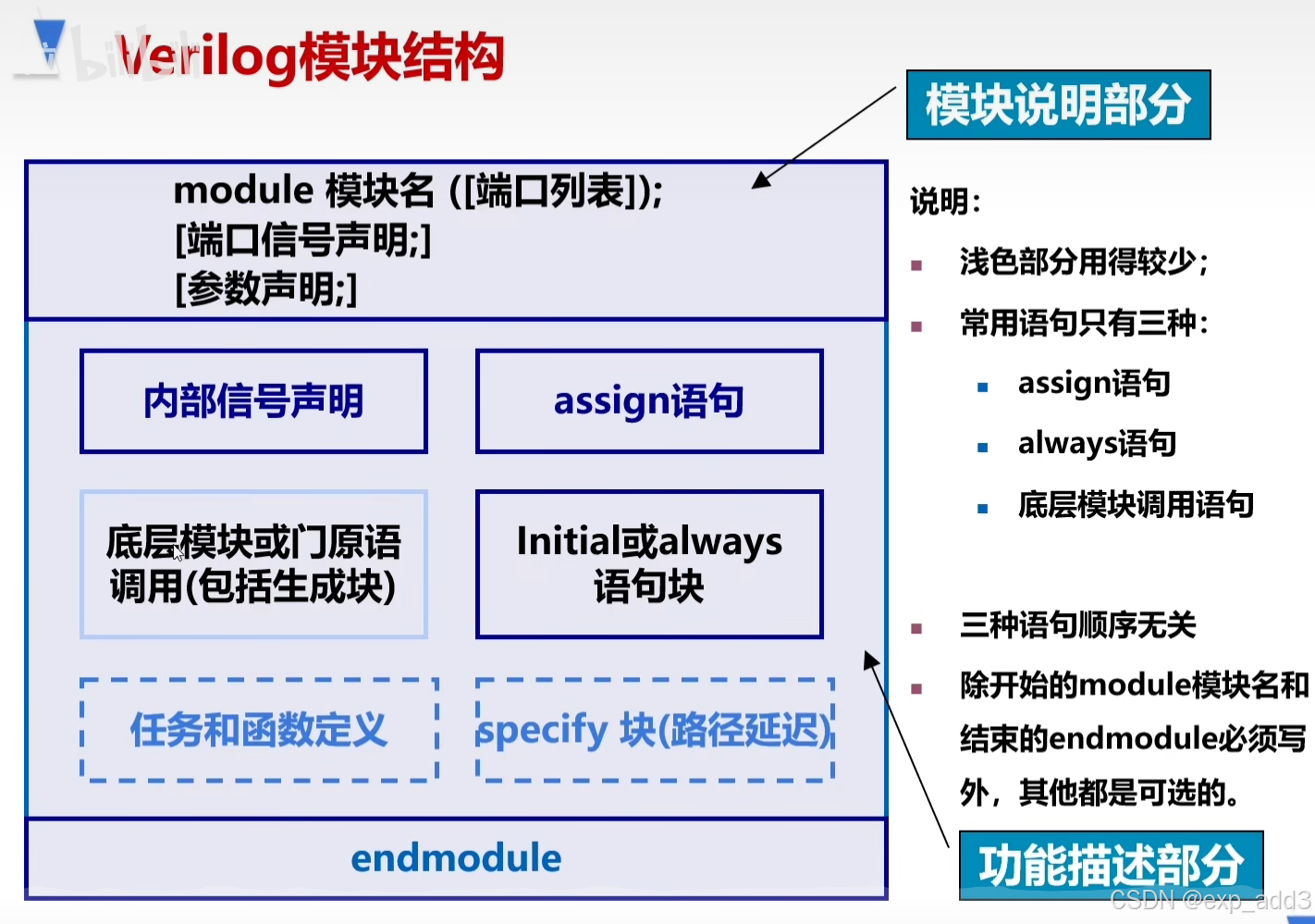

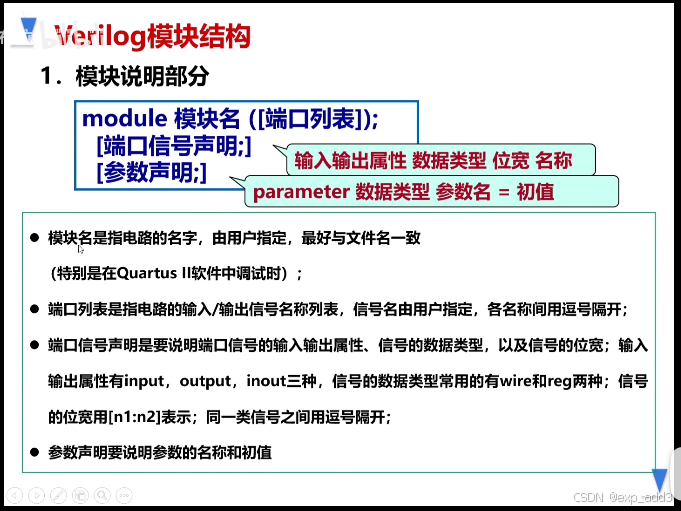

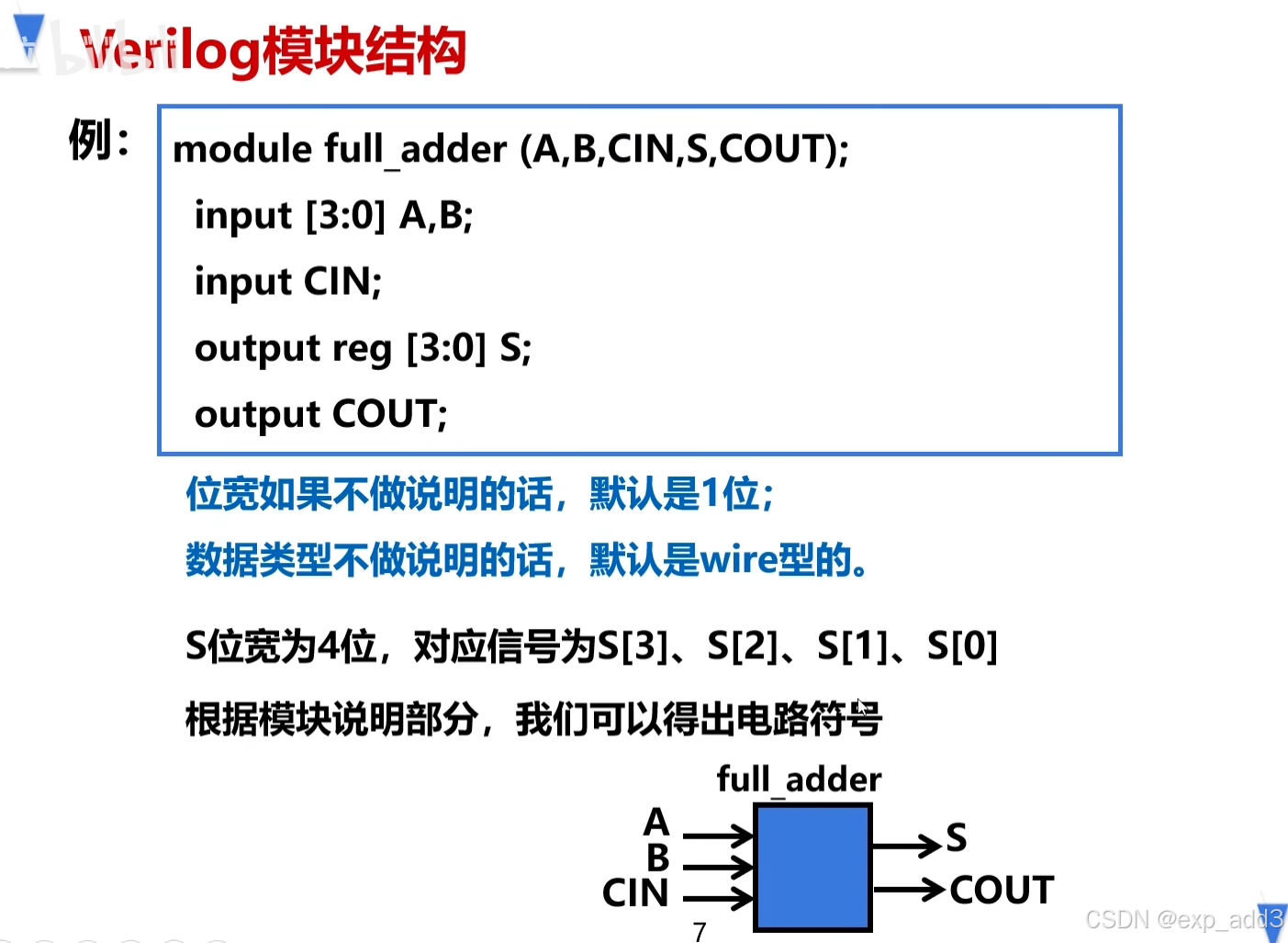

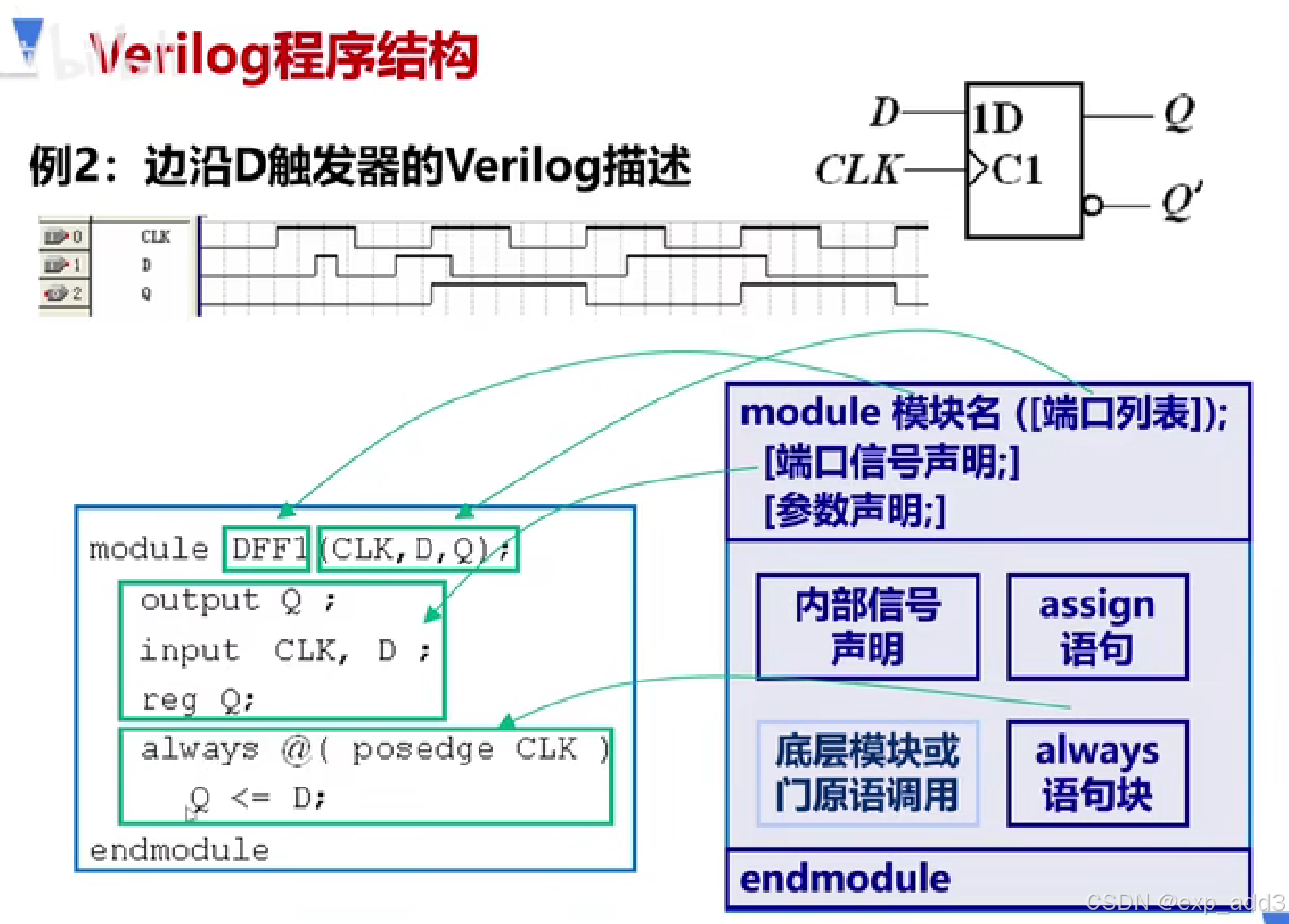

结构

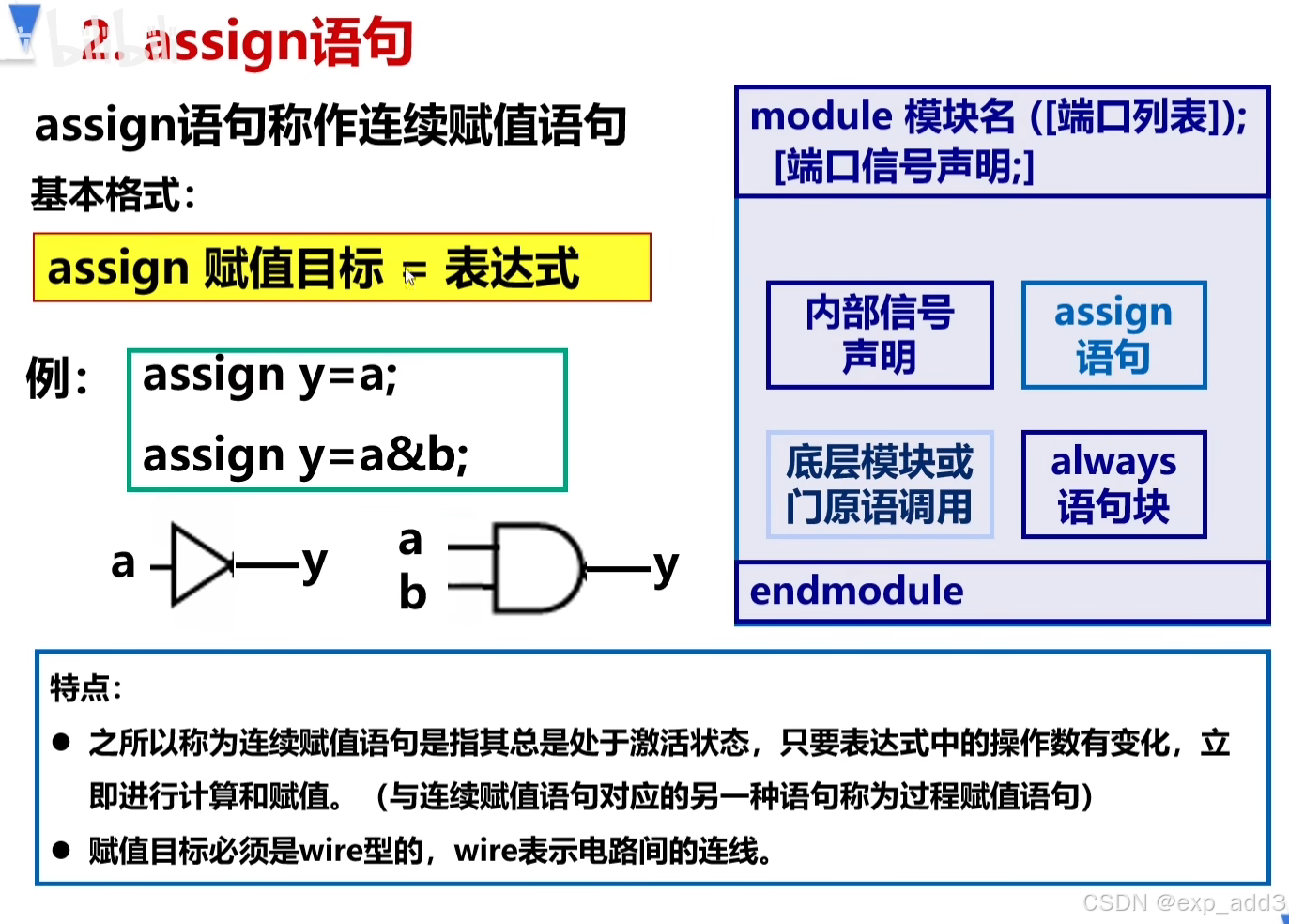

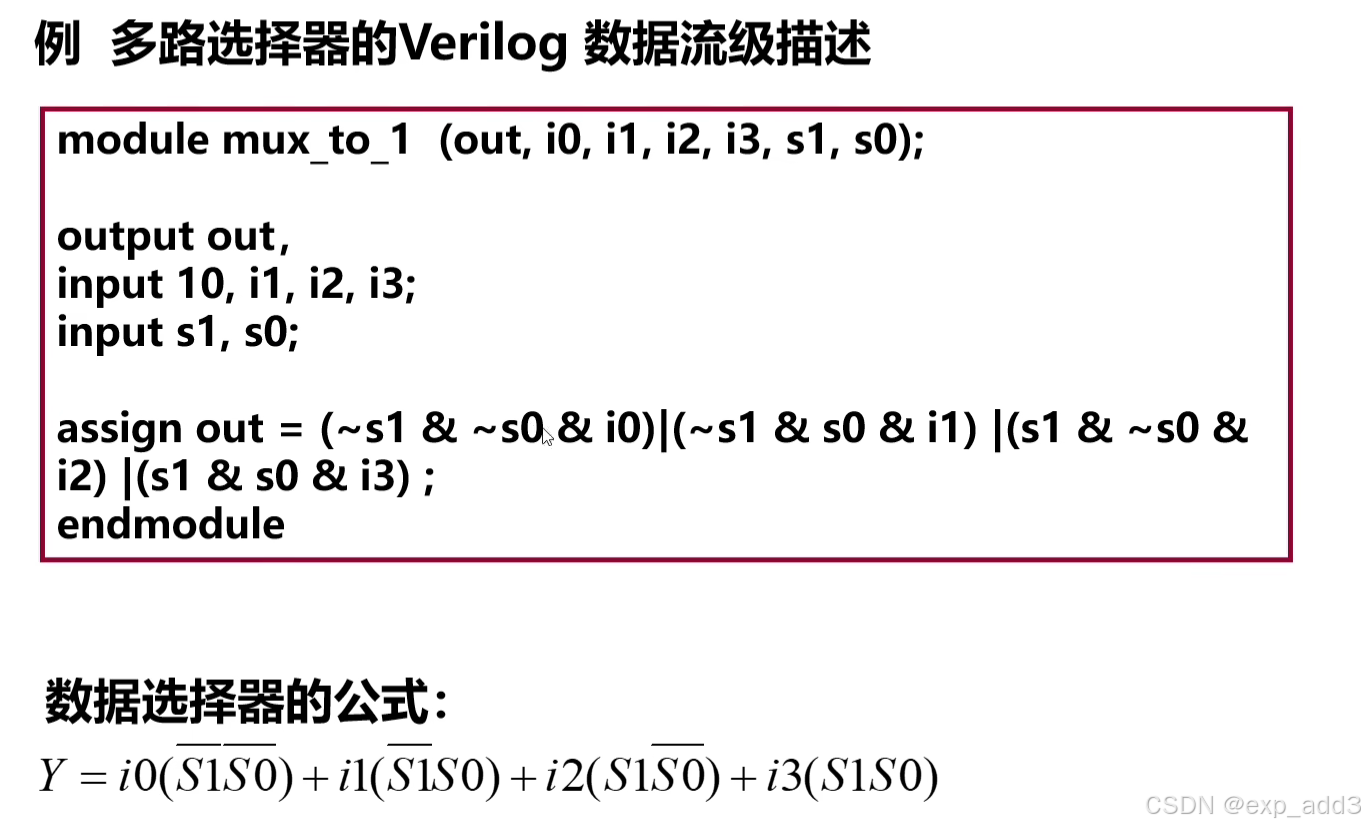

assign语句

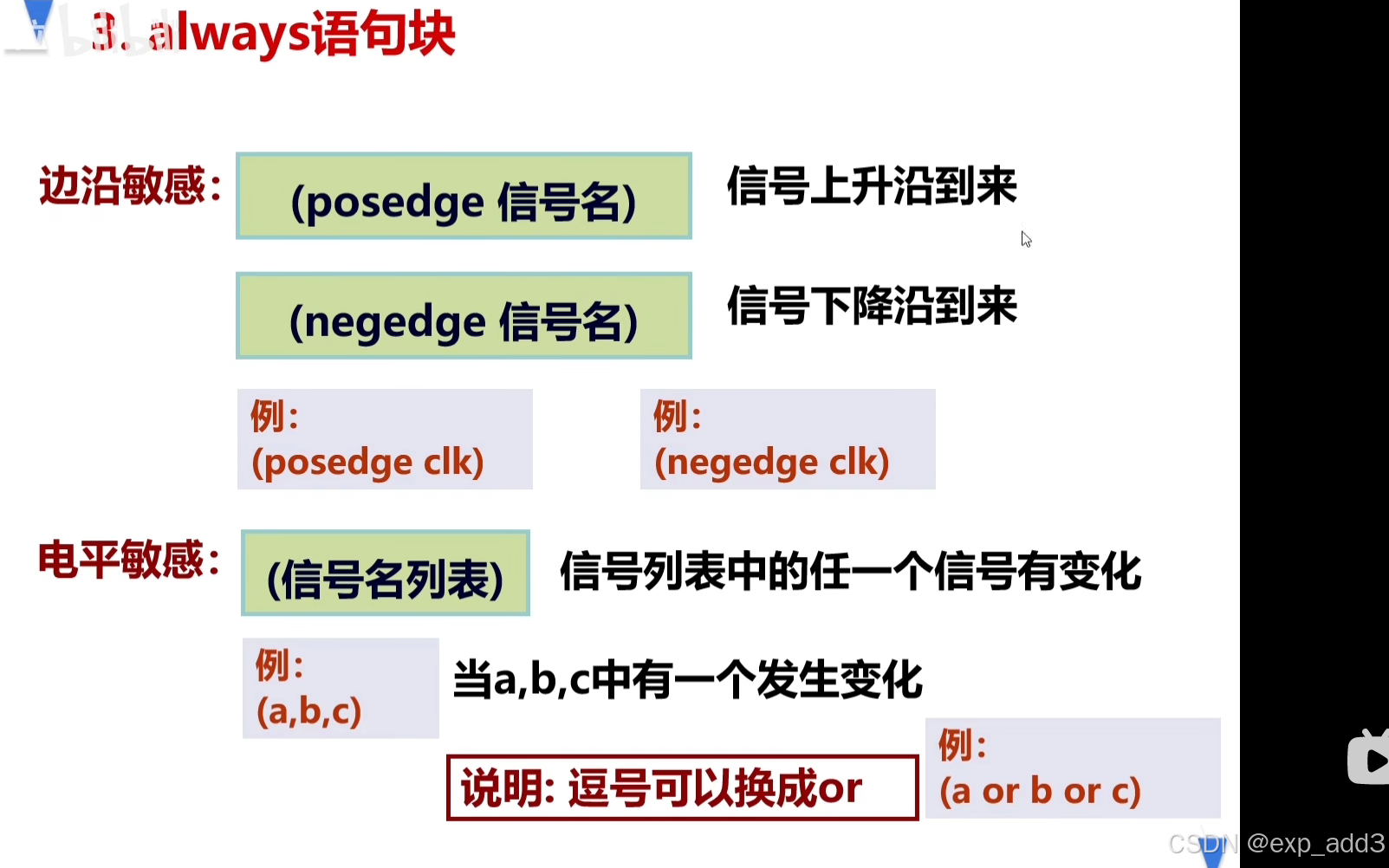

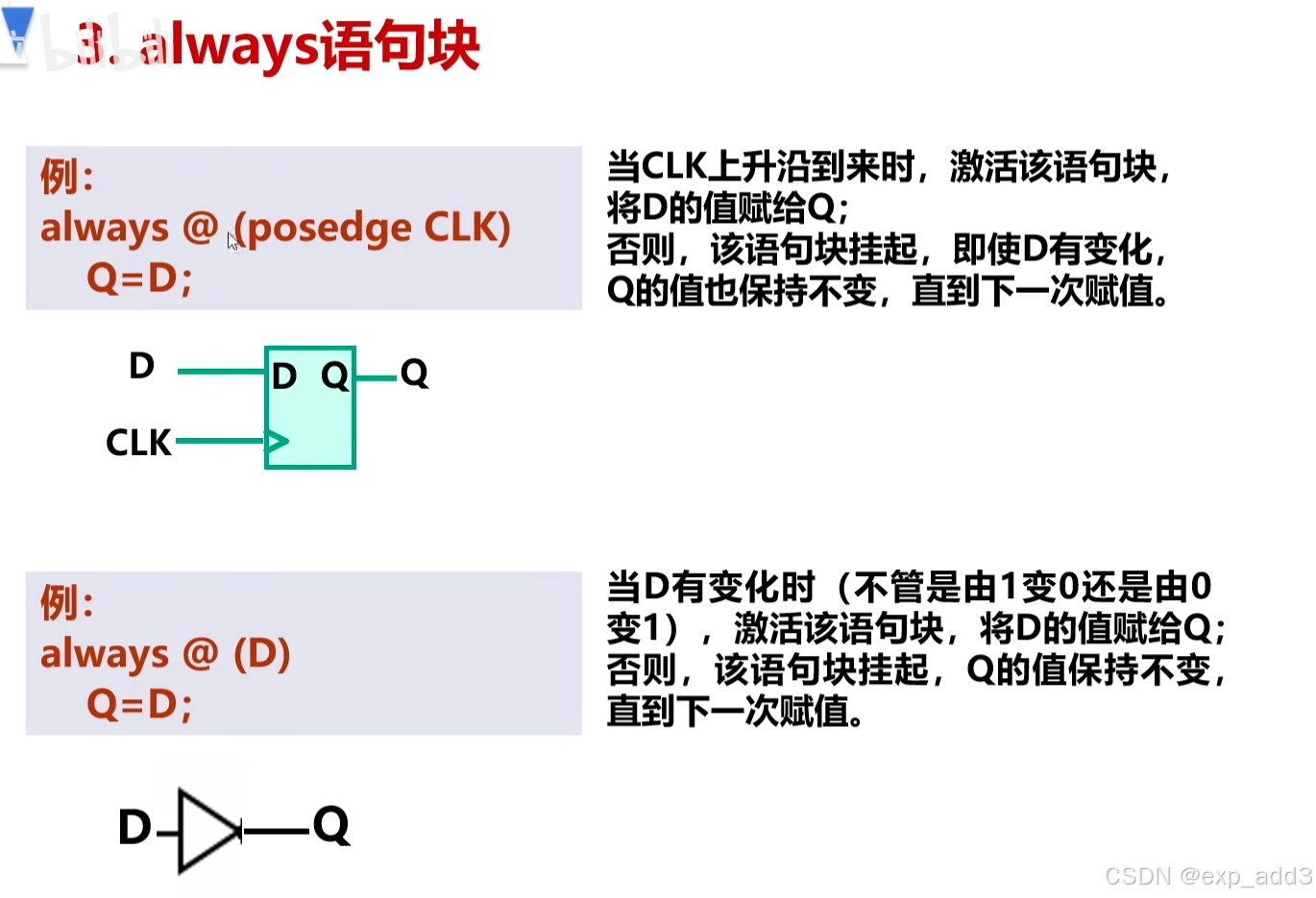

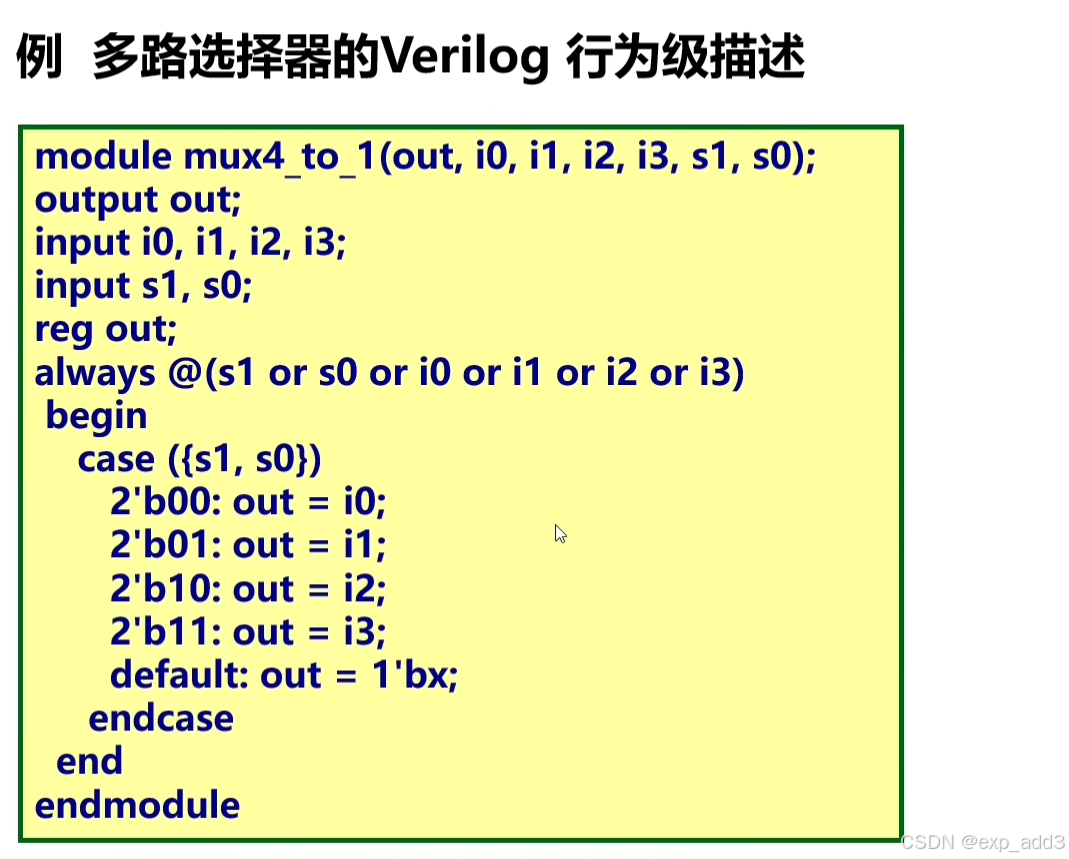

always语句

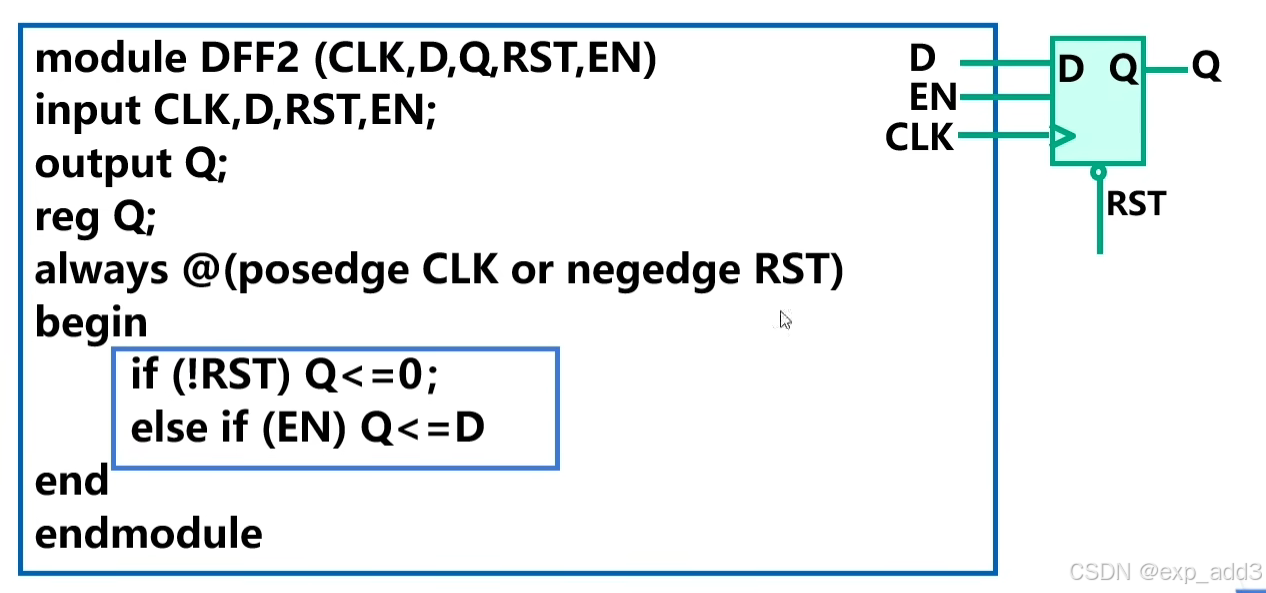

always使用if-else等语句示例

这里CLK上升沿或RST下降沿触发时运行,如果RST为0,Q直接输出0,EN为1(使能)时直接把给Q赋值D的信号

这里讲到,begin-end里面的语句是顺序执行的,其他地方都是并行执行的,而且begin end相当于c语言里的花括号

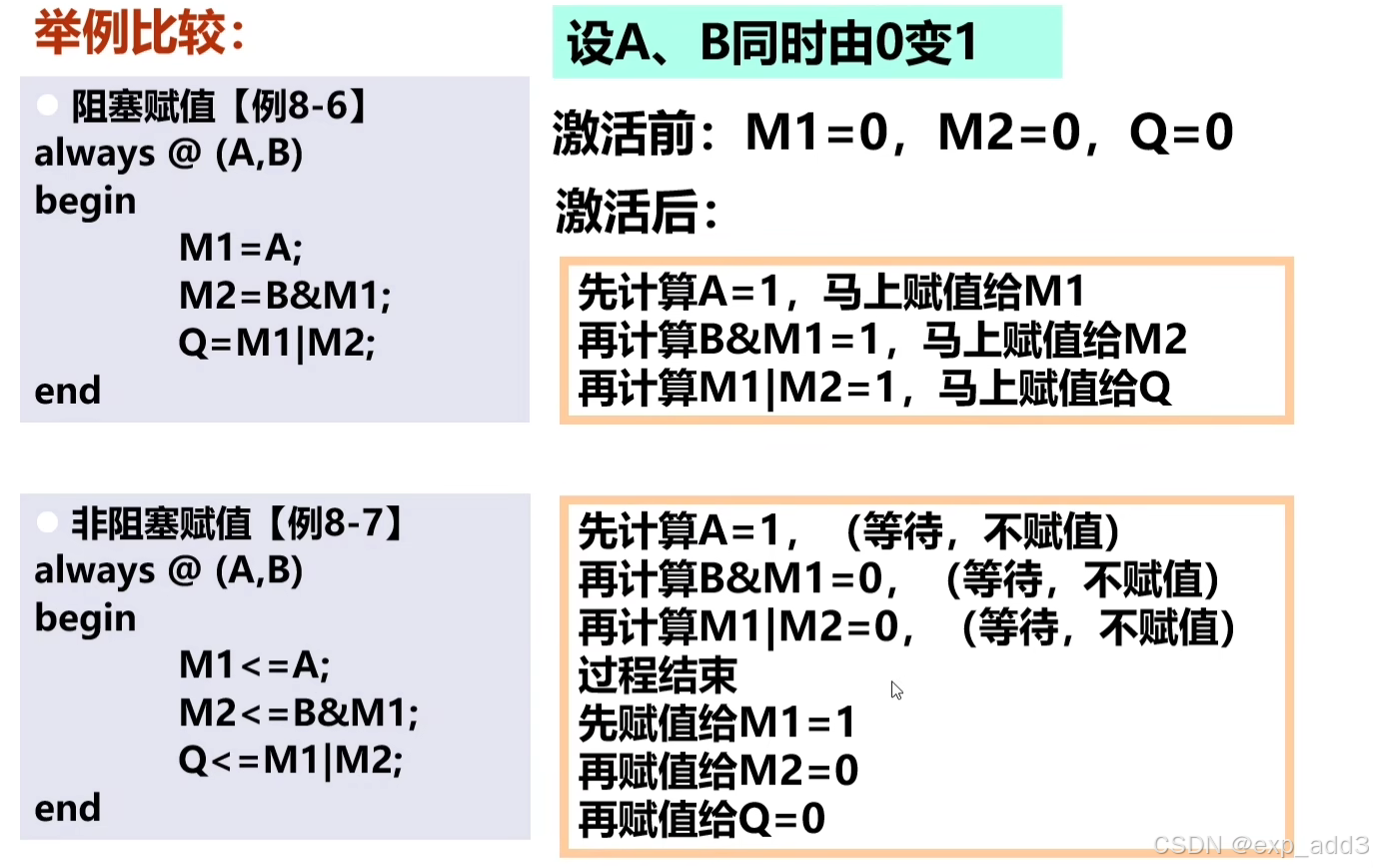

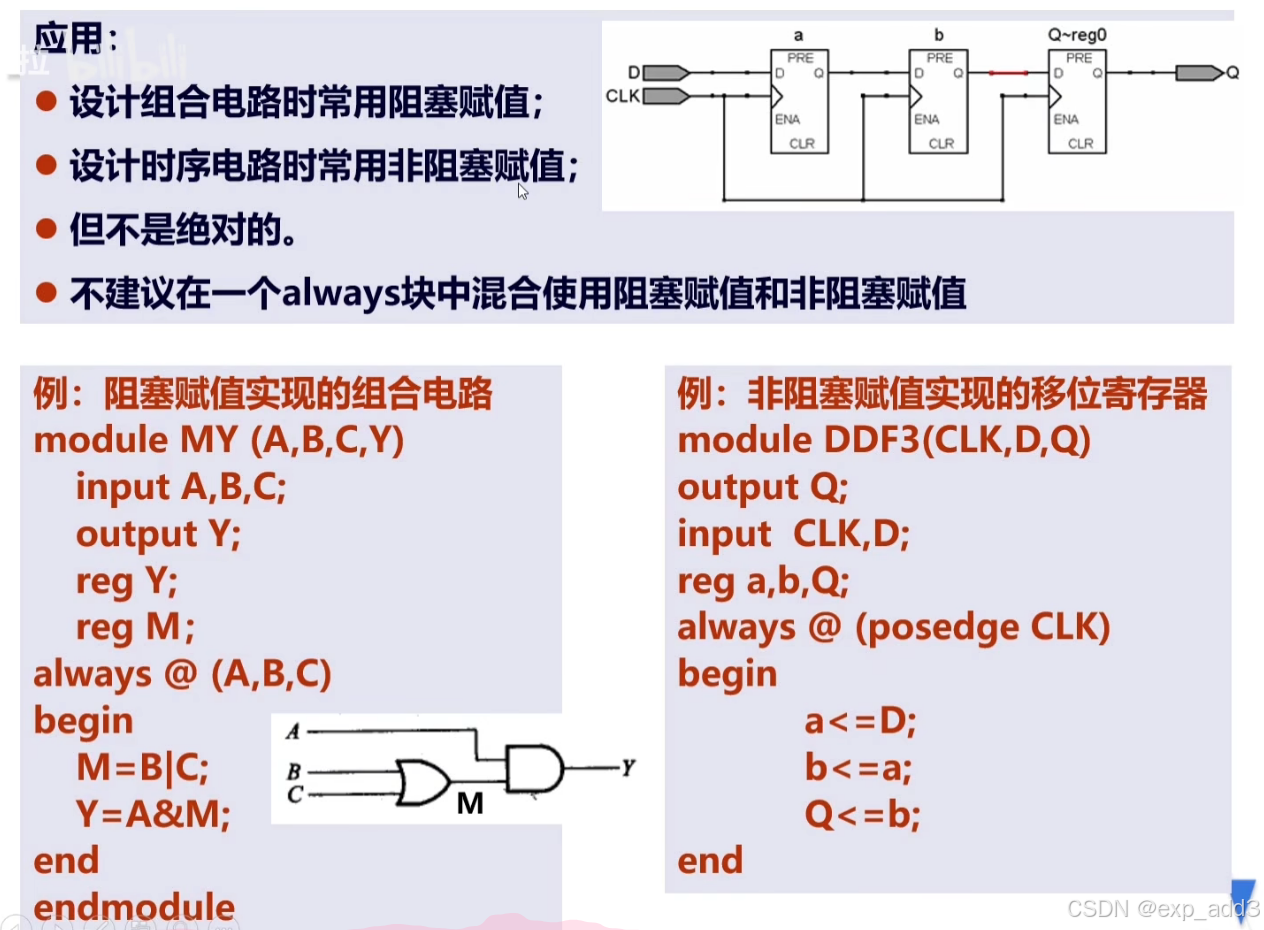

= 与 <=

区别就是 <= 会等后面表达式都计算好再赋值,=是直接赋值然后下一句

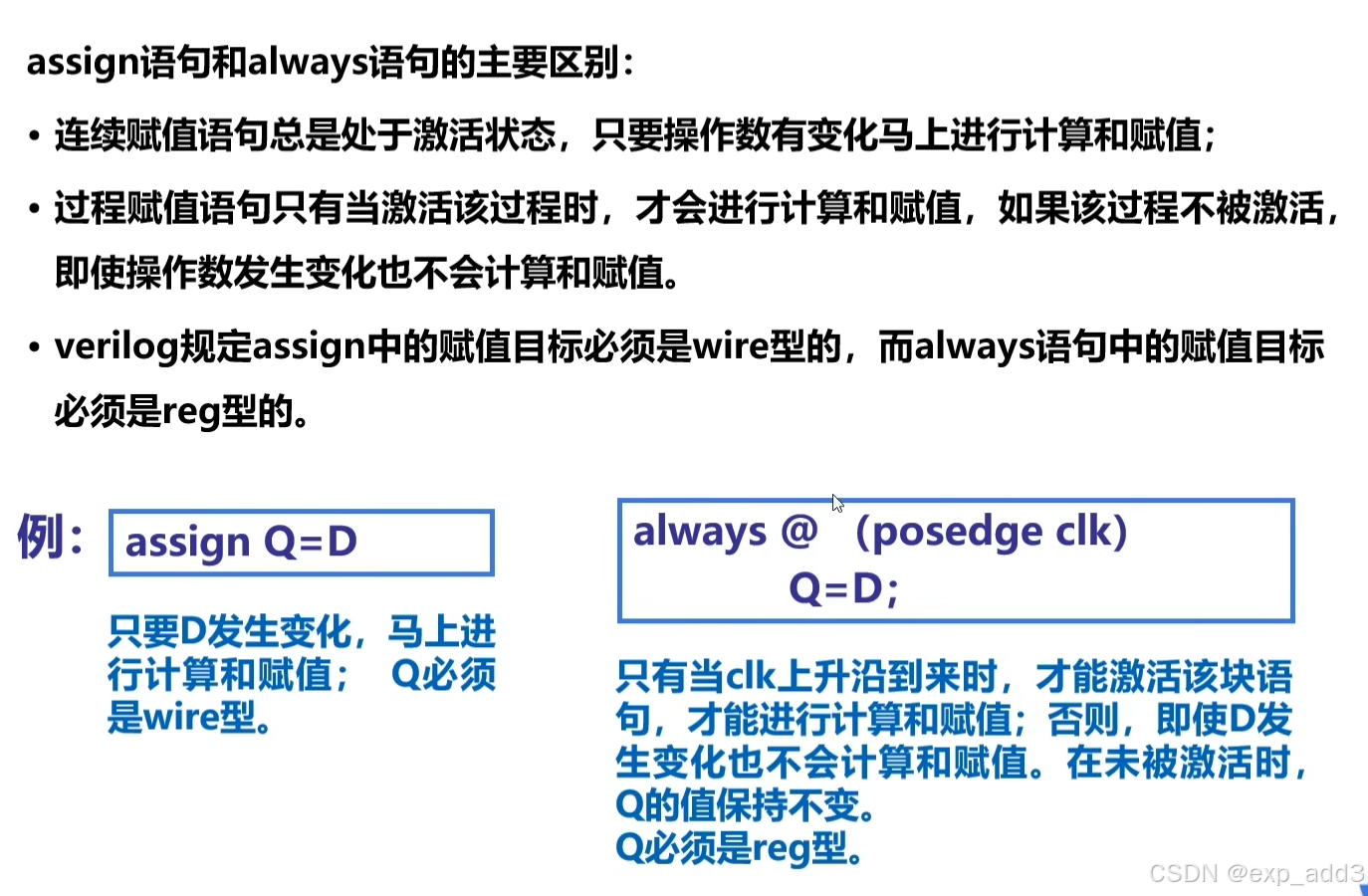

assign和always区别

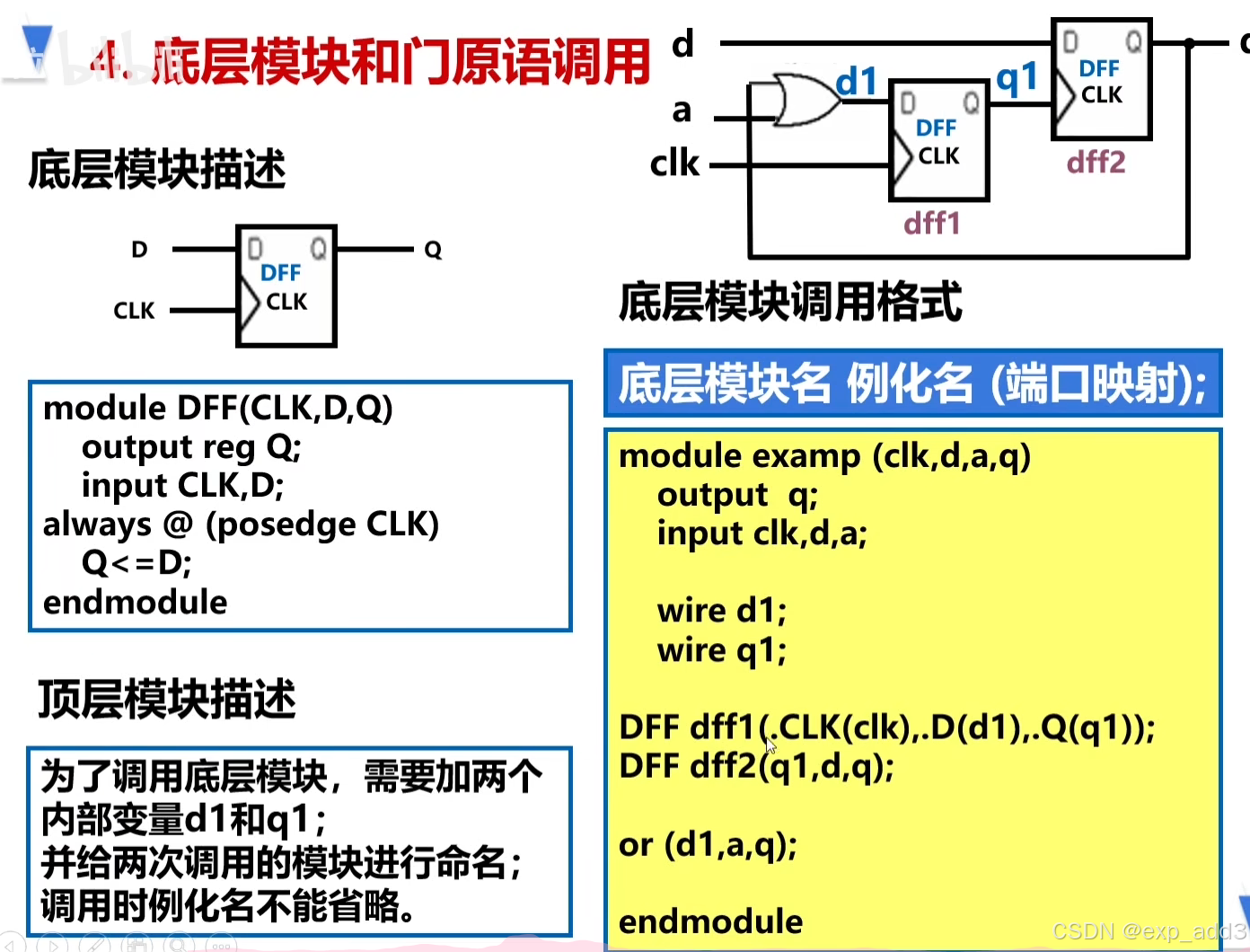

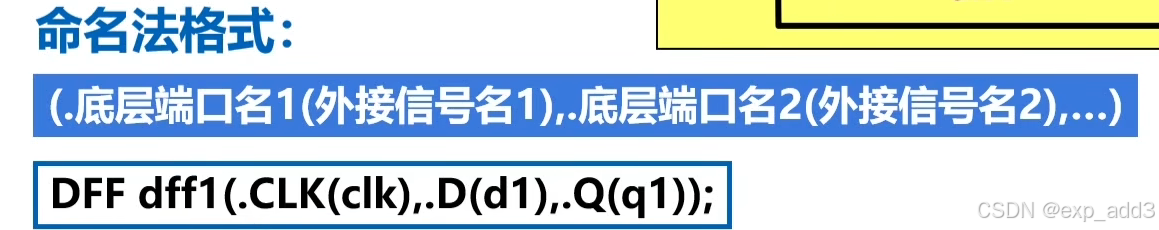

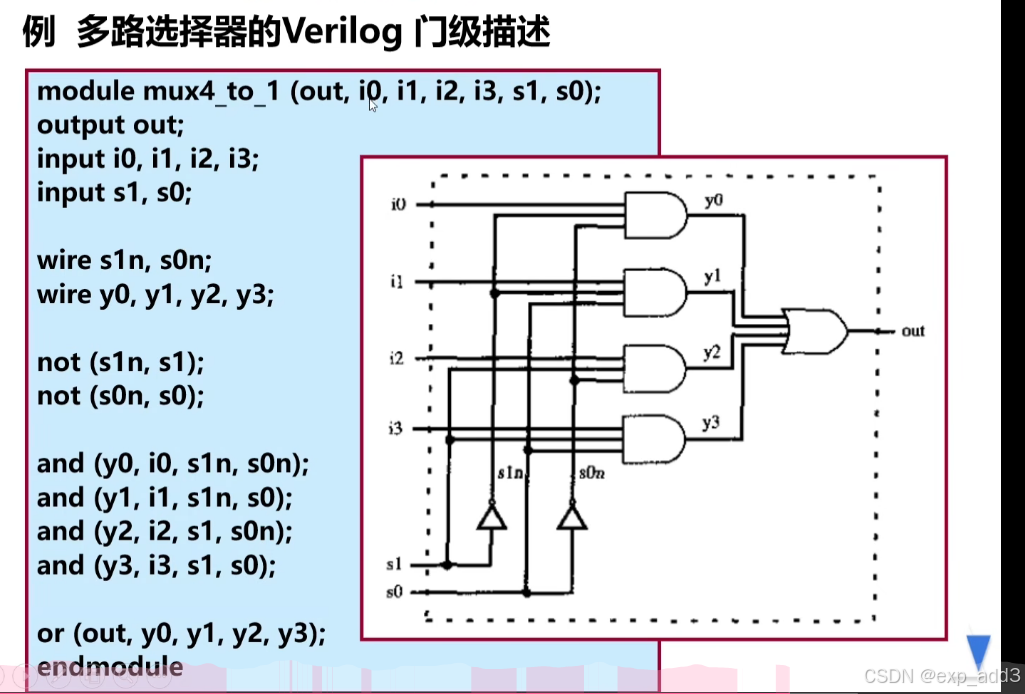

底层模块和门原语调用

调用时赋值方法是 DFF dff1(.CLK(clk), .D(d1), .Q(q1)); 少用按顺序输入参数的方法,如dff2

函数里面指定变量 用 点 + 函数内部名 + (输入参数)

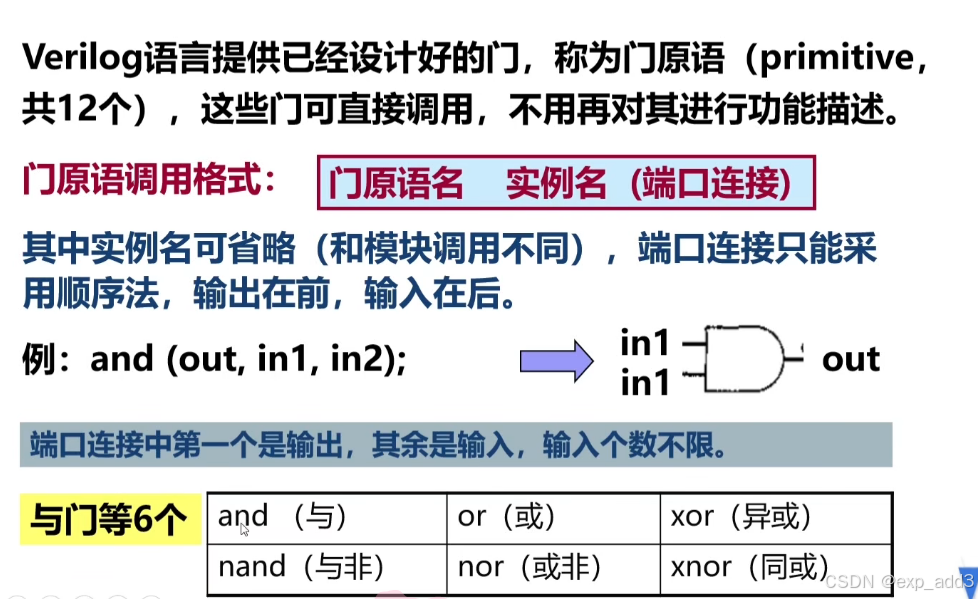

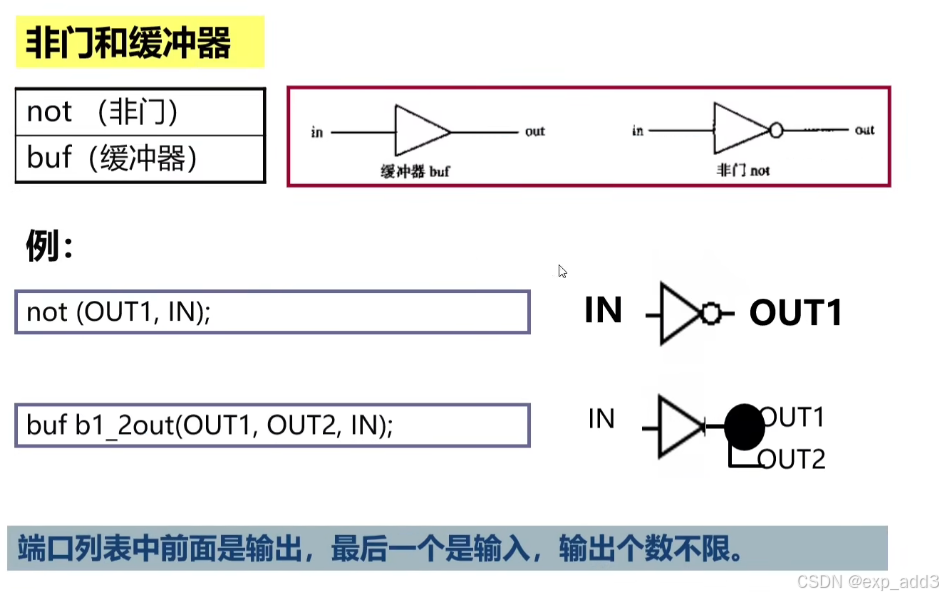

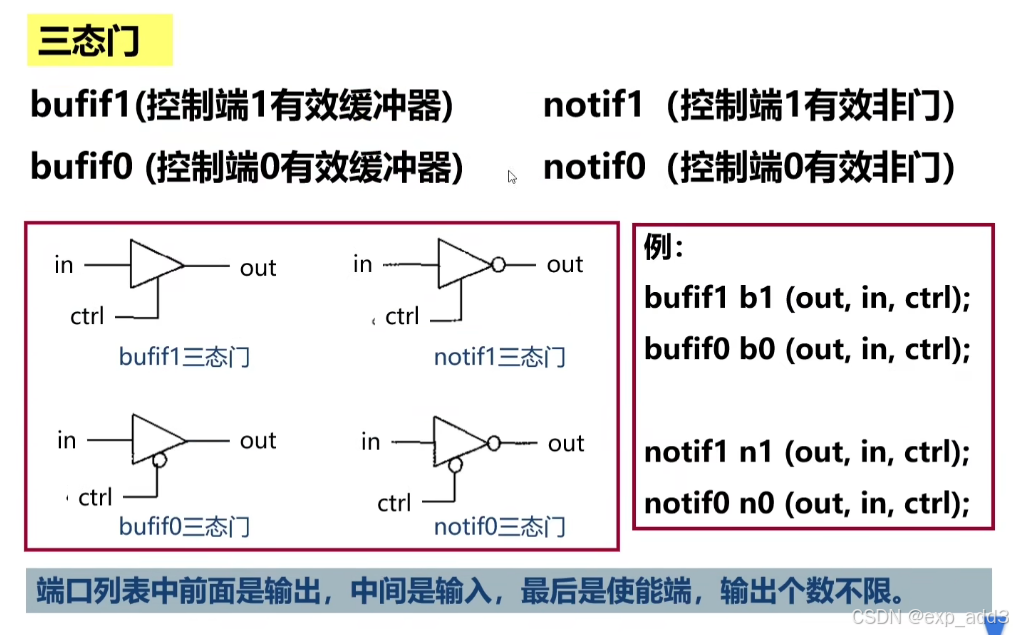

门原语

verilog里面有设计好的门电路,可以直接调用

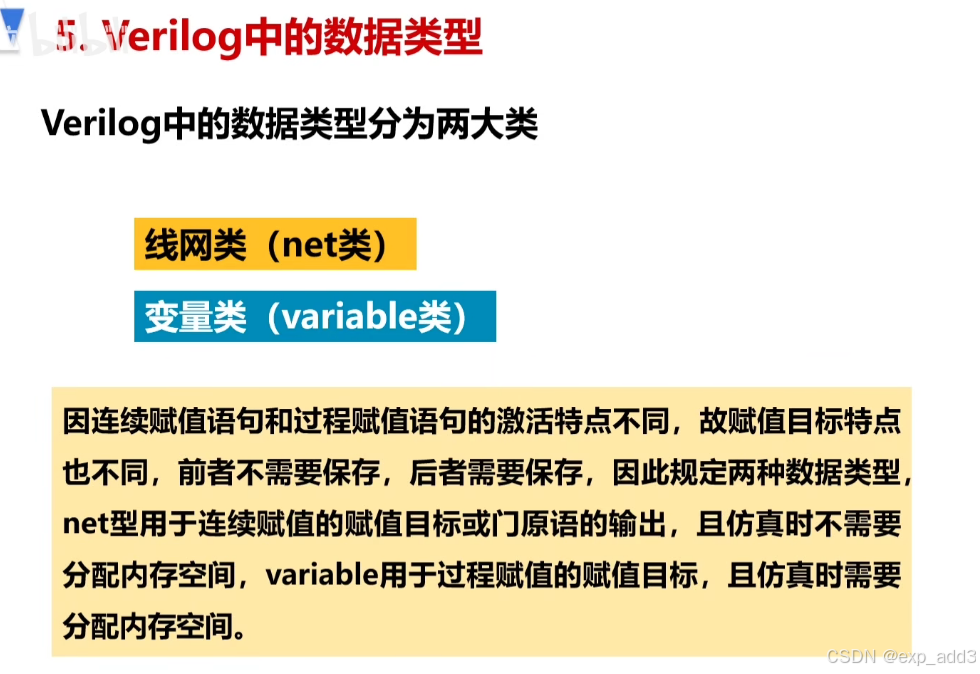

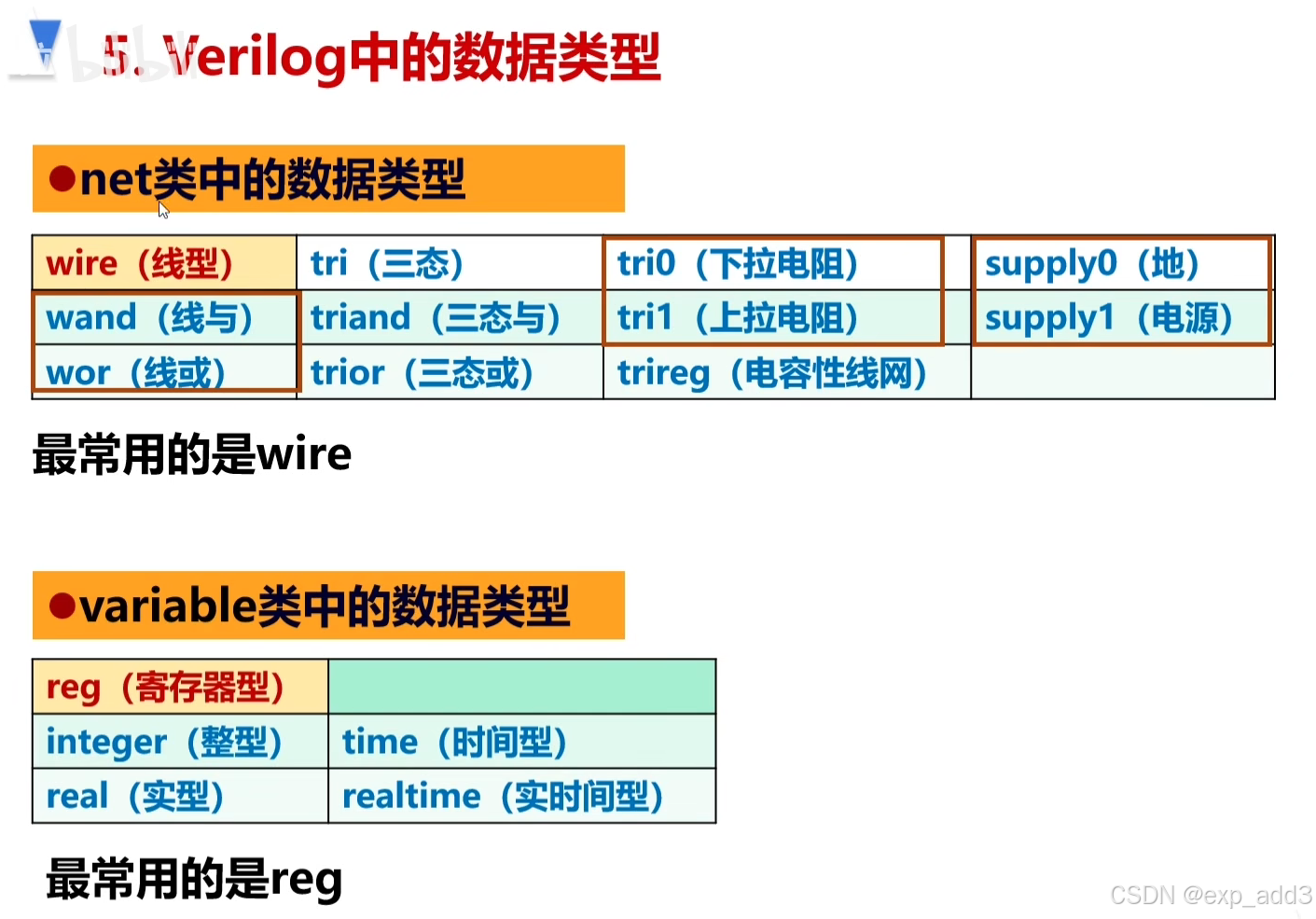

数据类型

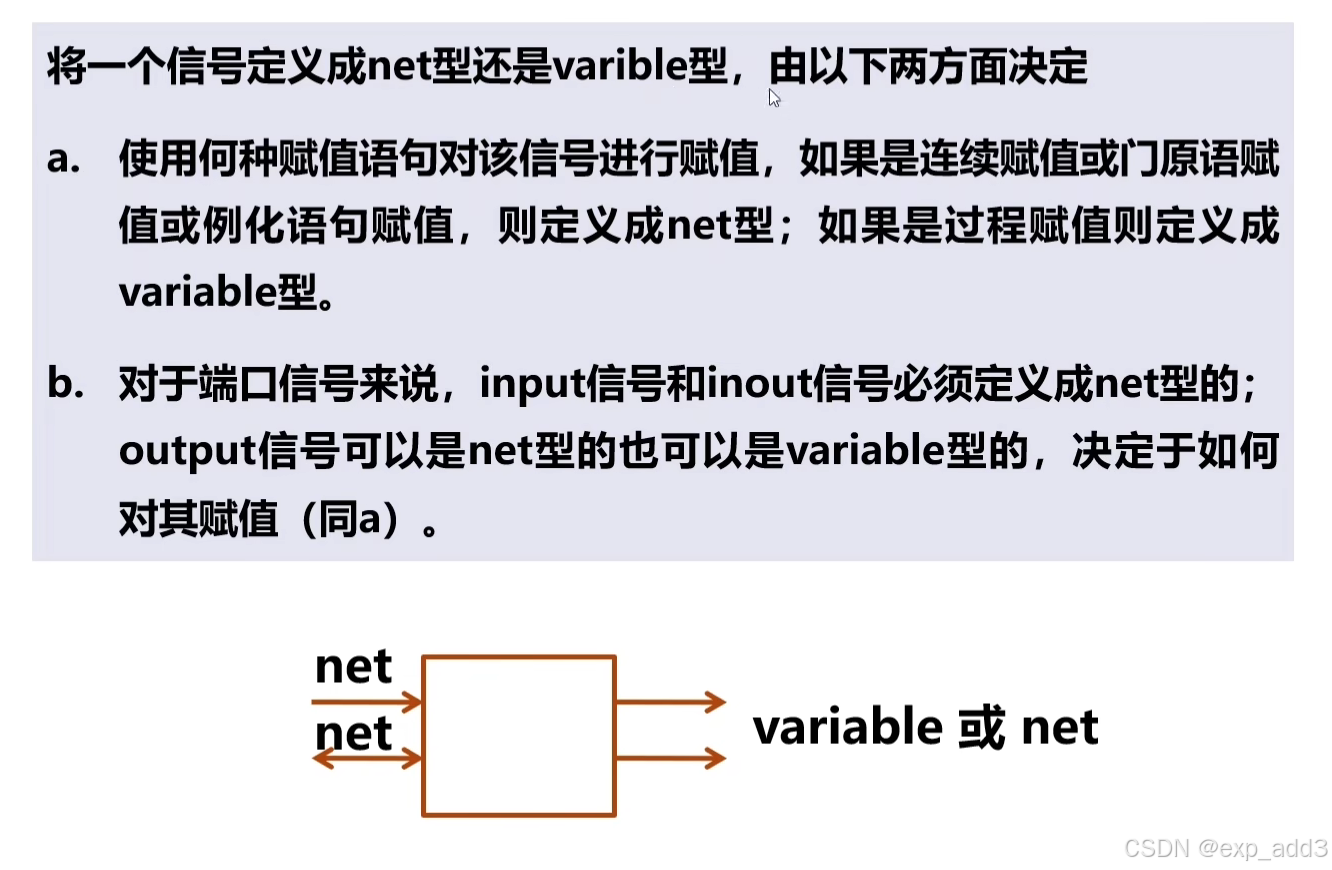

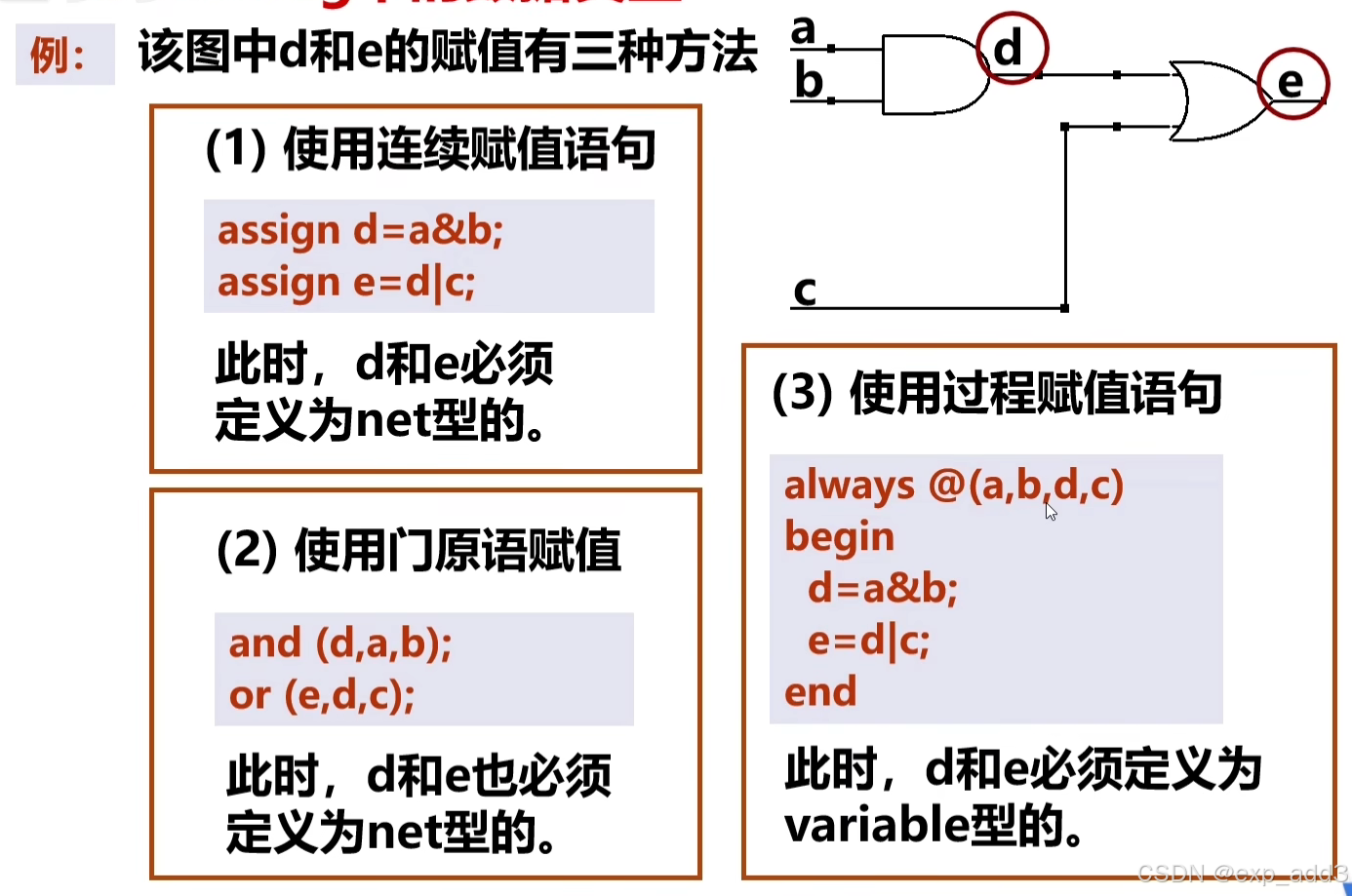

如何去正确定义数据类型

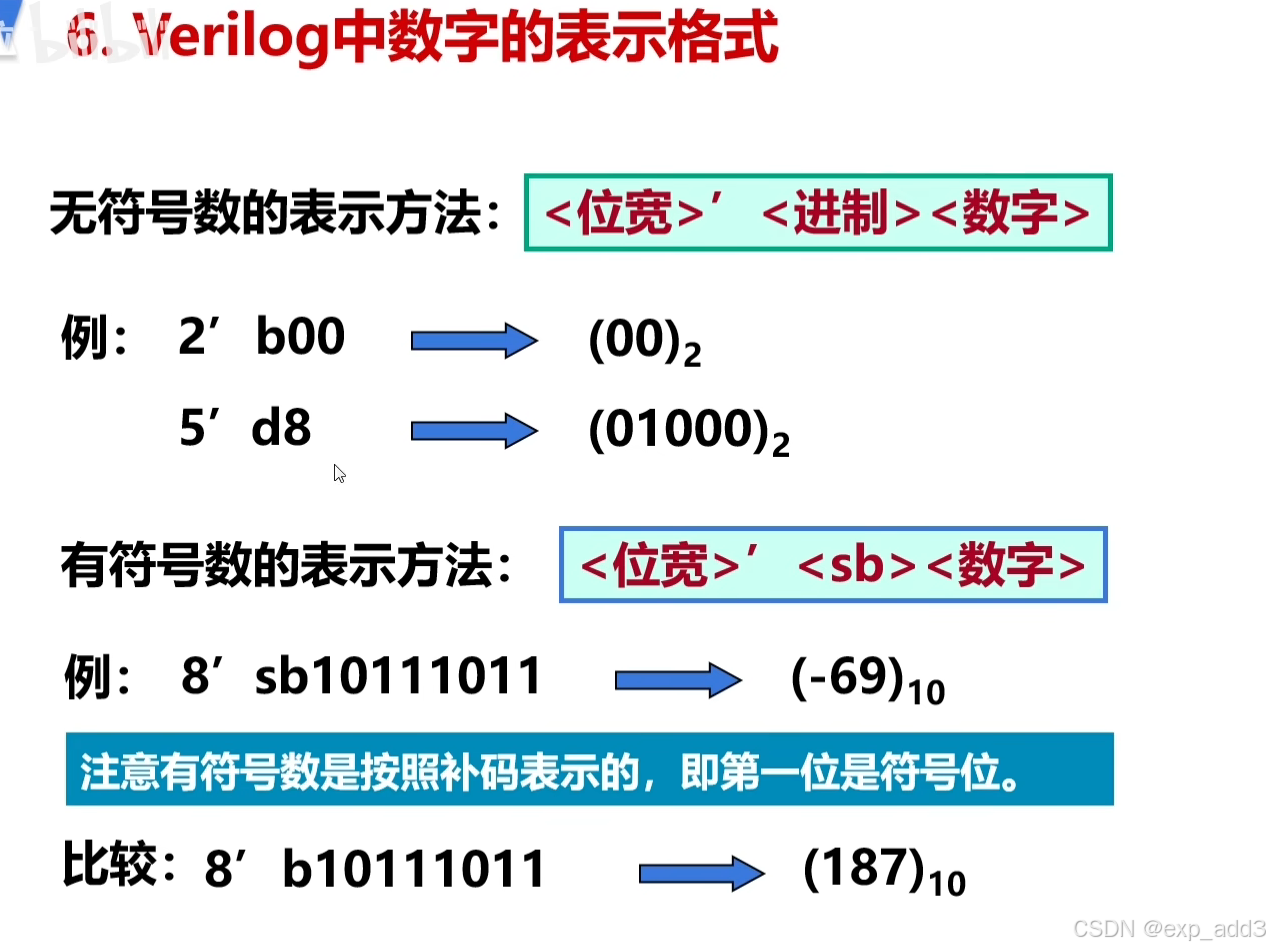

数字类型

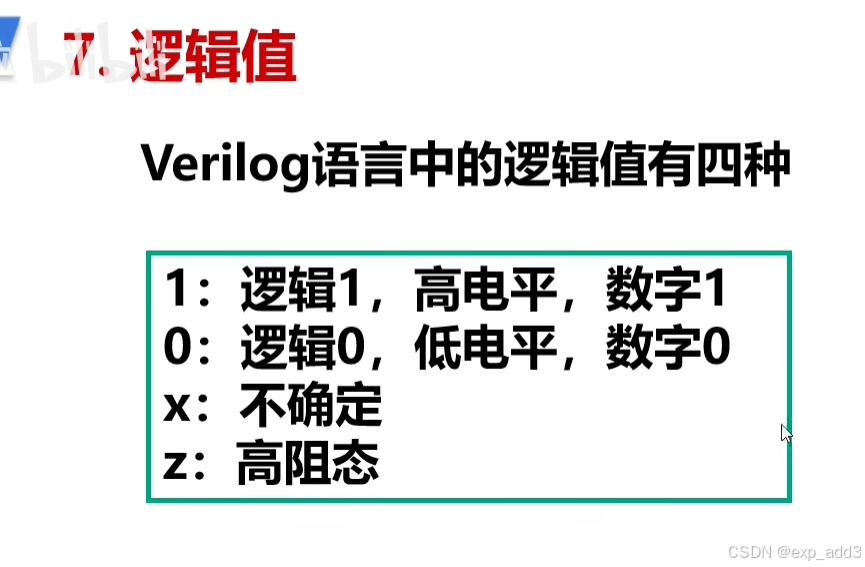

逻辑值

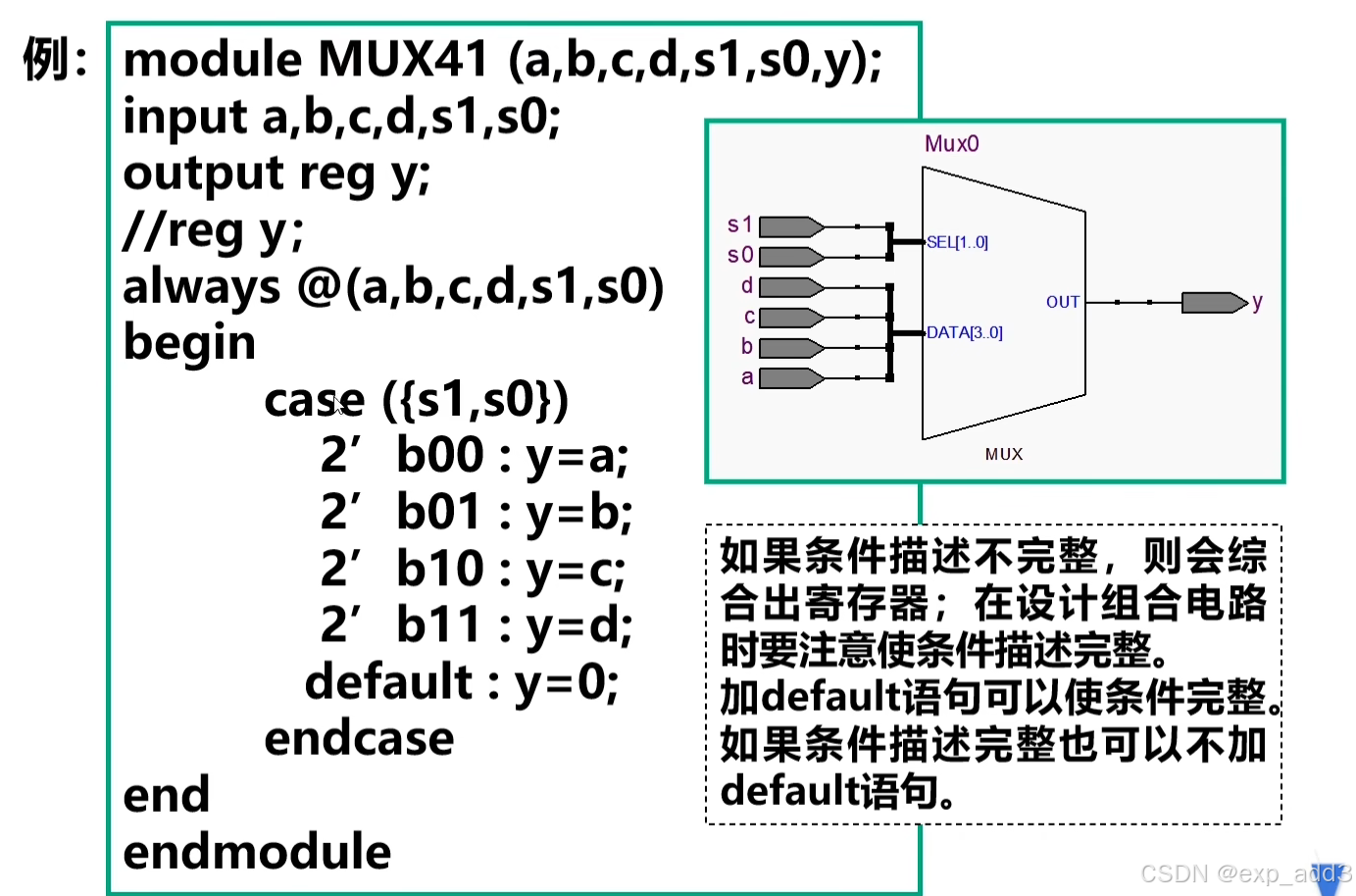

逻辑语句

if else c语言

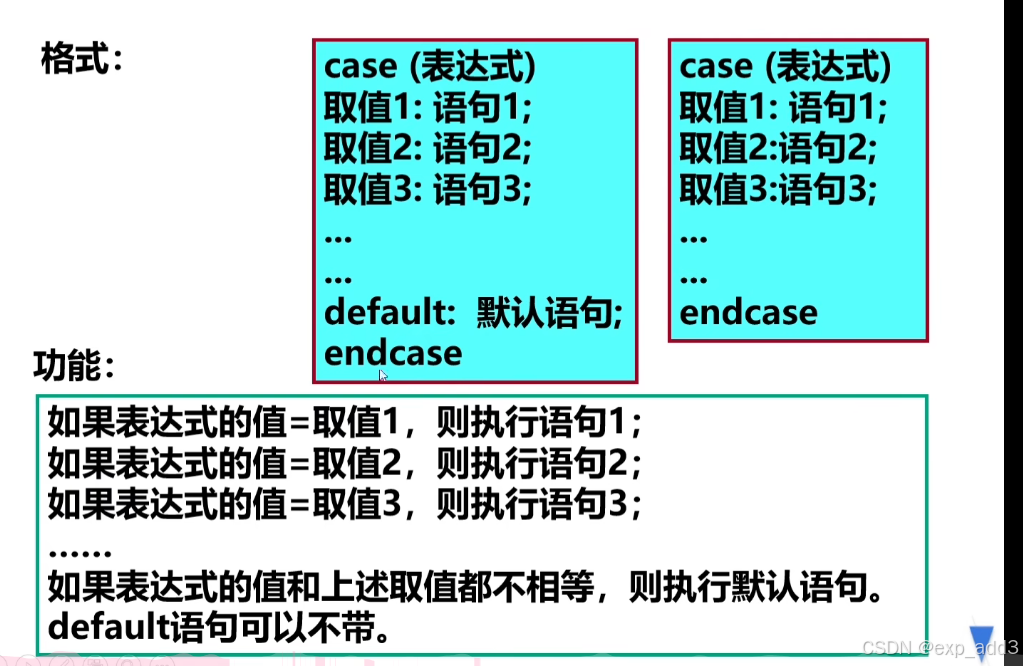

csae 语句 多了一个endcase

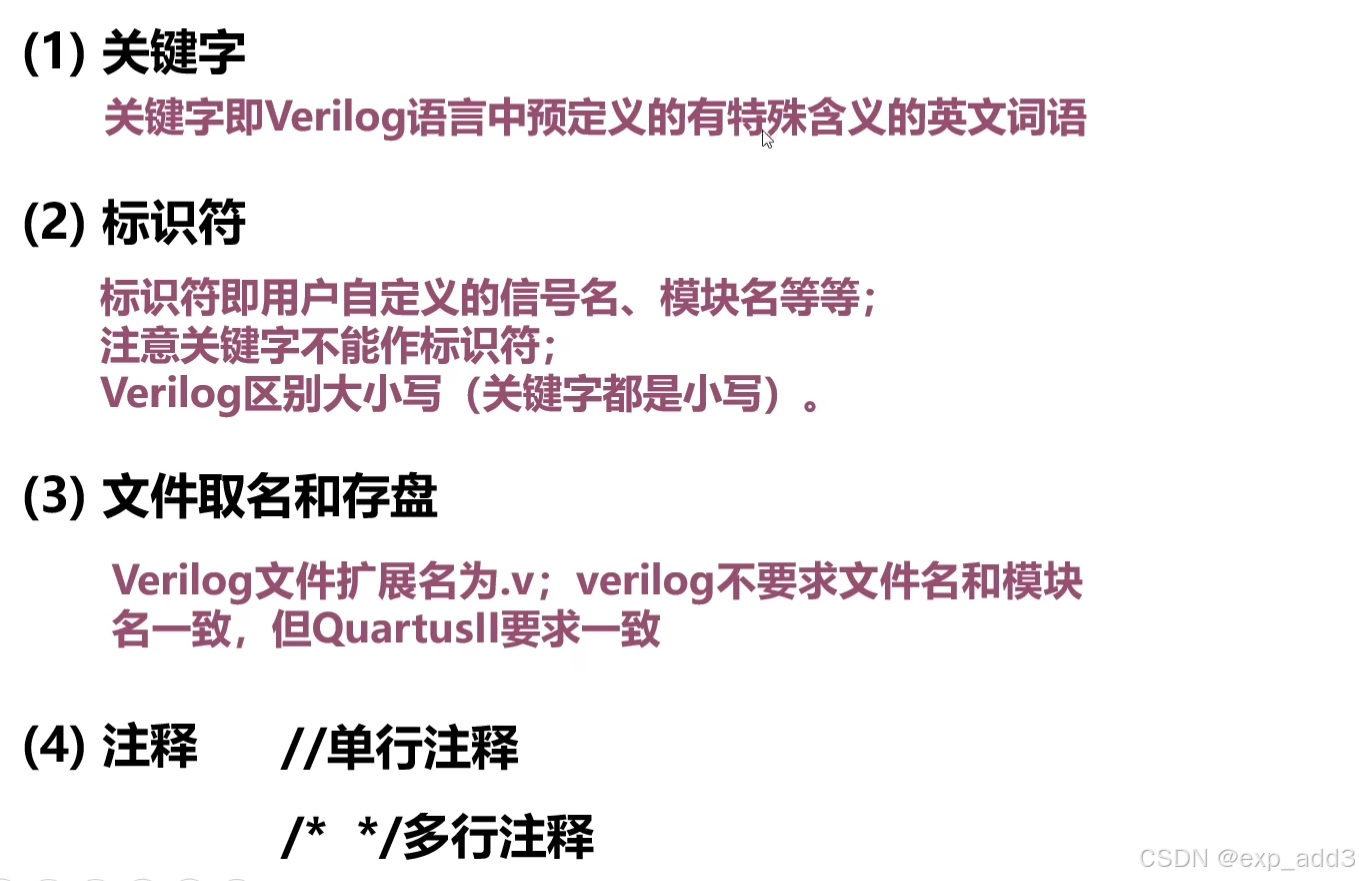

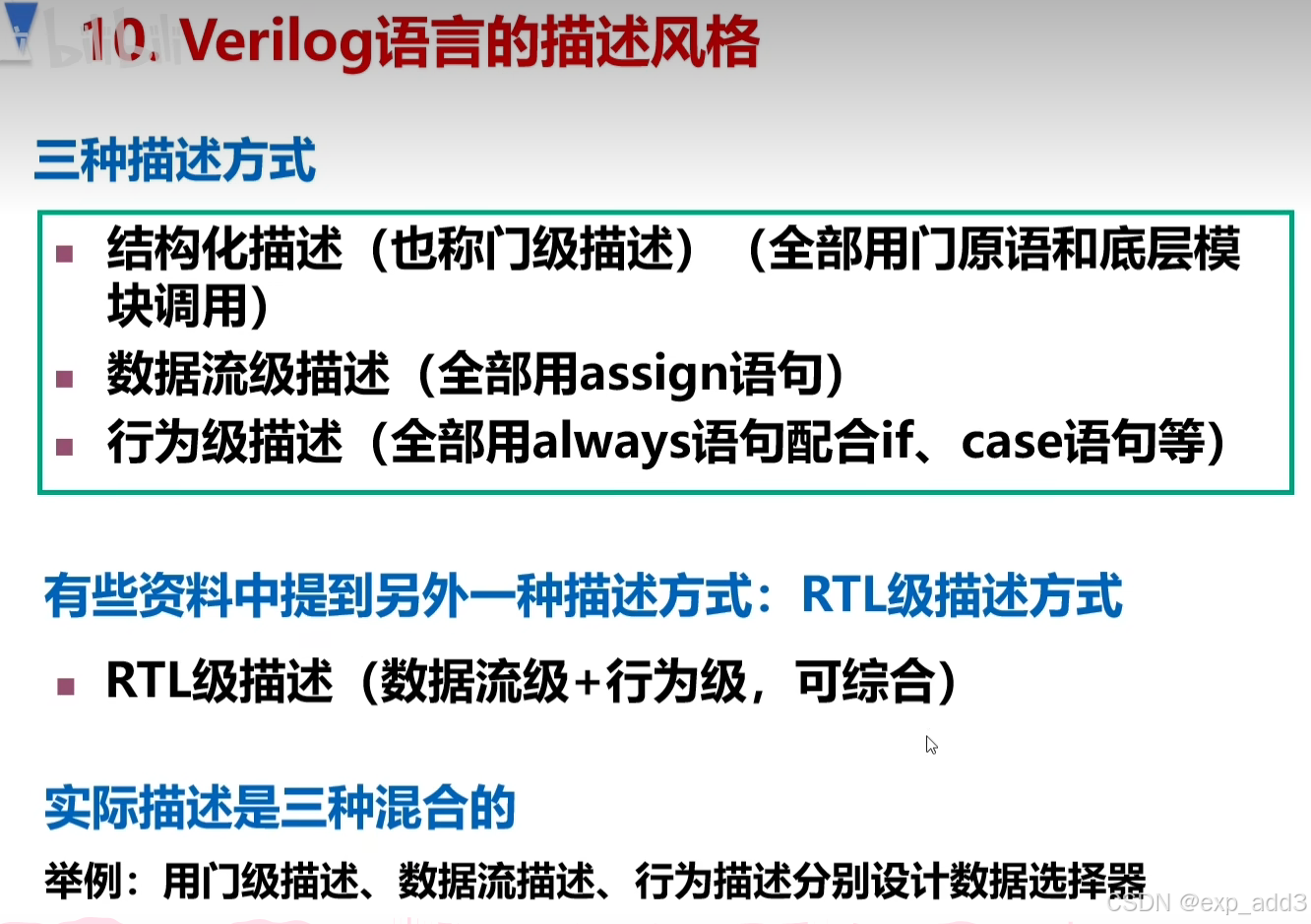

语言风格

其他

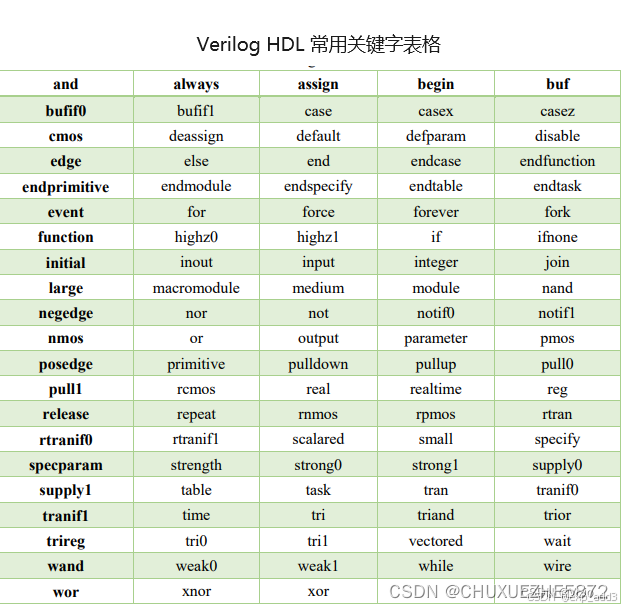

关键字

5914

5914

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?