异步复位的串联T触发器

题目描述:

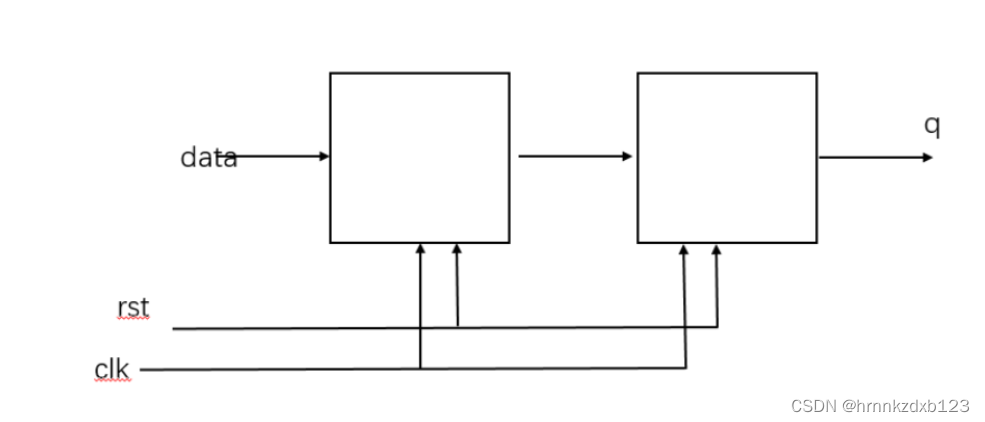

用verilog实现两个串联的异步复位的T触发器的逻辑,结构如图:

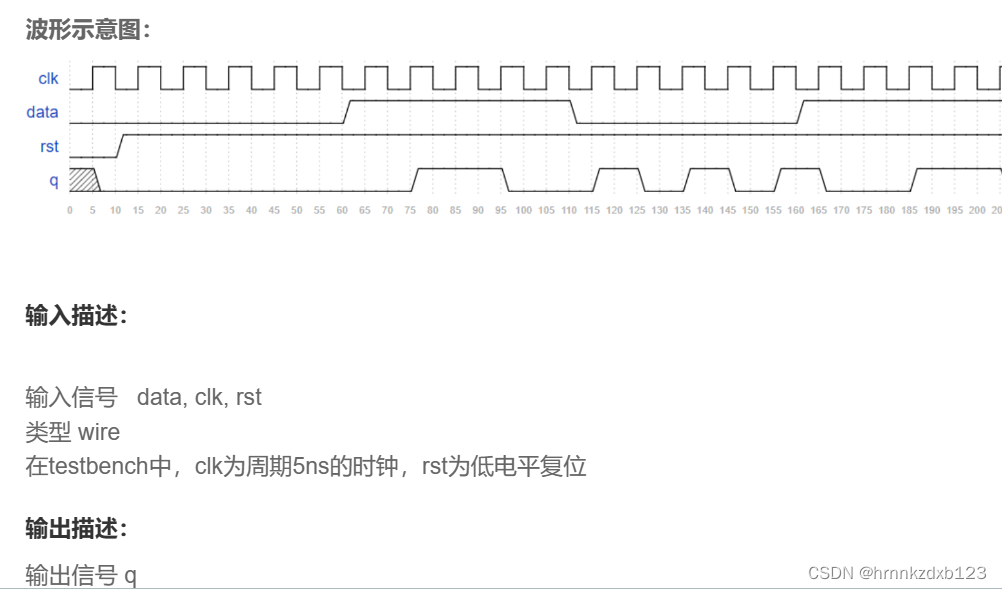

对于此题来说,我们先了解一下T触发器。T触发器可以理解为,有数据来了就把原来的数据进行反转,没数据来,就保持为原来的数据。

因此,设置第一个T触发器的输出为q1,这样就有了第一个T触发器的代码。

从而,用q1作为第二个T触发器的数据输入,从而q也可以进行编写。

代码如下:

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

//*************code***********//

reg q1;

always @(posedge clk or negedge rst)begin

if(rst==1'b0)begin

q1 <= 0 ;

end

else if(data)begin

q1 <= ~q1 ;

end

end

always @(posedge clk or negedge rst)begin

if(rst==1'b0)begin

q <= 0 ;

end

else if(q1)begin

q <= ~q ;

end

end

//*************code***********//

endmodule

T触发器在实际应用中并不多见,用到了就这么写就行。

注意rst和rst_n。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?