一、flash工艺

1.1 Logic vs Flash

数据掉电后消失(PC / phone / server : CPU +)

① SRAM

② DRAM

数据非易失

① NOR FLASH

② NAND FLASH

③ SSD

④ SATA

⑤ U 盘

⑥ 移动硬盘

⑦ 机械磁盘

数据掉电后保存(MCU , 单芯片方案)

eflash

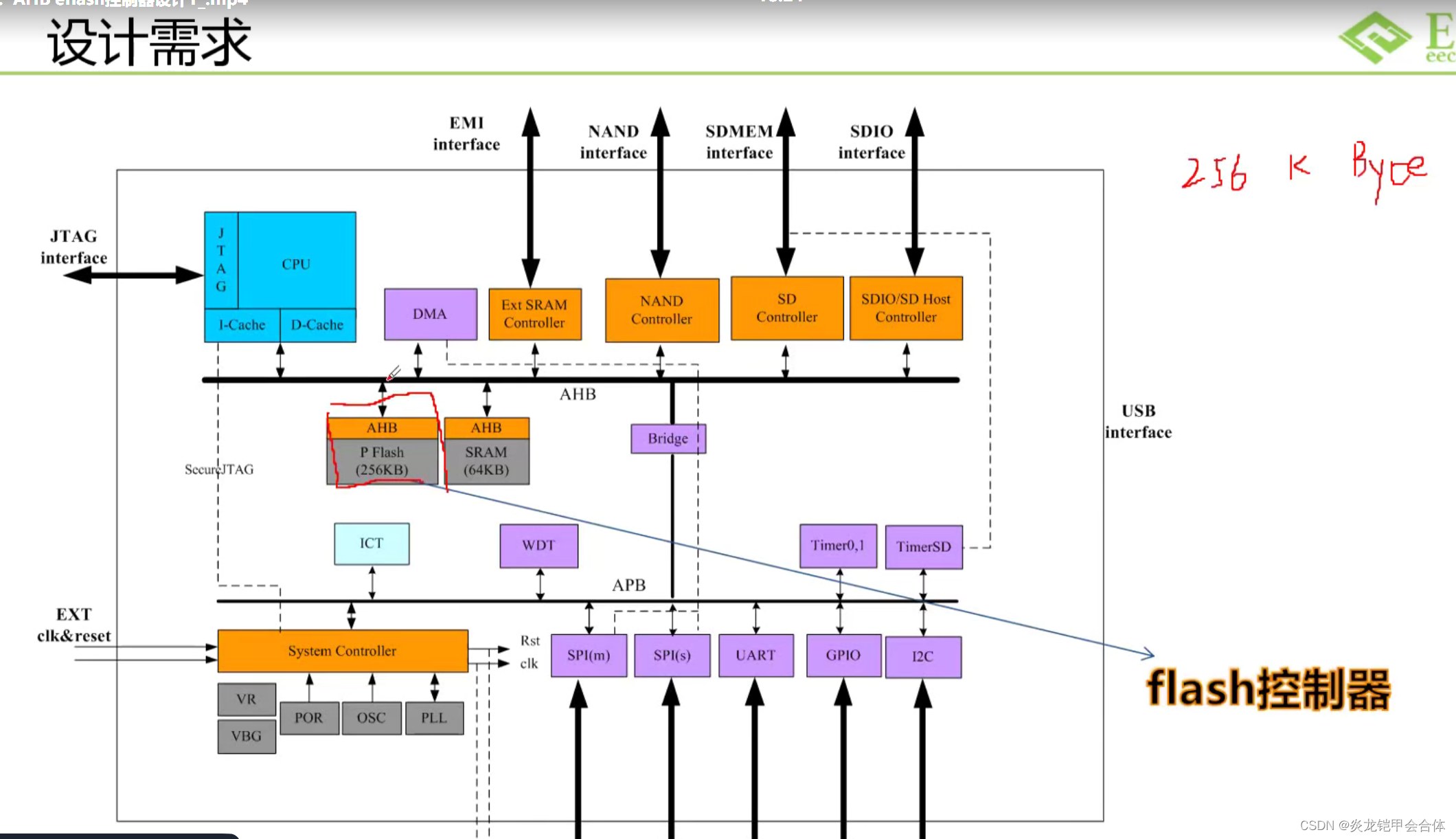

1.2 设计需求

Eflash 控制器

① 作为系统程序的存储空间;

② flash存储体IP由代工厂提供;

③ 项目完成 flash 控制器的设计

④ eflash 作为 ahb slave 的形式存在

特性:

① 支持 32位 的 ahb slave interface (不支持该总线 busy 传输类型)

② 支持eflash 的多周期的读、写、页擦操作(2块独立的 eflash 串联封装)

③ eflash 操作可配置(时序、功能)(flash 的异步操作)

④ 支持 eflash 中的 boot 区空间的擦写保护;

知识点

① amba 总线

② 阅读 flash datasheet 写控制器的能力

③ 如何利用行为级模型进行仿真

④ 关于 boot 的概念

⑤ DFT 的概念

⑥ 文档体系(设计文档体系、验证文档体系)

⑦ 底层驱动的概念

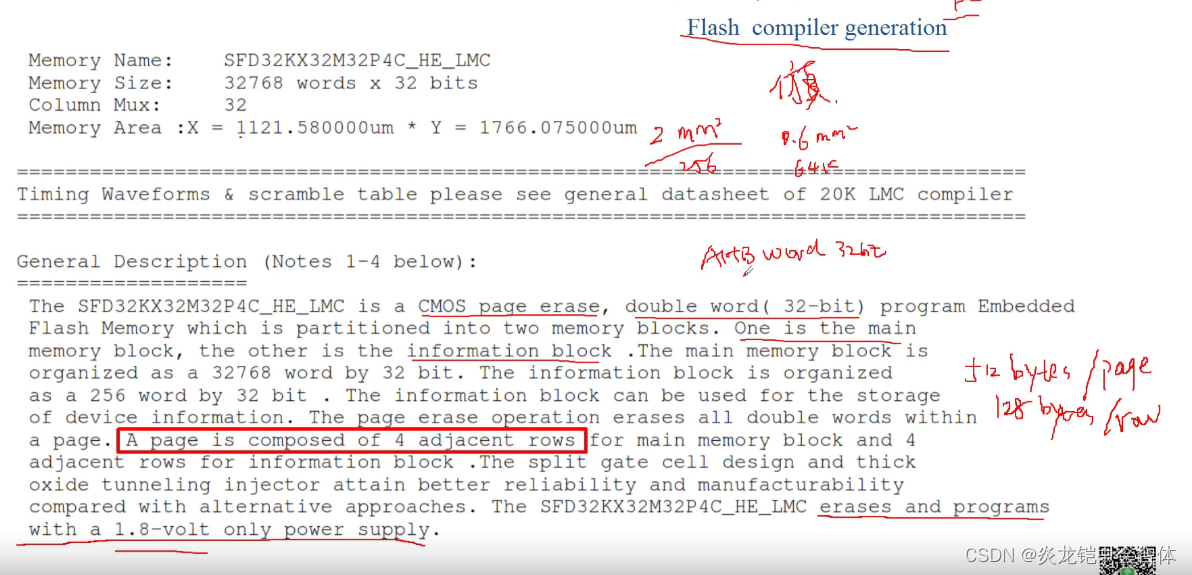

flash

① 由代工厂提供;

② 提供各种文件(仿真、时序),一般不提供 GDS ,需要在工厂做 merge;

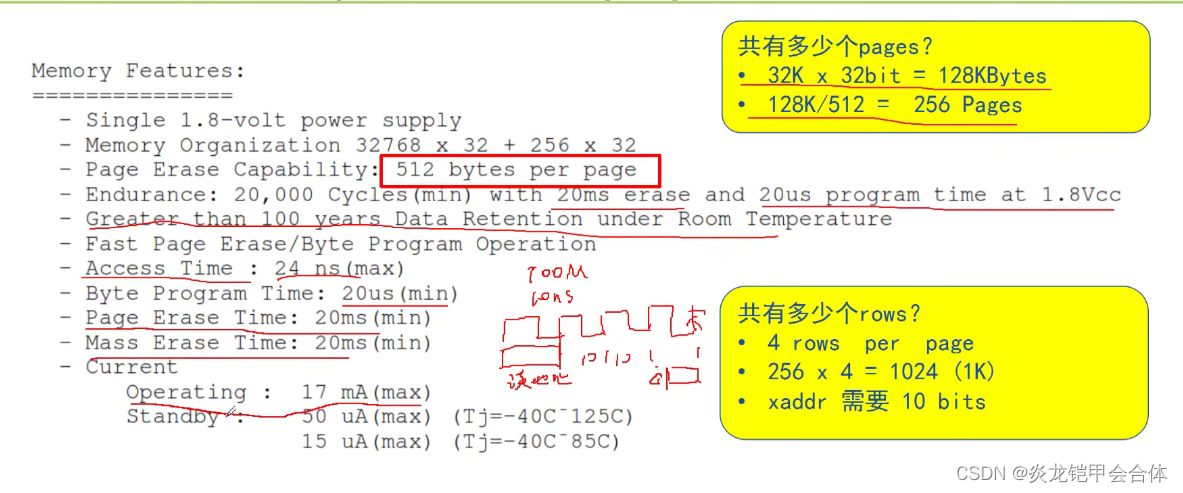

③ 32K * 32 bit(32 K * 8 byte = 128 Kbyte) 256 page(512 bytes / page)

④ 两片 flash 串联(共 256 KBytes)

面积

1121.58 um * 1766.075 um ≈ 2 ㎜²

功耗:

注意:没有clk,所以时钟需要自己生成

二 、 flash spec 【读相关文档得到】

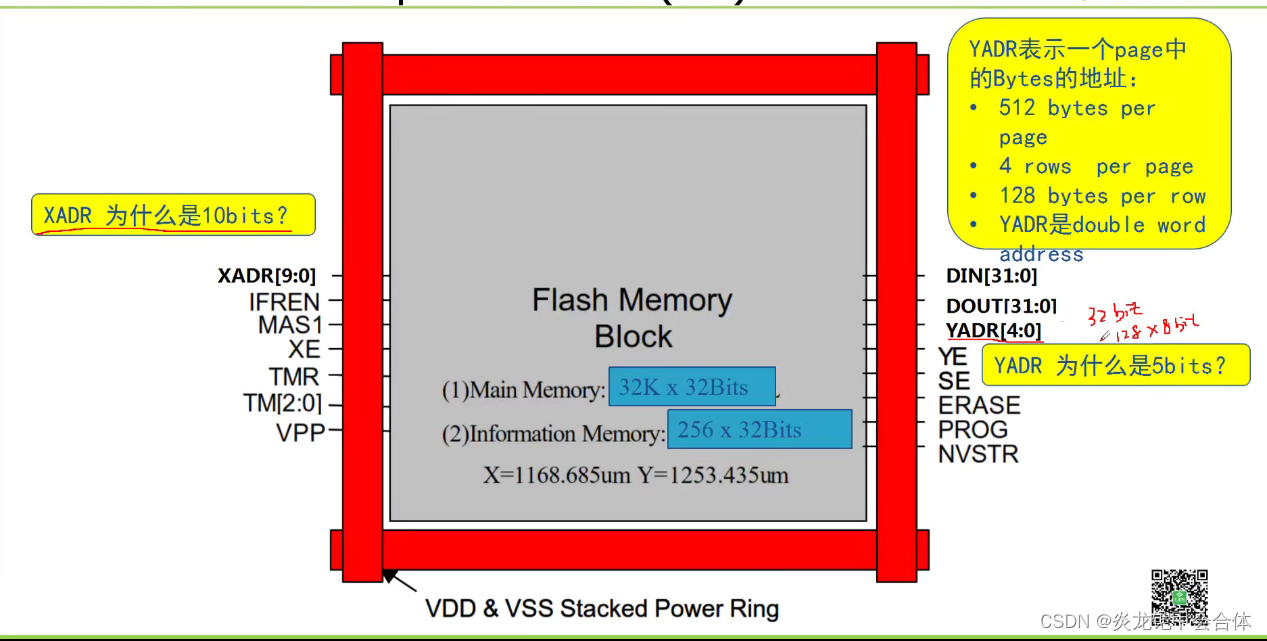

2.1 信号

| 名称 | I/O | 描述 |

|---|---|---|

| XADR[9:0] | I | 寻址的是行,10bit,低两位表示page中的哪一行,[9:2] 表示选择的page ,[1:0] 表示选择page 中的哪一行; |

| YADR[4:0] | I | 一行中有32个dw ,所以使用 5 bit【dw : double word】 |

| DIN[31:0] | I | 写数据 |

| DOUT[31:0] | O | 输出数据(读数据) |

| XE | I | x 地址有效,当XE = 1 时,XADR是有效的 |

| YE | I | y 地址有效,当 YE =1 时,YADR 是有效的 |

| SE | I | 灵敏放大器的使能信号,读数据的时候,读某行某列中存储单元的数据,存储在晶体管中,驱动能力不够,需要灵敏放大器,将信号读到的数据送到输出端 |

| IFREN | I | 1:表示访问 information block ;0:表示访问 main block;通常设置为1 |

| ERASE | I | 按页擦除 |

| MAS1 | I | 按块擦除 |

| PROG | I | 数据写入,程序烧录 |

| NVSTR | I | 非易失性操作 |

| VDD | I | 电源 |

| VSS | I | 地 |

一片 flash :32K * 32 bits = 1024 Kbits = 128K Bytes;

每页 512 byte ,一共是256 页

每页 4 行,一共1K 行, XADR 需要 10 bits

每行 32 列 , 一行是 128 bytes

地址映射:

首先将memory分成page,page分成row,row分成double word

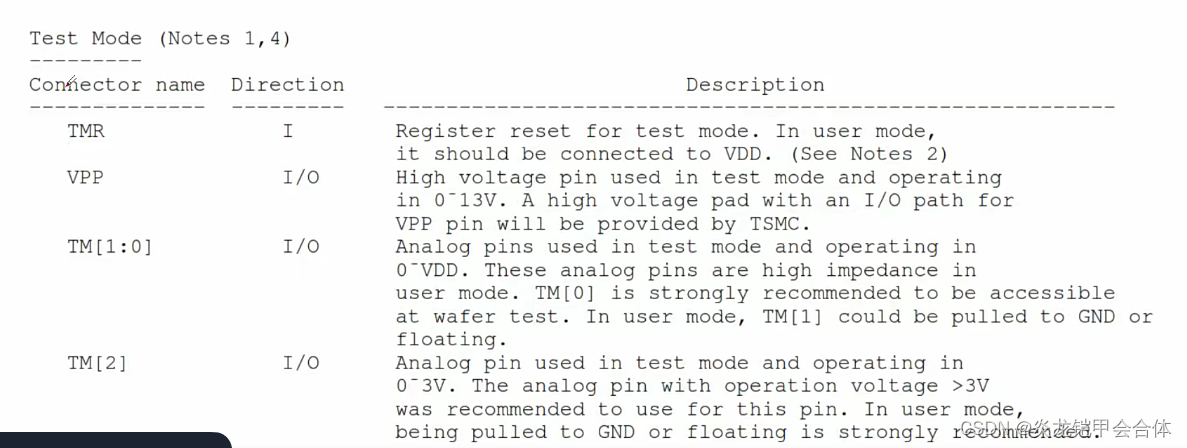

2.2 测试信号

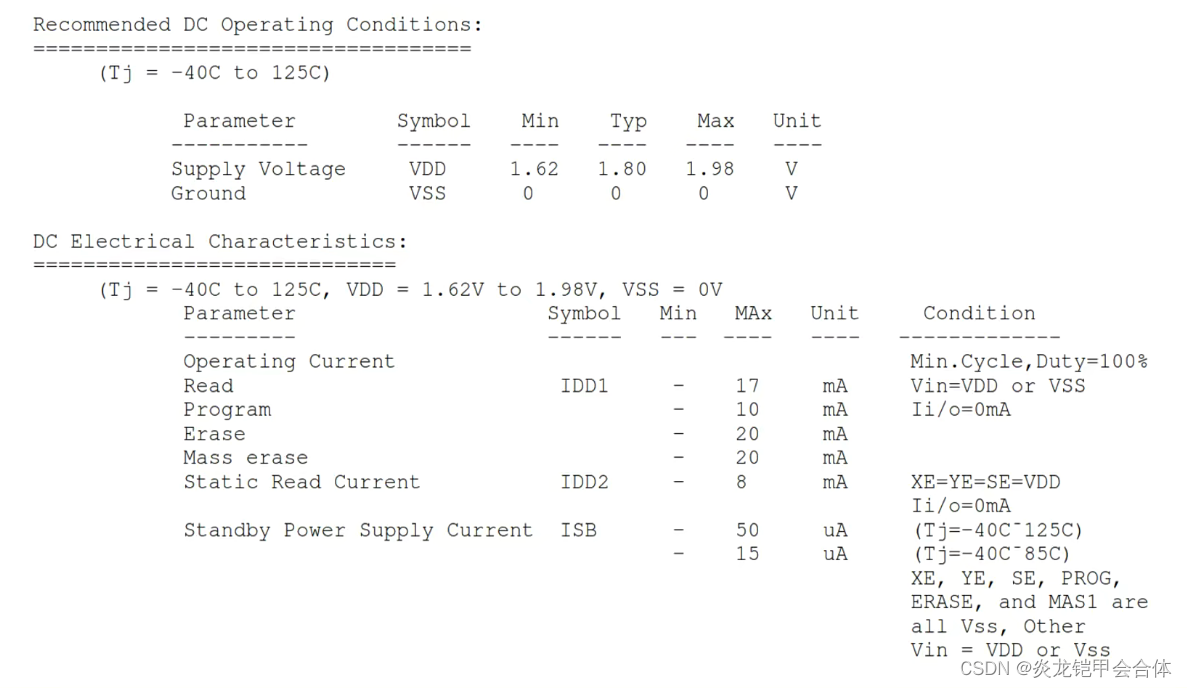

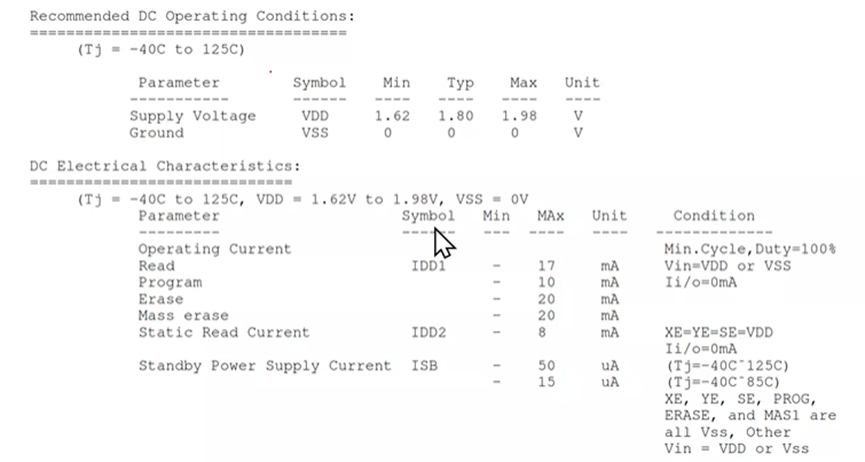

2.3 电流、电压

① Standby的时候,电流以微安形式存在,在工作状态下的时候,电流以毫安形式存在,在不同的模式下,电流相差一个数量级。不同情况下,电流不同,功耗不同

② SRAM是一维的寻址,eFlash是二维地址

③ Word是多少位的(32位或者是16位),是根据不同的系统确定的

2.4 读写擦信号

真值表:

| MODE | XE | YE | SE | PROG | ERASE | MAS1 | NVSTR |

|---|---|---|---|---|---|---|---|

| Standby | L | L | L | L | L | L | L |

| Read | H | H | H | L | L | L | L |

| Program | H | H | L | H | L | L | H |

| Page Erase | H | L | L | L | H | L | H |

| Mass Erase | H | L | L | L | H | H | H |

IFREN 真值表

| Mode | IFREN = 1 | IFREN = 0 |

|---|---|---|

| Read | 读取 information block | 读取main block |

| Program | Program information block | Program main block |

| Page erase | 对 information block 进行页擦 | 对 main block进行页擦 |

| Mass erase | 全擦除 【所有 block】 | 擦除 main block |

test mode

| Mode | PROG | ERASE | YE | XE | IFREN | MAS1 |

|---|---|---|---|---|---|---|

| Test mode 1 | L | L | H | L | L | H |

| Test mode 2 | L | L | H | L | H | L |

| Test mode 3 | L | H | H | H | L | L |

【Test mode信号主要通过基台进行测试,不需要进行内建自测试】

2.5 时序参数

| 参数 | symbol | min | max | Unit |

|---|---|---|---|---|

| Access time of read cycle | Tacc | - | 24 | ns |

| 读时序的数据保持时间 | Tdh | 0 | - | ns |

| PROG/ERASE to NVSTR 的建立时间 | Tnvs | 5 | - | us |

| NVSTR 的保持时间 | Tnvh | 5 | - | us |

| NVSTR 的保持时间( 在块擦除的时候) | Tnvh1 | 100 | - | us |

| NVSTR to program 的建立时间 | Tpgs | 10 | - | us |

| program 的保持时间 | Tpgh | 20 | - | ns |

| Program 的时间 | Tprog | 20 | 40 | us |

| address / data 建立时间 | Tads | 20 | - | ns |

| address / data 保持时间 | Tadh | 20 | - | ns |

| 保留时间 | Trcv | 1 | - | us |

| Cumulative program HV period (1) | Thv | - | 4 | ms |

| 擦除时间 | Terase | 20 | 40 | ms |

| 块擦除时间 | Tme | 20 | 40 | ms |

2.6 时序图

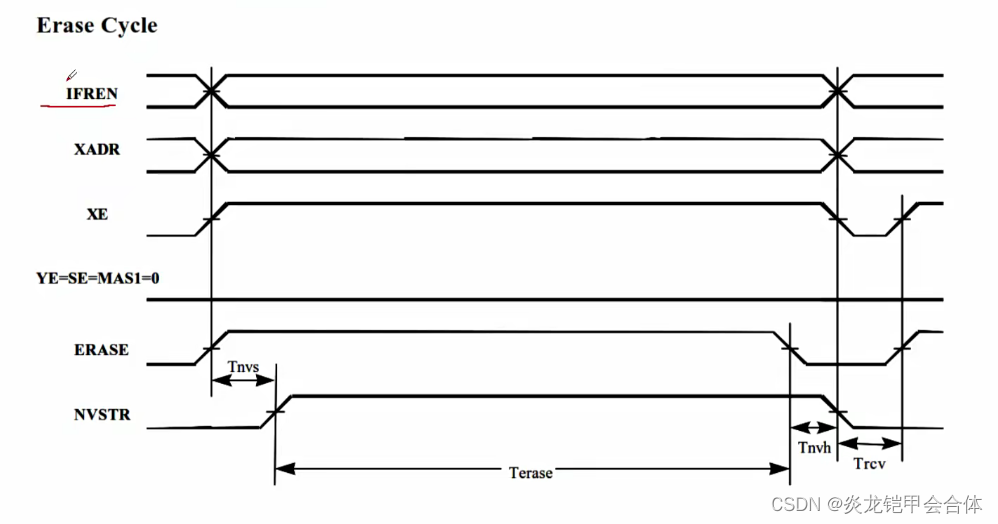

1)页擦除时序图

页擦状态过程描述:

① IFREN = 0 表示对 main block进行页擦,IFREN = 1 表示对 information block 进行页擦;

② XADR 进行配置;并将 XE、ERASE 信号拉高 ;

③ YE , SE , MAS1 信号始终为低;

④ 在ERASE 信号保持 Tnvs = 5 us (至少)之后,将NVSTR 信号拉高;

⑤ 保持各自的状态 持续 Terase = 20 ~ 40 ms 的时间,将 ERASE 信号拉低

⑥ ERASE 信号拉低后,保持 Tnvh = 5 us (至少)之后,XADR 信号进行一次变换;同时将NVSTR , XE ,信号拉低,并维持Trcv = 1 us(至少) 的时间。

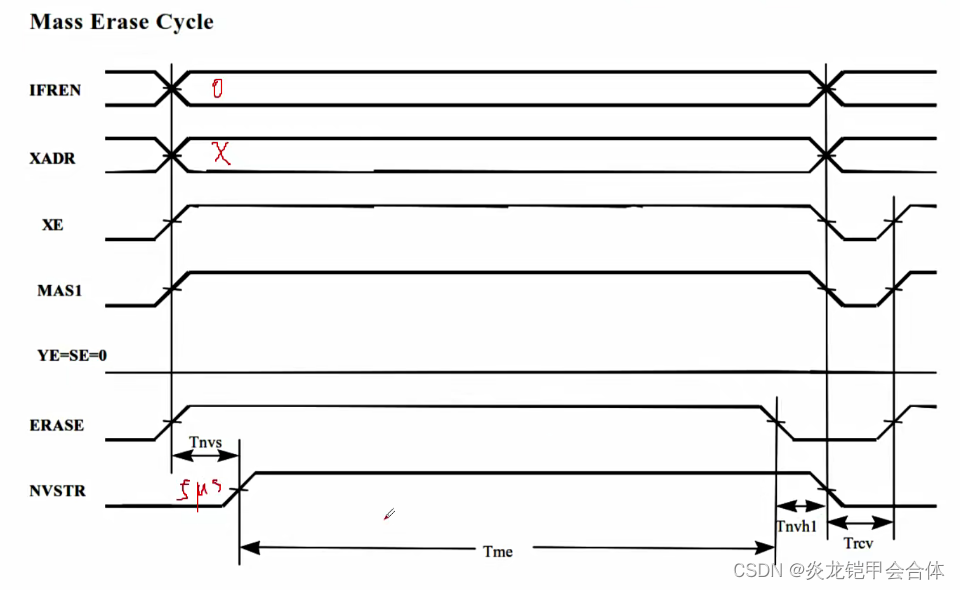

2)块擦除时序图

块擦除状态过程描述:

① IFREN = 0 表示对 main block进行块擦,IFREN = 1 表示对全部 block 进行块擦;

② XADR 进行配置;并将 XE、ERASE 、MAS1 信号拉高 ;

③ YE , SE 信号始终为低;

④ 在ERASE 信号保持 Tnvs = 5 us (至少)之后,将NVSTR 信号拉高;

⑤ 保持各自的状态 持续 Tme = 20 ~ 40 ms 的时间,将 ERASE 信号拉低;

⑥ ERASE 信号拉低后,保持 Tnvh1 = 100 us (至少)之后,XADR 信号进行一次变换;同时将NVSTR , XE , MAS1 信号拉低,并维持Trcv = 1 us(至少) 的时间后,进入下一个状态;

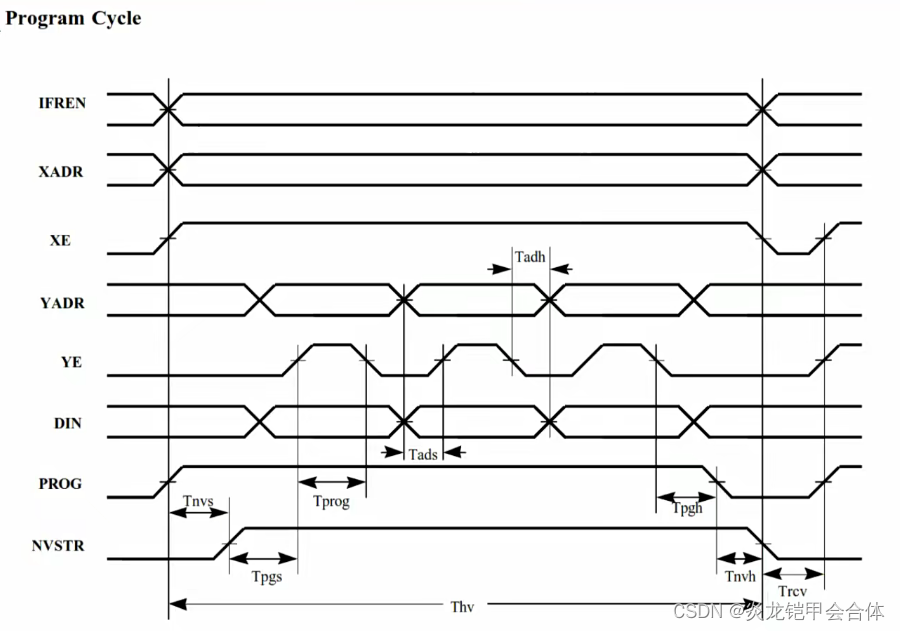

3)写时序图

写状态过程描述:

① IFREN = 0 表示对 main block进行写操作,IFREN = 1 表示对information block 进行写操作;

② XADR 进行配置;并将 XE 、PROG 信号拉高 ,YE 信号拉低 ;

③ 在PROG 信号保持 Tnvs = 5 us (至少)之后,将NVSTR 信号拉高;

④ 在 NVSTR 信号拉高 Tpgs = 10 us (至少)之后,将 YE 信号拉高;

⑤ 将YE 信号拉高 Tprog = 20 ~ 40 us 的时间后,将 YE 信号拉低;

⑥ 在 YE 信号拉高之前,需要将 YADR 信号和 DIN 信号至少保持 Tads = 20ns (至少)的时间,【为了满足建立时间】;

在YE 信号拉低之后,需要将 YADR 信号和 DIN 信号至少保持 Tadh = 20 ns (至少)的时间,【为了满足保持时间】。

⑦ 每次写入一笔数据都需要将 YE 信号拉高一次,并保持 Tprog = 20 ~ 40 us ;【图中 DIN 连续写入了三笔数据 】

⑧ 在写入最后一笔数据之后,YE 信号拉低,并保持 Tpgh = 20 ns (至少)的时间后,将 PROG 信号拉低;

⑨ 在 PROG 信号拉低之后,保持 Tnvh = 5us (至少)的时间后,将 NVSTR 信号和 XE 信号拉低,将IFREN 信号和 XADR 信号进行一次变换。

⑩ 在所有信号维持上述状态 Trcv = 1 us(至少) 的时间后,进入下一个状态;

【注意,写操作时,XE 信号拉高的时间 Thv = 4ms (最多)】

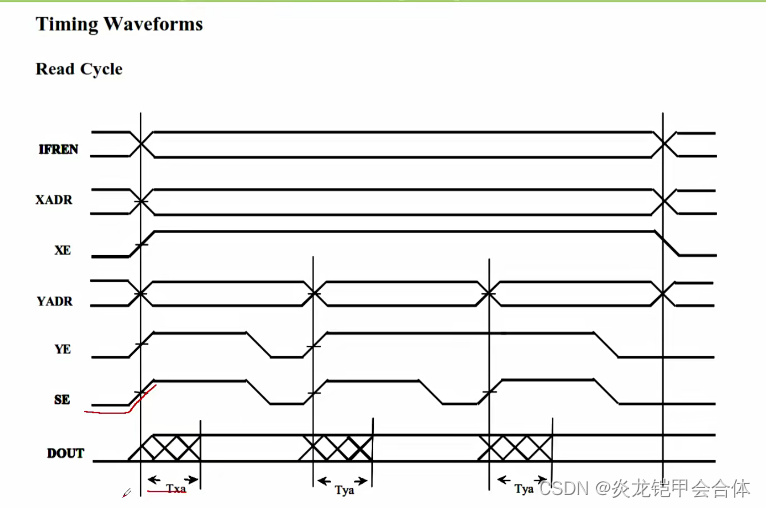

4)读时序图

读状态过程描述:

① IFREN = 0 表示对 main block进行写操作,IFREN = 1 表示对information block 进行写操作;

② XADR 、YADR 进行配置;并将 XE 、SE 、YE 信号拉高 ;

③ 当 XE 信号拉高之后,保持 Txa = Tacc = 24 ns (最多)的时间之后,读取 DOUT 中的数据;【读时序的保持时间 Tdh = 0 ns (至少,最大值未规定)】

④ 每次读取数据, 需要将 SE 信号变化一次。

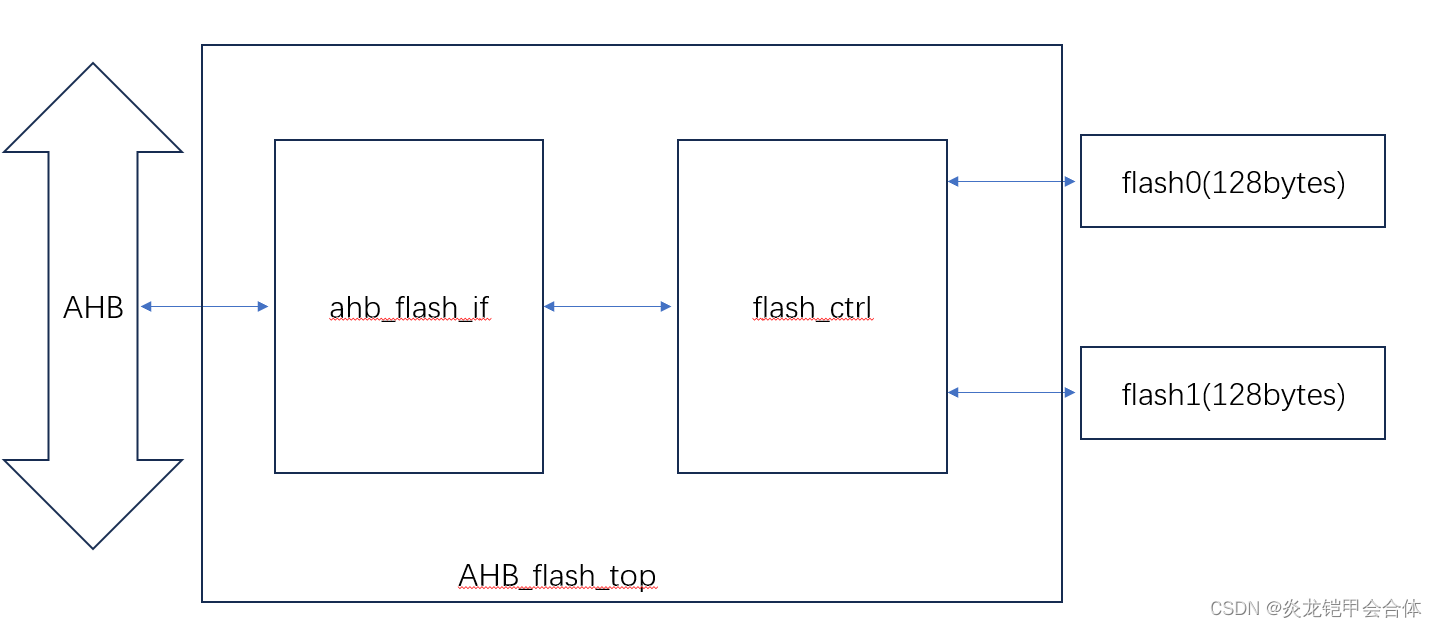

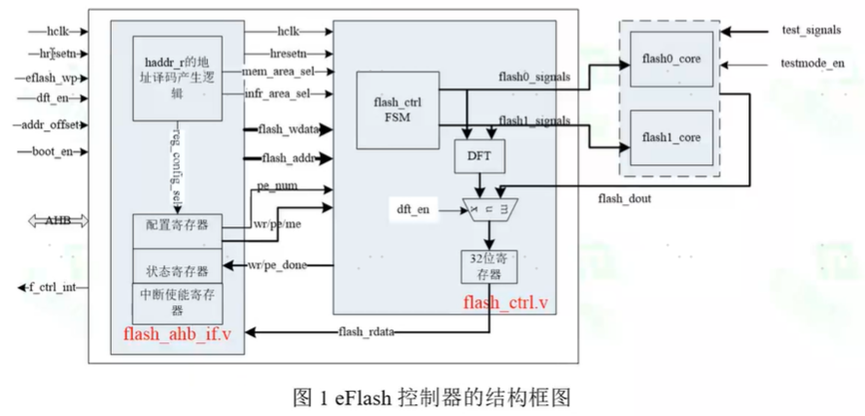

三 、eflash 控制器的架构设计

3.1 整体框图

3.2 eflash 功能列表

① 支持32 位的 AHB slave interface;

② 支持 eflash 多周期的读、写、页擦操作(两块独立的eflash 串联封装,256KByte);

③ eflash 操作可配置(时序、功能);

④ 支持 eflash 中的 boot 区空间的擦写保护;

⑤ 支持 DFT 功能;

3.3 eflash 控制器软硬件模块划分

软件部分:

① eflash 控制器的驱动;

② 对读写擦的时序进行配置;

硬件部分:

① 实现 amba 2.0 接口;

② 实现 eflash 控制器接口时序;

3.4 各个模块分析

3.4.1 顶层模块

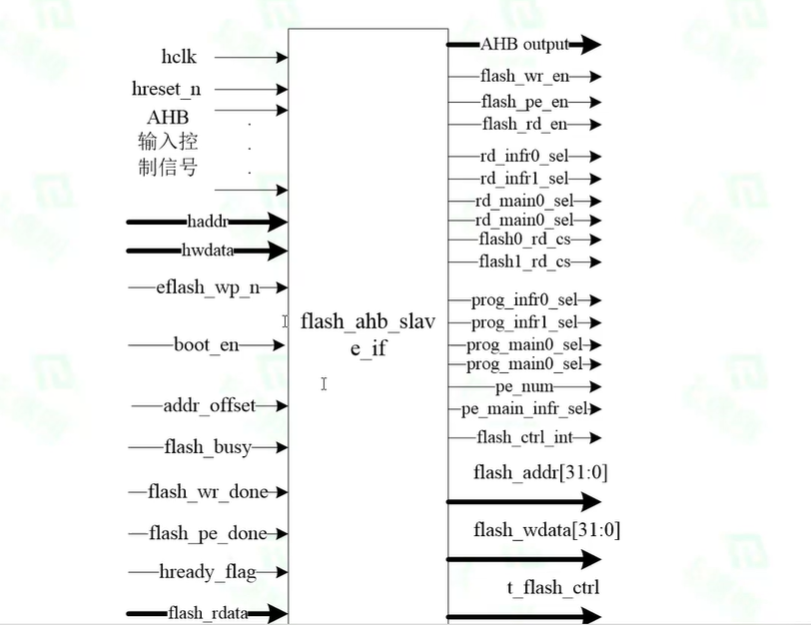

顶层模块包含两部分内容,一部分是ahb_flash_if 模块,另一部分是flash_ctrl 模块;

① ahb_flash_if 模块:接收AHB总线控制信号,地址信号和数据信号;将地址译码转化成flash地址;配置控制寄存器以配合flash_ctrl模块的控制操作;并且储存flash工作状态到状态寄存器供软件可查。

② flash_ctrl 模块:接收总线地址和命令,完成Flsh的读、写、和擦除操作。

信号描述:

| 信号 | I/O | width | from | to | 描述 |

|---|---|---|---|---|---|

| hclk | I | 1 | clock source | AHB BUS clock | |

| hresetn | input | 1 | reset controller | AHB bus reset signal | |

| hsel | input | 1 | decoder | slave selected signal | |

| hready_in | input | 1 | other slave | high:bus is ready to use | |

| hwrite | input | 1 | Master | High:wrte; Low:read | |

| hsize | input | [2:0] | Master | transfer size: 8/16/32 Max:1024 | |

| htrans | input | [2:0] | Master | 传输类型:NONSEQ、SEQ、IDLE、BUSY | |

| hburst | input | [1:0] | Master | 8种 singal incr beat4/8/16 ,wrap4/8/16 | |

| hwdata | input | [31:0] | Master | write data | |

| haddr | input | [31:0] | Master | AHB bus address | |

| eflash_wp_n | input | 1 | efalsh write protect enable | ||

| dft_en | input | 1 | DFT enable | ||

| boot_en | input | 1 | boot area enable | ||

| addr_offset | input | [4:0] | address offset | ||

| flash0_dout_in | input | [31:0] | flash0 read data out | ||

| flash1_dout_in | input | [31:0] | flash1 read data out | ||

| hready_out | output | 1 | Master | slave has finished transfer | |

| hresp | output | [1:0] | Master | OKEY、ERROR、RETRY、SPLIT | |

| hrdata | output | [31:0] | Master | AHB bus read data | |

| flash_ctrl_int | output | 1 | Flash | falsh control interrupt signal when program done or pe done | |

| flash0_infr_en | output | 1 | Flash | flash0 infromation block enable(IFREN) | |

| flash0_xaddr_en | output | 1 | Flash | falsh0 xaddress enable(XE) | |

| flash0_yaddr_en | output | 1 | Flash | falsh0 yaddress enable(YE) | |

| flash0_se_en | output | 1 | Flash | falsh0 SA enable(SE) | |

| flash0_prog_en | output | 1 | Flash | falsh0 progaram enable(PROG) | |

| flash0_nvstr_en | output | 1 | Flash | falsh0 non-volatile store cycle enable(NVSTR) | |

| flash0_erase_en | output | 1 | Flash | flash0 erase enable(ERASE) | |

| flash0_mass_en | output | 1 | Flash | flash0 mass erase enable(MAS1) | |

| flash0_xaddr | output | [9:0] | Flash | flash0 x address(XADR) | |

| flash0_yaddr | output | [4:0] | Flash | flash0 y address(YADR) | |

| flash0_wdata | output | [31:0] | Flash | flash0 write data(DIN) | |

| flash1_infr_en | output | 1 | Flash | flash1 infromation block enable(IFREN) | |

| flash1_xaddr_en | output | 1 | Flash | falsh1 xaddress enable(XE) | |

| flash1_yaddr_en | output | 1 | Flash | falsh1 yaddress enable(YE) | |

| flash1_se_en | output | 1 | Flash | falsh1 SA enable(SE) | |

| flash1_prog_en | output | 1 | Flash | falsh1 progaram enable(PROG) | |

| flash1_nvstr_en | output | 1 | Flash | falsh1 non-volatile store cycle enable(NVSTR) | |

| flash0_erase_en | output | 1 | Flash | flash1 erase enable(ERASE) | |

| flash1_mass_en | output | 1 | Flash | flash1 mass erase enable(MAS1) | |

| flash1_xaddr | output | [9:0] | Flash | flash1 x address(XADR) | |

| flash1_yaddr | output | [4:0] | Flash | flash1 y address(YADR) | |

| flash1_wdata | output | [31:0] | Flash | flash1 write data(DIN) |

3.4.2 ahb_flash_if 模块

信号描述

| 信号 | I/O | width | 描述 |

|---|---|---|---|

| hclk, | input | 1 | clock source AHB bus clock |

| hresetn, | input | 1 | reset controller AHB bus reset signal |

| hsel, | input | 1 | decoder slave selected signal |

| hready_in, | input | 1 | other slave high:bus is ready to use |

| hwrite, | input | 1 | Master High:wrte; Low:read |

| hsize, | input | [2:0] | Master transfer size: 8/16/32 Max:1024 |

| htrans, | input | [2:0] | Master 传输类型:NONSEQ、SEQ、IDLE、BUSY |

| hburst, | input | [1:0] | Master 8种 singal incr beat4/8/16 ,wrap4/8/16 |

| hwdata, | input | [31:0] | Master write data |

| haddr | input | [31:0] | Master AHB bus address |

| flash_rdata | input | [31:0] | flash_ctrl flash read out data |

| flash_prog_done | input | 1 | flash_ctrl flash program has finished |

| flash_busy | input | 1 | flash is busy |

| eflash_wp_n, | input | 1 | efalsh write protect enable |

| addr_offset | input | [4:0] | boot area address offset |

| boot_en | input | 1 | boot area enable |

| hready_flag | input | 1 | slave has finished transfer,transfer to hready_out |

| hready_out | output | 1 | this slave to BUS siganl |

| hresp | output | [1:0] | OK 、ERROR、SPLIT、RETRY |

| hrdata | output | [31:0] | flash read data or register value |

| flash_prog_en | output | 1 | flash program enable |

| flash_pe_en | output | 1 | flash page erase enable |

| flash_rd_en | output | 1 | flash read enable |

| rd_inf0_sel | output | 1 | information0 area read select |

| rd_inf1_sel | output | 1 | information1 area read select |

| rd_main0_sel | output | 1 | main0 area read select |

| rd_main1_sel | output | 1 | main1 area read select |

| flash0_rd_cs | output | 1 | flash0 read selcet |

| flash1_rd_cs | output | 1 | flash0 read selcet |

| prog_infrarea0_sel | output | 1 | information0 area program select |

| prog_infrarea1_sel | output | 1 | information1 area program select |

| prog_mainarea0_sel | output | 1 | main0 area program select |

| prog_mainarea1_sel | output | 1 | main1 area program select |

| pe_num, | output | [8:0] | page number |

| pe_main_infr_sel | output | 1 | page erase main or infromation area |

| flash_addr_out, | output | [14:0] | flash address |

| flash_wdata, | output | [31:0] | flash write data |

| flash_ctrl_int, | output | 1 | flash interrupt enable |

| t_nvstr_setup | output | [11:0] | PROG/ERASE to NVSTR set up time >5us |

| t_nvstr_hold | output | [11:0] | NVSTR hold time >5us |

| t_rcv | output | [7:0] | Recover time >1us |

| t_prog_setup | output | [15:0] | NVSTR to program set up time |

| t_prog_hold | output | [3:0] | Program hold time (20~40us) |

| t_addr_setup | output | [3:0] | Adress/data set up time |

| t_addr_hold | output | [3:0] | Adress/data hold time |

| t_prog_proc | output | [15:0] | program time |

| t_addr_aces | output | [7:0] | Access time of read cycle |

| t_page_erase | output | [23:0] | page erase time >20ms |

寄存器地址及功能描述:

| name | bits | Address Offset | Reset value | Definition |

|---|---|---|---|---|

| nvstr_setup_timing | [31:0] | 0x00 | 32‘h259 | 写/擦操到NVSTR的建立时间 |

| nvstr_hold_timing | [31:0] | 0x04 | 32‘h259 | 写/擦操到NVSTR的保持时间 |

| prog_setup_timing | [31:0] | 0x08 | 32‘h4b1 | 写操作建立时间 |

| progaddr_sethold_timing | [31:0] | 0x0c | 32‘h333 | 写操作地址建立、保持时间及写完成后的保持时间 |

| prog_proc_timing | [31:0] | 0x10 | 32‘h962 | 每次写操作完成的时间 |

| read_aces_timing | [31:0] | 0x14 | 32‘h5 | 读操作所需要的时间 |

| pe_timing | [31:0] | 0x18 | 32‘h0 | 页擦除所需要的时间(需配置) |

| rcv_timing | [31:0] | 0x1c | 32‘h79 | 恢复时间 |

| wr_en_r | [31:0] | 0x20 | 32‘h0 | Flash program使能 |

| pe_en_r | [31:0] | 0x24 | 32‘h0 | Flash 页擦使能 |

| pe_num_r | [31:0] | 0x28 | 9‘h1df | 页擦的数量 |

| pe_main_infr_sel_r | [31:0] | 0x2c | 32‘h0 | 页擦main区还是information区选择 |

| prog_addr_r | [31:0] | 0x30 | 32‘h0 | program 地址 |

| prog_data_r | [31:0] | 0x34 | 32‘h0 | program 数据 |

| int_en_r | [31:0] | 0x38 | - | 中断使能 |

| flash_status_r | [31:0] | 0x3c | - | flash 状态寄存器 |

| boot_error_r | [31:0] | 0x40 | - | boot 操作出错标记寄存器 |

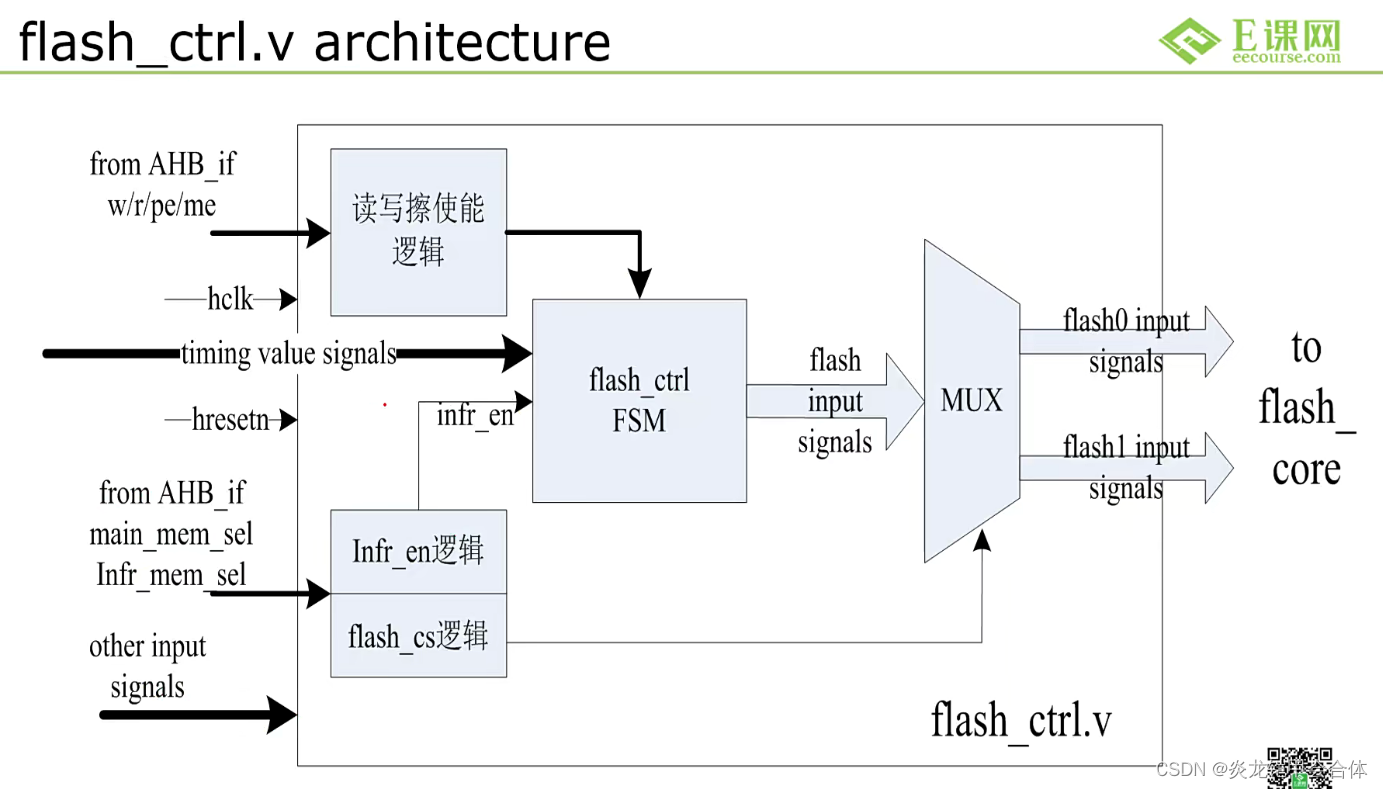

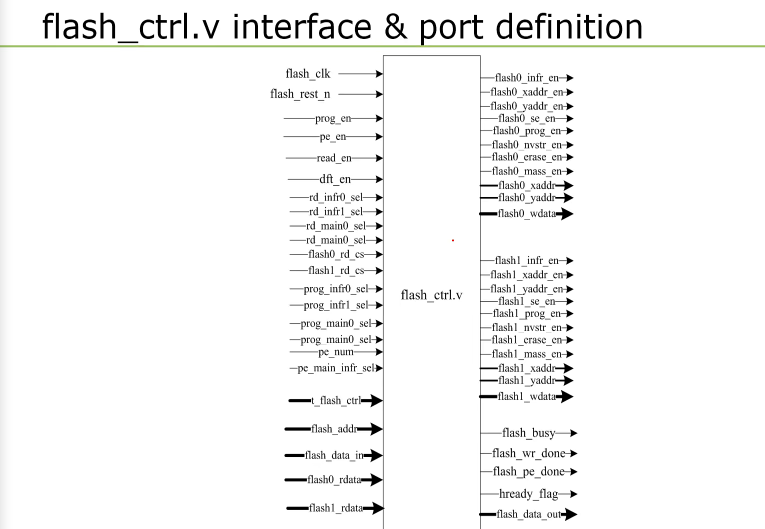

3.4.3 flash_ctrl 模块

信号描述

| Signals | I/O | Width | form | to | 描述 |

|---|---|---|---|---|---|

| flash_clk | input | 1 | clock source | AHB bus clock | |

| flash_rst_n | input | 1 | reset controller | AHB bus reset signal | |

| prog_en | input | 1 | flash_ahb_slave_if | flash program enable | |

| pe_en | input | 1 | flash_ahb_slave_if | flash page erase enable | |

| read_en | input | 1 | flash_ahb_slave_if | flash read enable | |

| rd_inf0_sel | input | 1 | flash_ahb_slave_if | information0 area read select | |

| rd_inf1_sel | input | 1 | flash_ahb_slave_if | information1 area read select | |

| rd_main0_sel | input | 1 | flash_ahb_slave_if | main0 area read select | |

| rd_main1_sel | input | 1 | flash_ahb_slave_if | main1 area read select | |

| flash0_rd_cs | input | 1 | flash_ahb_slave_if | flash0 read selcet | |

| flash1_rd_cs | input | 1 | flash_ahb_slave_if | flash0 read selcet | |

| prog_infrarea0_sel | input | 1 | flash_ahb_slave_if | information0 area program select | |

| prog_infrarea1_sel | input | 1 | flash_ahb_slave_if | information1 area program select | |

| prog_mainarea0_sel | input | 1 | flash_ahb_slave_if | main0 area program select | |

| prog_mainarea1_sel | input | 1 | flash_ahb_slave_if | main1 area program select | |

| pe_num, | input | [8:0] | flash_ahb_slave_if | page number | |

| pe_main_infr_sel | input | 1 | flash_ahb_slave_if | page erase main or infromation area | |

| flash_addr | input | [14:0] | flash_ahb_slave_if | flash address | |

| flash_data_in | input | [31:0] | flash_ahb_slave_if | flash write data | |

| flash0_rdata | input | [31:0] | flash_ahb_slave_if | flash0 read data | |

| flash1_rdata | input | [31:0] | flash_ahb_slave_if | flash1 read data | |

| flash_ctrl_int, | input | 1 | flash_ahb_slave_if | flash interrupt signal(op finish) | |

| nvstr_set_timing | input | [11:0] | flash_ahb_slave_if | PROG/ERASE to NVSTR set up time >5us | |

| nvstr_hold_timing | input | [11:0] | flash_ahb_slave_if | ||

| rcv_timing | input | [7:0] | flash_ahb_slave_if | Recover tim |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?