上篇文章给诸位道友们已经分享了板材的DF值的一些使用说明情况了,这期文章小编主要讲解的是第二个知识点-------板材的DK值的使用说明了,诸位搬好小椅子稳住啊,小编我开始发功了。

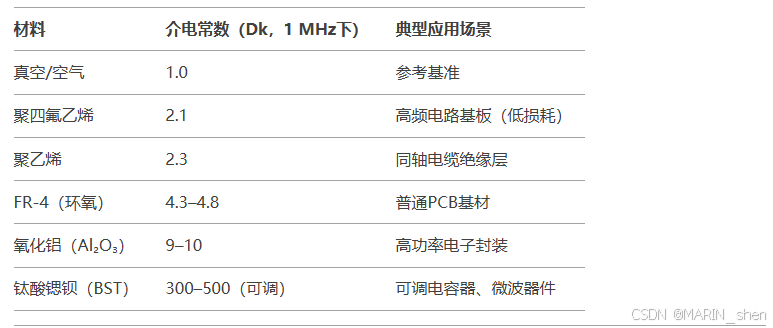

介电常数(Dielectric Constant,Dk),又称相对介电常数(Relative Permittivity),是描述材料在电场中极化能力的物理量。以下是关于介电常数的详细解析:

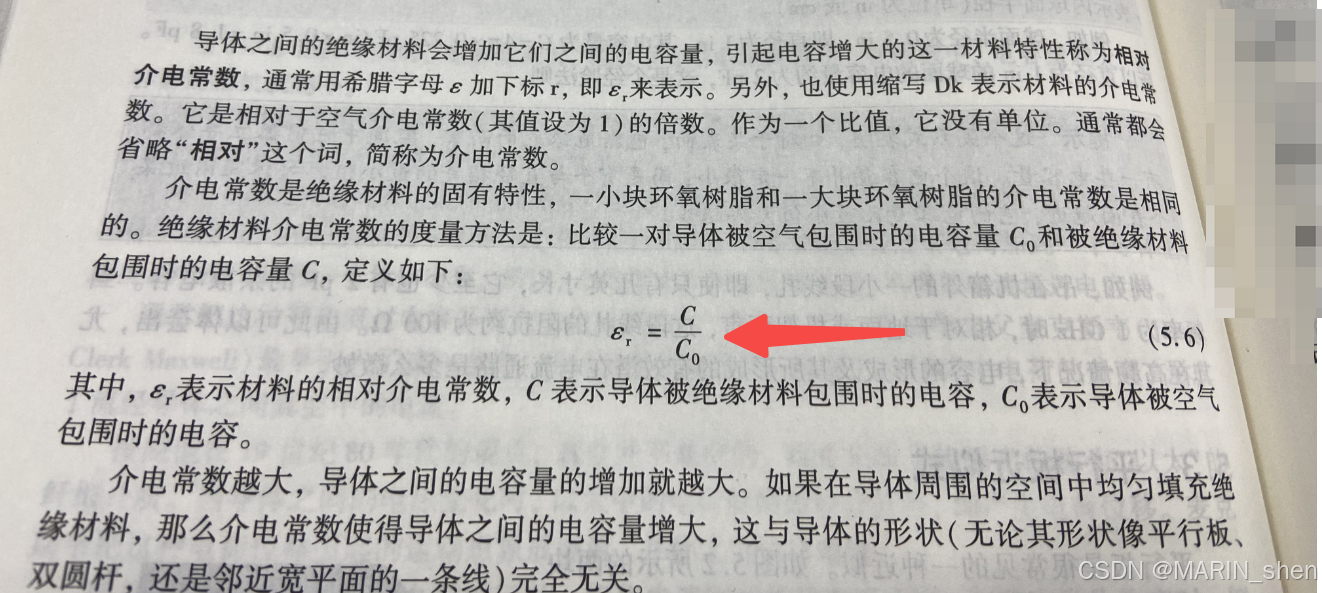

1. 定义与公式:

-

基本定义:介电常数表示材料在外加电场中储存电能的能力,定义为材料中电场的电容率(ε)与真空电容率(ε0)的比值:

公式:Dk=ε/ε0 -

其中,真空的介电常数 Dk=1。

-

物理意义:

-

Dk>1:材料会削弱电场强度(极化电荷抵消部分外加电场)。

-

Dk 越大,材料储存电能的能力越强(如电容器中的介质)。

-

2. 关键特性:

-

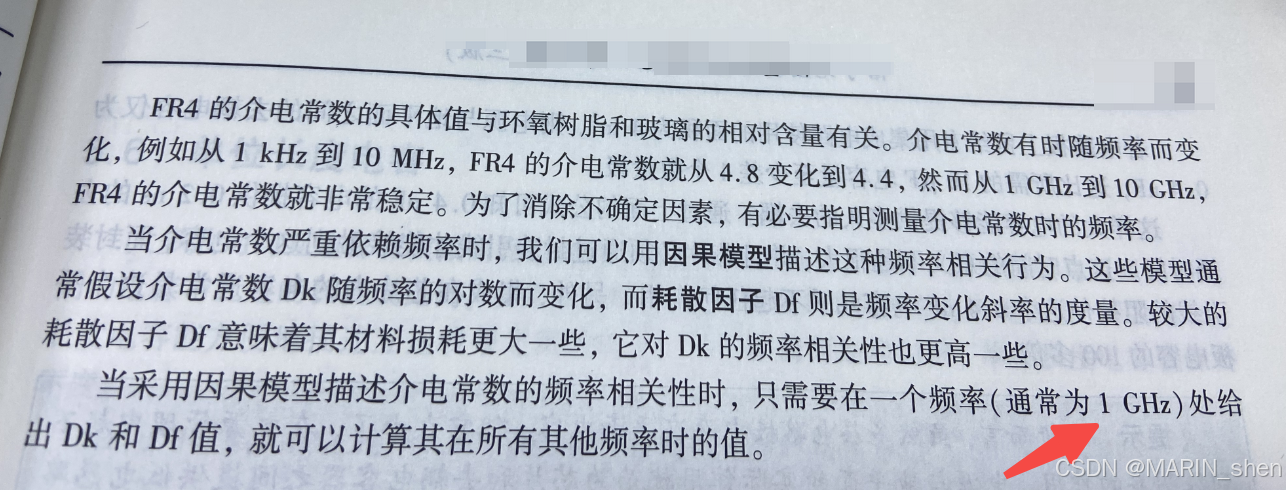

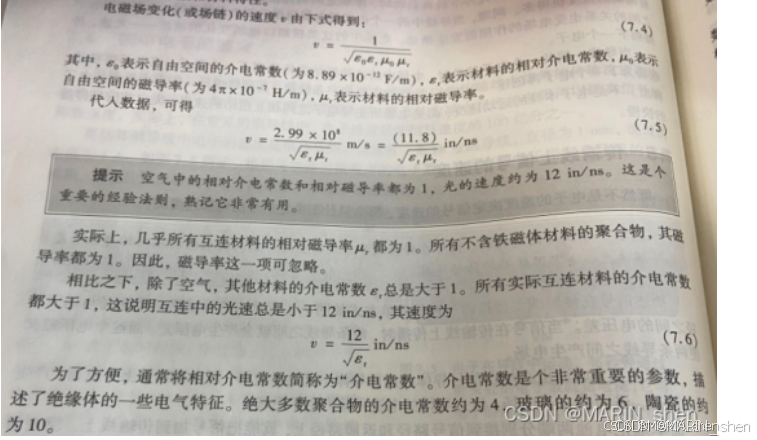

频率依赖性:

介电常数随电场频率变化(介电色散)。高频下,材料极化可能无法跟上电场变化,导致 Dk值降低(如微波频段的材料特性变化)。

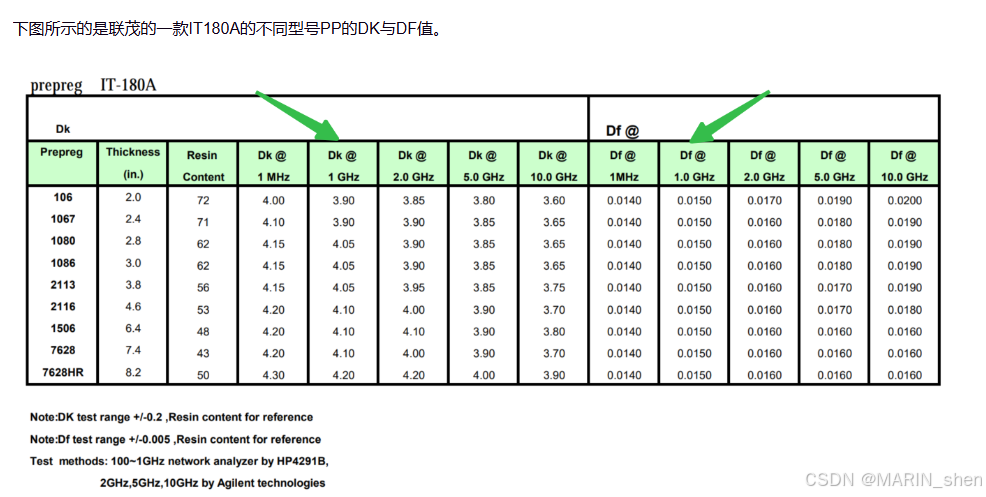

所以说我们一般拿到板厂给的板材的规格书的时候,通常是看信号在1GHZ的处的DK以及DF值的大小代入到我们单板的层叠中去的。

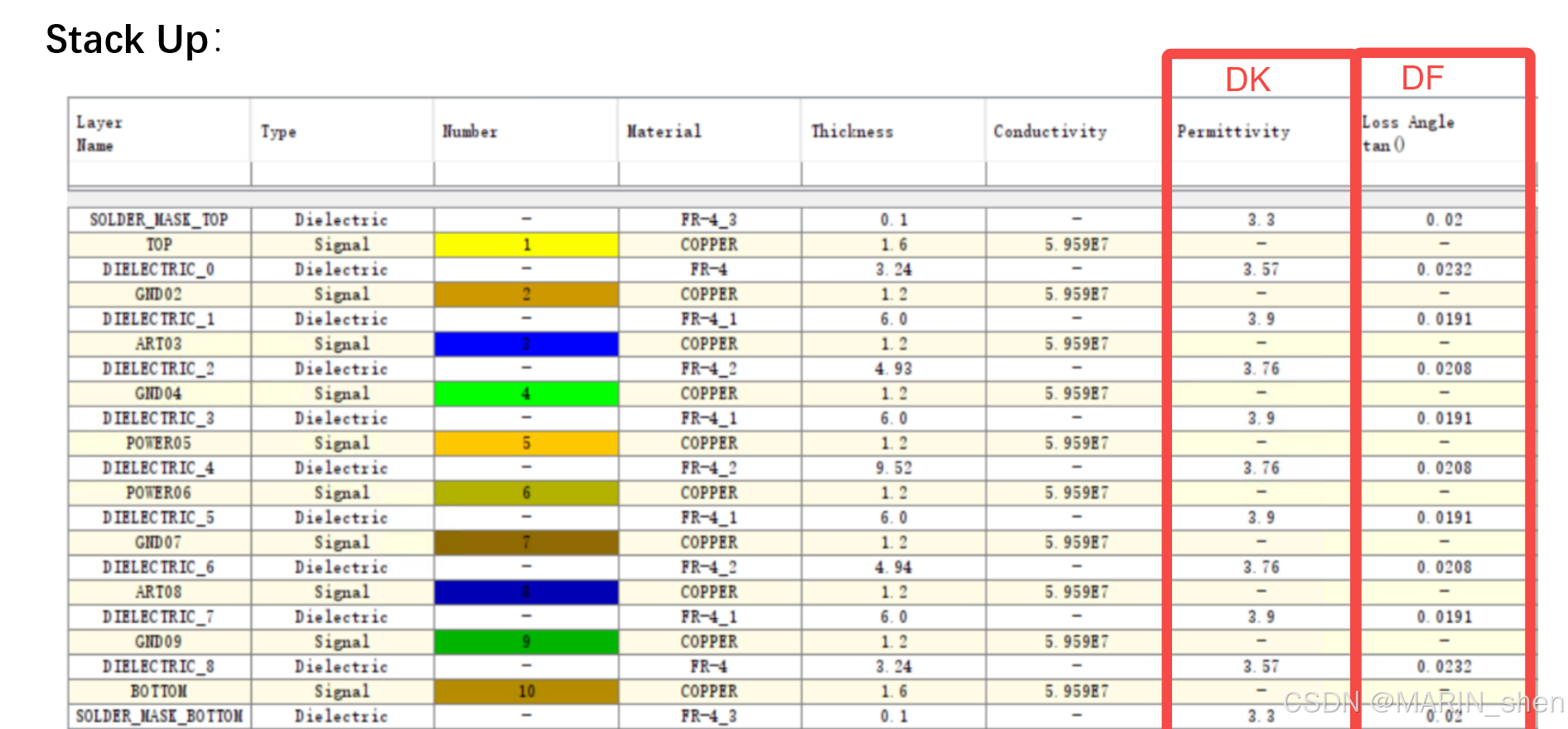

我们在做单板高速信号的仿真的时候需要代入单板的层叠结构,有的时候你们公司规模很大很有钱的时候,需要板厂那边提供啥资料的时候,板厂那边的态度是立马就给反馈的,一般不会超过半天的,什么板材的数值,铜箔的粗糙度,DF值的大小,DK值的大小等。

要是道友们所在宗门的江湖地位一般的话,估计你们对接那些板厂回复的消息就没有那么快了,不过这个这都是可以理解的嘛,毕竟江湖不是打打杀杀的,是人情世故啊。

3. 应用领域

-

电子电路设计:

-

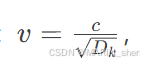

信号传播速度:

低 Dk 材料(如PTFE)用于高频高速信号传输(如5G、雷达)。一般来Dk值越小越好,传输速度越快,传输延时越小,对高速信号越好。

低 Dk 材料(如PTFE)用于高频高速信号传输(如5G、雷达)。一般来Dk值越小越好,传输速度越快,传输延时越小,对高速信号越好。

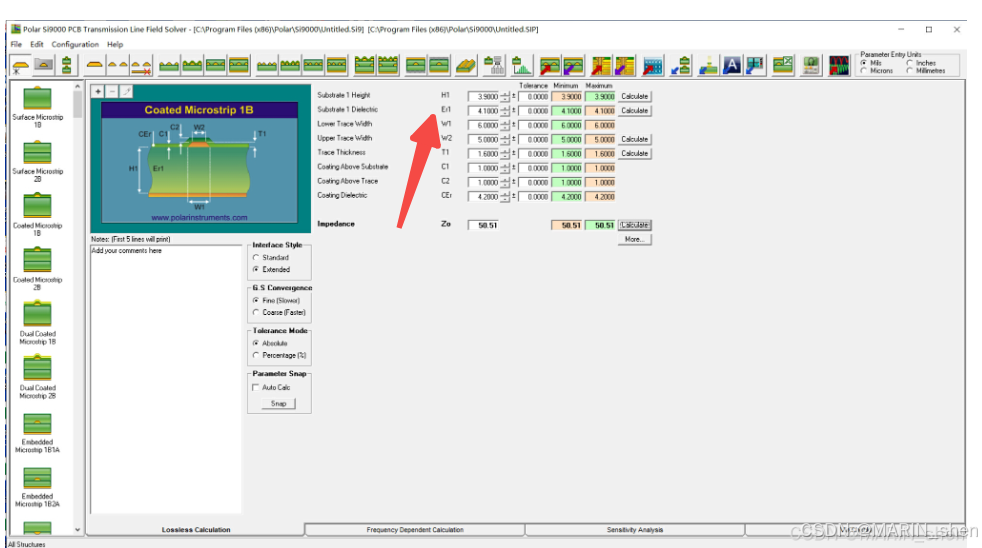

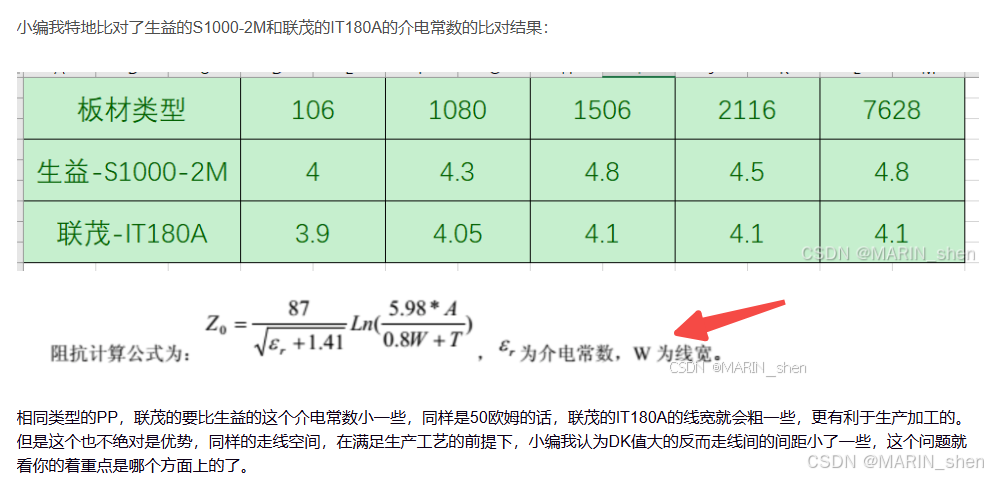

其实这个板材的DK值也就是我们经常算阻抗的( Polar -SI9000软件计算阻抗值)时候用到的ER值的大小,其中DK值即软件中的ER值是和信号的阻抗值成反比的,

- 阻抗匹配:传输线(微带线、带状线)的几何尺寸设计需结合 Dk。这个数值小编我之前的一篇文章的也有所提及到的:

我们在做PCB设计的时候其实主要关注板材DK的影响主要就是上面两个点了,一个是信号的阻抗数值相关联的,一个是影响到信号的传播速度了。

-

电容器:

-

高 Dk材料(如陶瓷)可减小电容器体积(如MLCC)。

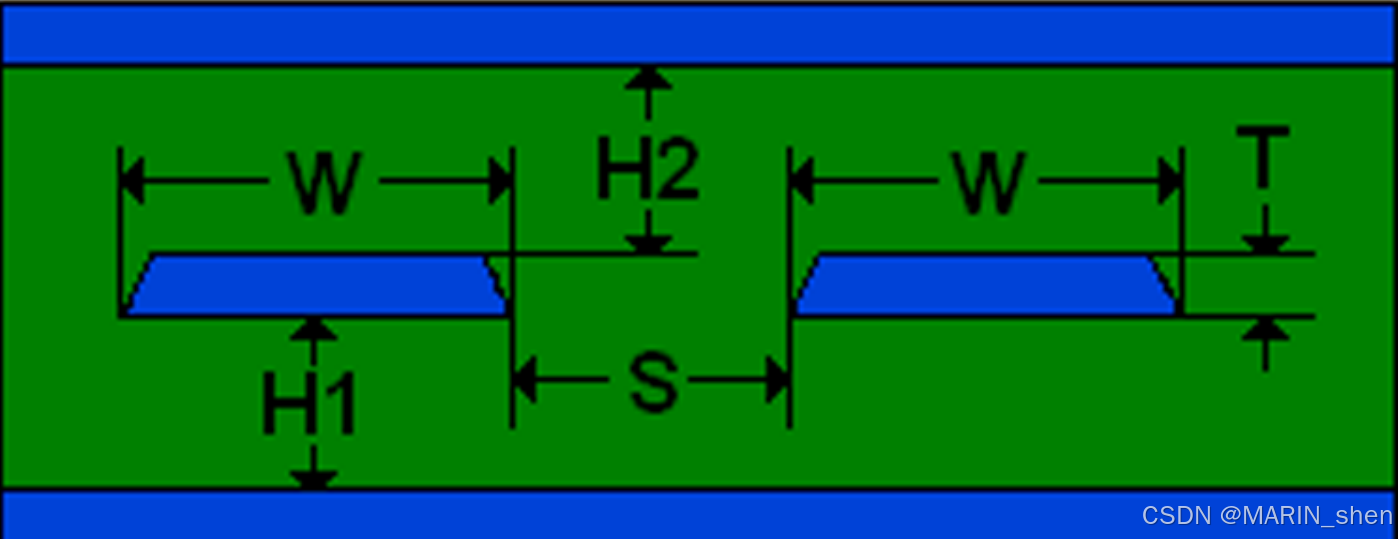

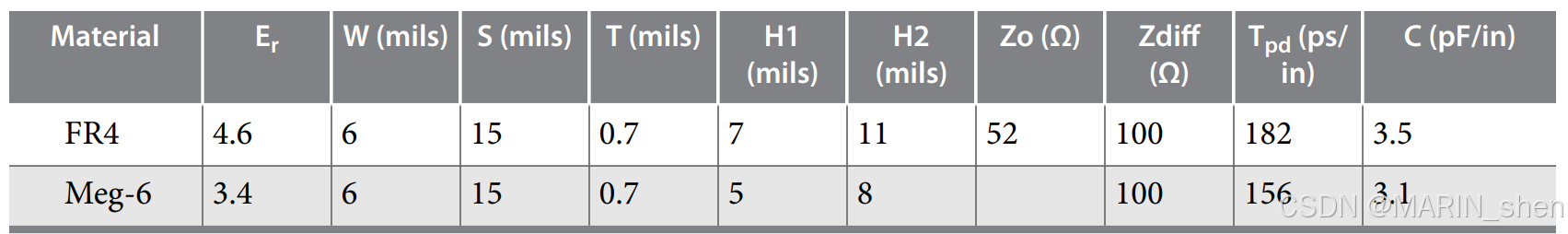

还有一个就是高速板材由于RE值比较小,同样的线宽,阻抗数值,可以满足更小的层叠结构。例如下所示是两个不同板材保持同样的阻抗100欧姆,差分线的走线轨迹(线宽W,组内间距S)是一样的,Stripline Differential Trace(内层带状线)结构:

一般来说减小Ɛr影响传输线有两种方式:

A:迹线阻抗随着r的减小而增加导致反射,进一步降低信号质量。

B:信号速度随着r的减小而增加导致不同谐波的分散,包括数字信号。这导致接收器处的相位抖动加

如果道友们想要更加详细的关于板材的DK值一些公式参数啥的可以去关注小编的一个乌克兰前同事,他之前也有分享过这个知识点的,只是他是从仿真的角度去切入看这个数值的影响,小编我是从一个PCB设计者的角度去分析的。

如何理解介电常数与耗散因子![]() https://my-signal.blog.youkuaiyun.com/article/details/136308482

https://my-signal.blog.youkuaiyun.com/article/details/136308482

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!

1030

1030

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?