1、Verilog书写基本格式

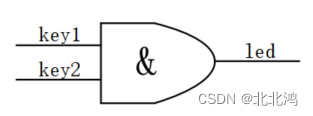

功能:与输入

功能模块代码如下(示例):

module key_ctrl_led ( //模块module名和文件名保持一致,module与endmodule一致

input wire key1, //输入input一定都是线型wire的,默认位宽为1,此处不用标明位宽

input wire key2, //第二个输入信号,加逗号连接

output wire led //输出output,三个信号,最后一个信号不加逗号。output类型可以是wire也可以是reg型

);

//1&1=1 1&0=0 0&1=0 0&0=0 //与的真值表

assign led = key1&key2; //assign是对线型语句的输出变量赋值

endmodule

重点知识:

1、输入Input一定都是线型wire的,输出output可以wire也可以reg

2、输入输出是针对模块写的

3、信号名称是唯一的(如key1、key2、led)

assign相当于连线,一般是将一个变量的值不间断地赋值给另一个变量,就像把这两个变量连在一起,所以习惯性的当做连线用,比如把一个模块的输出给另一个模块当输入。

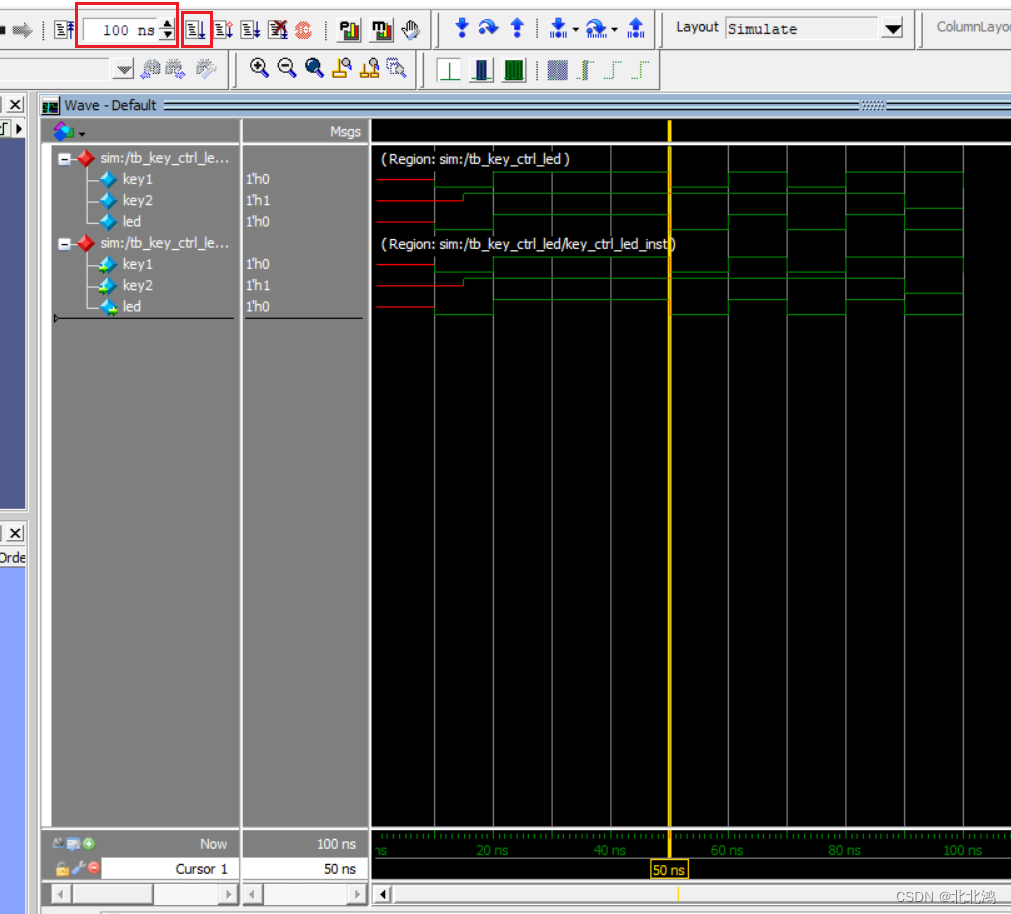

Testbench 测试激励 :给功能模块的key1、key2信号源,然后查看led信号是否正确

不可综合:不可以真正下载到FPGA

仿真激励模块代码如下(示例):

`timescale 1ns/1ns //`timescale 表示的是时标,后面的表示单位/精度

//#10,比如要用到延时功能,#10代表延时10ns。不能10.1,除非精度改成100ps=0.1ns。

module tb_key_ctrl_led();//此测试模块不需要定义端口

reg key1;//内部变量只需要定义变量类型和名称,不需要定义方向

reg key2;//变量类型定义只与变量的赋值方式有关

wire led;

//always 是一种赋值方式, #10 表示延时 10 个时间单位

//每过10ns,key阻塞赋值

always #10 key1 = {$random};

//$random 是一个随机函数,可以用来取一个随机数, {}是取绝对值

always #15 key2 = {$random};

//例化被测试模块,两个模块之间的信号传递的唯一方式

key_ctrl_led key_ctrl_led_inst(

.key1(key1),

.key2(key2),

.led(led)

);

endmodule

重点知识:

timescale 1ns/1ns //timescale 表示的是时标,后面的表示单位/精度

//#10,比如要用到延时功能,#10代表延时10ns。不能10.1,除非精度改成100ps=0.1ns。

1、reg在always语句下编程

2、例化模块内部的输出,括号内是wire变量。

例化模块内部的输入,括号内既可以是wire也可以reg。

3、.key1(key1),“.”后面的key1是功能模块中的,括号里的key1是仿真激励模块中的

4、$random函数调用时,返回一个32位的随机数,它是一个带符号的整形数

结果

本文介绍了Verilog语言中模块的基本书写格式,包括输入输出的定义,以及使用assign进行信号赋值。在测试激励方面,讲解了如何创建仿真模块,使用timescale设置时标,并通过always语句实现信号的延迟和随机赋值。此外,还强调了模块例化以及测试过程中信号的连接方式。

本文介绍了Verilog语言中模块的基本书写格式,包括输入输出的定义,以及使用assign进行信号赋值。在测试激励方面,讲解了如何创建仿真模块,使用timescale设置时标,并通过always语句实现信号的延迟和随机赋值。此外,还强调了模块例化以及测试过程中信号的连接方式。

1070

1070

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?