1.原理

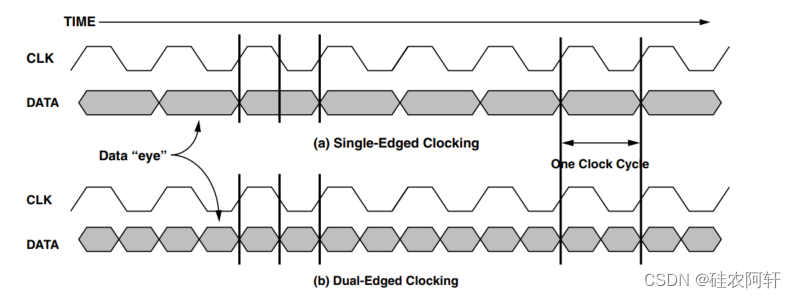

DDR(double data rate SDRAM)中的数据是双边沿传输,即在时钟的上升和下降沿都可以采样,它和单边沿传输的SDRAM(即SDR,single data rate SDRAM)的区别如下图,图中的data eye即数据的两次传输之间围成的区域,图(a)为SDR的传输示意图,因为只有一个时钟沿传输数据,所以称为single-edged clocking,图(b)为DDR的传输示意图,因为是两个时钟沿传输数据,所以称为dual-edged clocking。

在SDR中,data eye是由两个同向时钟沿围成的(在图中即为在时钟上升沿,发送端驱动数据),中间还会有一个反向时钟沿,在该反向时钟沿的时刻(在图中即为下降沿)数据是稳定的,所以该反向时钟沿可以用来在接受端采样数据。简而言之就是每个data eye有两个可用时钟沿,左边的上升沿用于发送端驱动数据,中间的下降沿用于接收端采样数据,而右边的时钟沿就属于下一个data eye了。

而在DDR中,data eye是由紧邻的两个反相时钟沿围成,每个data eye可用的时钟沿个数减半(即只有一个),这个时钟沿只能用于驱动或采样数据,而无法把两件任务都完成。因此必须引入另一种机制来弥补这一缺陷,这一机制就是DQS(data strobe signal),它被称为同步时序参考信号( source-synchronous timing reference signal)。

2.DQS的通用方法

下图是读操作的时序图,DQS由DRAM产生并送给controller,DQS和DQ都和clock的边沿对齐(edge aligned),controller将DQS delay 90°(需要额外的delay电路),delay后的DQS边沿和DQ的中心对齐(centere-aligned),可以用来采样稳定的数据。

本文详细介绍了DDR(SDR)内存的工作原理,重点阐述了DDR如何通过双沿触发提高数据传输效率,并解释了DQS(数据 strobe 信号)在读写操作中的作用,以及在LPDDR5中引入WCK和RDQS以优化数据同步和传输的机制。此外,还提及了高速接口设计中减少信号不确定性的重要性。

本文详细介绍了DDR(SDR)内存的工作原理,重点阐述了DDR如何通过双沿触发提高数据传输效率,并解释了DQS(数据 strobe 信号)在读写操作中的作用,以及在LPDDR5中引入WCK和RDQS以优化数据同步和传输的机制。此外,还提及了高速接口设计中减少信号不确定性的重要性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2800

2800

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?