rk3576 适配 PCIE

RK3576 是瑞芯微(Rockchip)推出的一款 ARM 架构的 SoC(系统级芯片),广泛应用于多种嵌入式设备,特别是用于开发和运行具有较高性能要求的应用。RK3576 的 PCIe(Peripheral Component Interconnect Express)功能模块是其重要组成部分之一,它允许与其他硬件设备进行高速通信。

RK3576 支持 PCIe 2.1 版本,并提供了多通道支持。一般来说,PCIe 2.1 的最大理论带宽为 5 GT/s(千兆传输每秒)。具体的带宽会根据设备所支持的通道数(x1、x2)有所不同。

- x1 通道:每通道带宽 500 MB/s

- x2 通道:每通道带宽 1 GB/s

RK3576 的 PCIe 模块能够与各种设备接口进行连接,包括:

SSD(固态硬盘):PCIe NVMe SSD 提供更高的读写性能。

网络适配器:如 10GbE 网卡等。

GPU 或其他加速卡:如果需要图形或计算加速,PCIe 提供了低延迟和高带宽的接口。

外部扩展卡:如 USB 3.0/3.1 控制器、音频卡等。

作者:炭烤毛蛋 ,点击博主了解更多。

提示: 为了充分利用 RK3576 的 PCIe 功能,软件层面需要相应的驱动支持。

文章目录

1. rk3576 Pcie部分的原理图

-

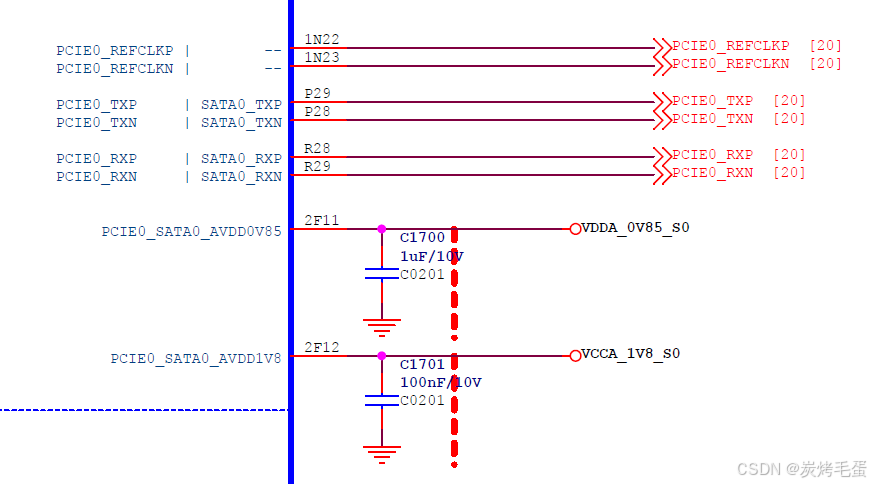

SATA HPY供电

SATA 与 PCIe2.0复用关系,模块上电相同。与 PCIe对比没有不再使用时钟源。

PCIe 2.0 需要供电 VCCA_1V8和VDDA_0V9,STAT 接口也是相同。 -

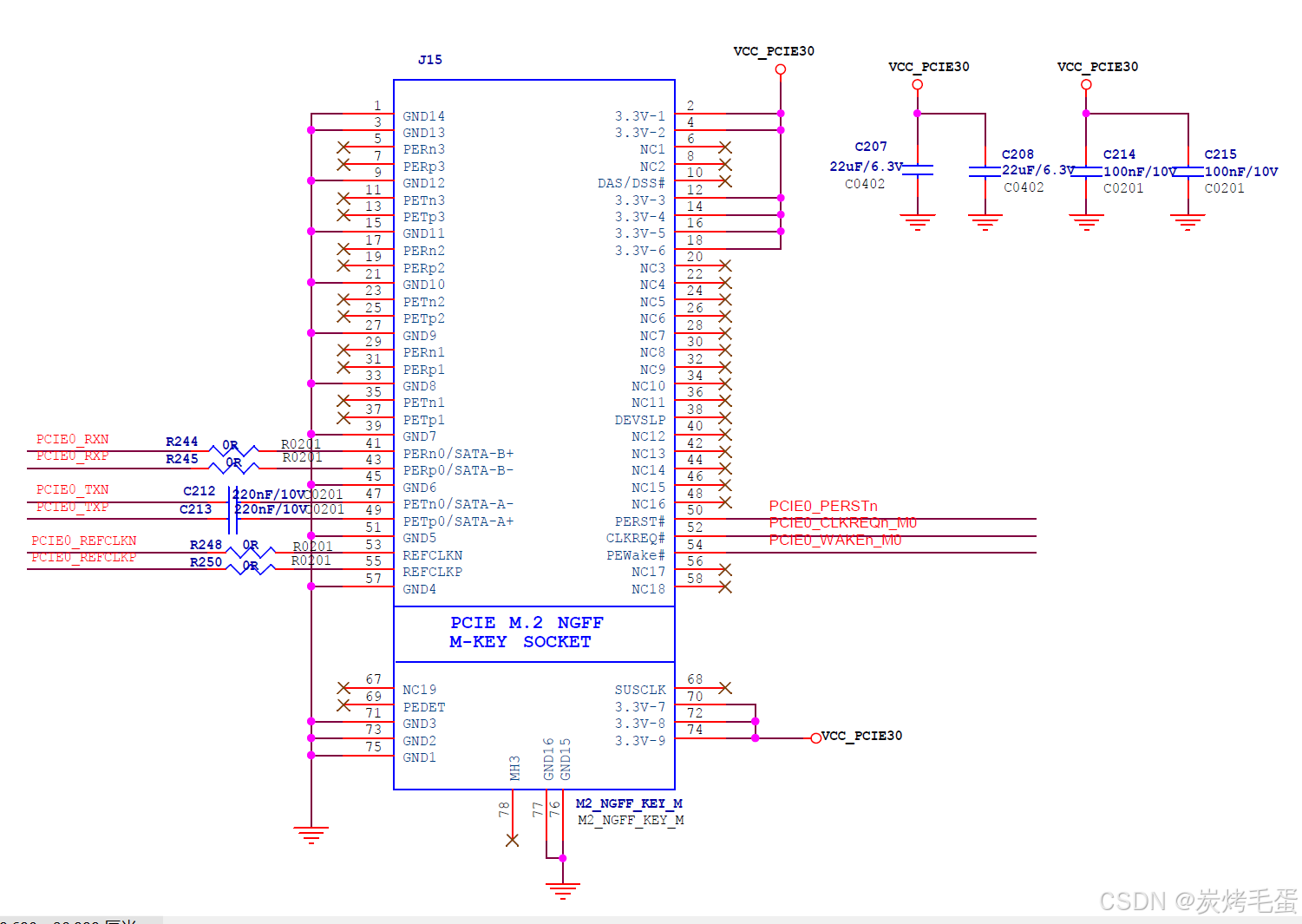

SATA 连接 M2-MKEY

-

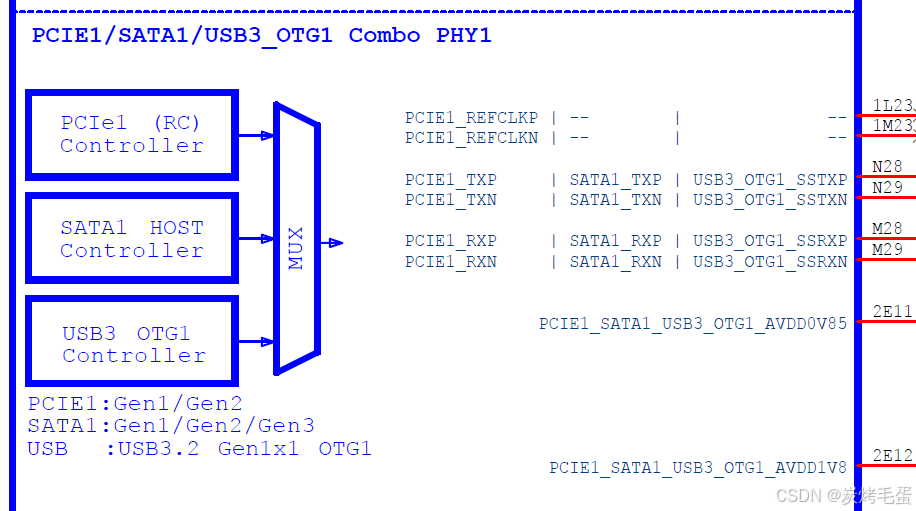

SATA1

SATA1 与 PCIe2.0_1、USB3_OTG1复用关系,模块上电相同。

2. rk3576 Pcie 内核匹配

rk3576 内核正常加载pcie外设,需要pcie相关总线驱动正常编译构建,然后加载过程SOC启动时根据平台总线加载外设。

2.1 rk3576 Pcie 内核配置

如果未见pci加载过程,很大概率是驱动未正常编译到。按照如下列表注意核查。

CONFIG_GENERIC_MSI_IRQ=y

CONFIG_GENERIC_MSI_IRQ_DOMAIN=y

CONFIG_IRQ_DOMAIN=y

CONFIG_IRQ_DOMAIN_HIERARCHY=y

CONFIG_PCI=y

CONFIG_PCI_DOMAINS=y

CONFIG_PCI_DOMAINS_GENERIC=y

CONFIG_PCI_SYSCALL=y

CONFIG_PCI_BUS_ADDR_T_64BIT=y

CONFIG_PCI_MSI=y

CONFIG_PCI_MSI_IRQ_DOMAIN=y

CONFIG_PHY_ROCKCHIP_SNPS_PCIE3=y

CONFIG_PHY_ROCKCHIP_NANENG_COMBO_PHY=y

CONFIG_PCIE_DW=y

CONFIG_PCIE_DW_HOST=y

CONFIG_PCIE_DW_ROCKCHIP=y

CONFIG_PCIEPORTBUS=y

CONFIG_PCIE_PME=y

2.2 内核设备树

rk3576 pcie 2.0 RC模式,无需外部晶体。两组pcie2.0分立运行,互不干扰。

- rk3576 pcie0 DTS

/ {

vcc3v3_pcie0: vcc3v3-pcie0 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie0";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpios = <&gpio0 RK_PC7 GPIO_ACTIVE_HIGH>;

startup-delay-us = <5000>;

vin-supply = <&vcc12v_dcin>;

};

};

&combphy0_ps {

status = "okay";

};

&pcie0 {

reset-gpios = <&gpio4 RK_PC7 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie0>;

status = "okay";

};

- rk3576 pcie1 DTS

/ {

vcc3v3_pcie1: vcc3v3-pcie1 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie1";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpios = <&gpio4 RK_PA3 GPIO_ACTIVE_HIGH>;

startup-delay-us = <5000>;

vin-supply = <&vcc12v_dcin>;

};

};

&combphy1_psu {

status = "okay";

};

&pcie1 {

reset-gpios = <&gpio4 RK_PB2 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie1>;

status = "okay";

};

- pcie 总线未发现从设备

[ 1.775076] rk-pcie 2a200000.pcie: invalid prsnt-gpios property in node

[ 1.781172] rk-pcie 2a200000.pcie: max MSI vector is 32

[ 1.781221] rk-pcie 2a200000.pcie: host bridge /pcie@2a200000 ranges:

[ 1.781248] rk-pcie 2a200000.pcie: err 0x0020000000..0x00200fffff -> 0x0020000000

[ 1.781265] rk-pcie 2a200000.pcie: IO 0x0020100000..0x00201fffff -> 0x0020100000

[ 1.781283] rk-pcie 2a200000.pcie: MEM 0x0020200000..0x0020ffffff -> 0x0020200000

[ 1.781297] rk-pcie 2a200000.pcie: MEM 0x0900000000..0x097fffffff -> 0x0900000000

[ 1.781410] rk-pcie 2a200000.pcie: iATU unroll: enabled

[ 1.781420] rk-pcie 2a200000.pcie: iATU regions: 8 ob, 8 ib, align 64K, limit 8G

[ 1.983586] rk-pcie 2a200000.pcie: PCIe Linking... LTSSM is 0x3

[ 2.004613] rk-pcie 2a200000.pcie: PCIe Linking... LTSSM is 0x3

[ 2.083443] rk-pcie 2a200000.pcie: PCIe Link up, LTSSM is 0x130011

[ 2.083457] rk-pcie 2a200000.pcie: PCIe Gen.2 x1 link up

[ 2.083559] rk-pcie 2a200000.pcie: PCI host bridge to bus 0000:00

[ 2.116703] pcieport 0000:00:00.0: PME: Signaling with IRQ 73

- pcie 总线识别到 SSD

[ 1.774448] rk-pcie 2a200000.pcie: invalid prsnt-gpios property in node

[ 1.775465] rk-pcie 2a200000.pcie: max MSI vector is 32

[ 1.775512] rk-pcie 2a200000.pcie: host bridge /pcie@2a200000 ranges:

[ 1.775540] rk-pcie 2a200000.pcie: err 0x0020000000..0x00200fffff -> 0x0020000000

[ 1.775558] rk-pcie 2a200000.pcie: IO 0x0020100000..0x00201fffff -> 0x0020100000

[ 1.775576] rk-pcie 2a200000.pcie: MEM 0x0020200000..0x0020ffffff -> 0x0020200000

[ 1.775590] rk-pcie 2a200000.pcie: MEM 0x0900000000..0x097fffffff -> 0x0900000000

[ 1.775712] rk-pcie 2a200000.pcie: iATU unroll: enabled

[ 1.775723] rk-pcie 2a200000.pcie: iATU regions: 8 ob, 8 ib, align 64K, limit 8G

[ 1.977889] rk-pcie 2a200000.pcie: PCIe Linking... LTSSM is 0x3

[ 1.998915] rk-pcie 2a200000.pcie: PCIe Linking... LTSSM is 0x3

[ 2.078751] rk-pcie 2a200000.pcie: PCIe Link up, LTSSM is 0x130011

[ 2.078765] rk-pcie 2a200000.pcie: PCIe Gen.2 x1 link up

[ 2.078865] rk-pcie 2a200000.pcie: PCI host bridge to bus 0000:00

[ 2.078876] pci_bus 0000:00: root bus resource [bus 00-0f]

[ 2.078886] pci_bus 0000:00: root bus resource [??? 0x20000000-0x200fffff flags 0x0]

[ 2.078897] pci_bus 0000:00: root bus resource [io 0x0000-0xfffff] (bus address [0x20100000-0x201fffff])

[ 2.078906] pci_bus 0000:00: root bus resource [mem 0x20200000-0x20ffffff]

[ 2.078915] pci_bus 0000:00: root bus resource [mem 0x900000000-0x97fffffff]

[ 2.078944] pci 0000:00:00.0: [1d87:3576] type 01 class 0x060400

[ 2.079003] pci 0000:00:00.0: supports D1 D2

[ 2.079012] pci 0000:00:00.0: PME# supported from D0 D1 D3hot

[ 2.098903] pci_bus 0000:01: busn_res: can not insert [bus 01-ff] under [bus 00-0f] (conflicts with (null) [bus 00-0f])

[ 2.098998] pci 0000:01:00.0: [144d:a80a] type 00 class 0x010802

[ 2.099071] pci 0000:01:00.0: reg 0x10: [mem 0x00000000-0x00003fff 64bit]

[ 2.099494] pci 0000:01:00.0: 4.000 Gb/s available PCIe bandwidth, limited by 5.0 GT/s PCIe x1 link at 0000:00:00.0 (capable of 31.504 Gb/s with 8.0 GT/s PCIe x4 link)

[ 2.099774] pci 0000:00:00.0: BAR 8: assigned [mem 0x20200000-0x202fffff]

[ 2.099789] pci 0000:01:00.0: BAR 0: assigned [mem 0x20200000-0x20203fff 64bit]

[ 2.099827] pci 0000:00:00.0: PCI bridge to [bus 01-ff]

[ 2.099838] pci 0000:00:00.0: bridge window [mem 0x20200000-0x202fffff]

[ 2.100996] pcieport 0000:00:00.0: PME: Signaling with IRQ 70

[ 2.224975] nvme nvme0: pci function 0000:01:00.0

[ 2.225028] nvme 0000:01:00.0: enabling device (0000 -> 0002)

[ 2.227929] nvme nvme0: Shutdown timeout set to 10 seconds

[ 2.230861] nvme nvme0: 8/0/0 default/read/poll queues

[ 2.239119] nvme0n1: p1 p2 p3 p4 p5 p6

- 进入系统后查看 SSD 设备信息

lspci

00:00.0 PCI bridge: Rockchip Electronics Co., Ltd Device 3576 (rev 01)

01:00.0 Non-Volatile memory controller: Silicon Motion, Inc. SM2863EN/SM2863XT SSD Controller (rev 01)

3. rk3576 pcie 运行测速

3.1 写入测试

- 写入1G文件

root@linaro-alip:/mnt/disk# dd if=/dev/zero of=test bs=1M count=1024

1024+0 records in

1024+0 records out

1073741824 bytes (1.1 GB, 1.0 GiB) copied, 1.54047 s, 697 MB/s

- 写入2G文件

root@linaro-alip:/mnt/disk# dd if=/dev/zero of=test bs=1M count=2048

2048+0 records in

2048+0 records out

2147483648 bytes (2.1 GB, 2.0 GiB) copied, 5.32985 s, 403 MB/s

- 写入8G文件

root@linaro-alip:/mnt/disk# dd if=/dev/zero of=test bs=1M count=4096

4096+0 records in

4096+0 records out

4294967296 bytes (4.3 GB, 4.0 GiB) copied, 12.3762 s, 347 MB/s

- 写入8G文件

root@linaro-alip:/mnt/disk# dd if=/dev/zero of=test bs=1M count=8192

8192+0 records in

8192+0 records out

8589934592 bytes (8.0GB) copied, 27.265775 seconds, 300.4MB/s

3.2 读取测试

- 读取1G文件

root@linaro-alip:/mnt/disk# dd if=test of=/dev/null bs=1M count=1024

1024+0 records in

1024+0 records out

1073741824 bytes (1.1 GB, 1.0 GiB) copied, 3.02902 s, 354 MB/s

- 读取2G文件

dd if=test of=/dev/null bs=1M count=2048

2048+0 records in

2048+0 records out

2147483648 bytes (2.1 GB, 2.0 GiB) copied, 6.07948 s, 353 MB/s

- 读取4G文件

root@linaro-alip:/mnt/disk# dd if=test of=/dev/null bs=1M count=4096

4096+0 records in

4096+0 records out

4294967296 bytes (4.3 GB, 4.0 GiB) copied, 11.9877 s, 358 MB/s

- 读取8G文件

root@linaro-alip:/mnt/disk# dd if=test of=/dev/null bs=1M count=8192

8192+0 records in

8192+0 records out

8589934592 bytes (8.6 GB, 8.0 GiB) copied, 23.0404 s, 373 MB/s

Tips

结语

不枉博主详细讲解,欢迎订阅博主–炭烤毛蛋 。

2530

2530

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?