module yunsuan1(input clk,rst_n,output reg [7:0]a,b,b1,b2,b3,c,d,count);

always @(posedge clk)

begin

count=count+1;

if(count==10) a=-25;

if(count==11) a=-26;

if(count==12) a=25;

if(count==13) a=2;

b=~a+1;

b1=b>>1;

b2=~b1+1;

if(a[0])b3=~b1;else b3=~b1+1;

end

endmodule

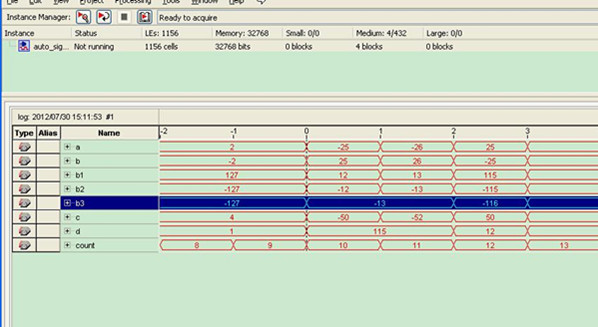

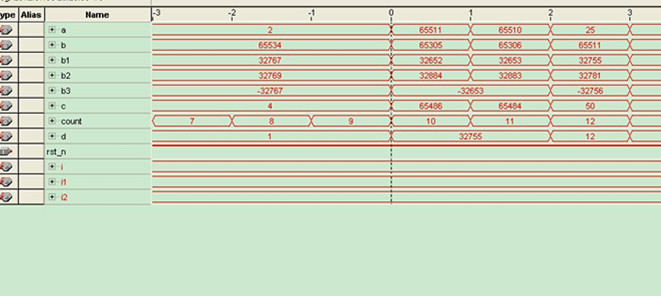

可以看出负数补码分为奇数和偶数表示:-25和-26的补码都为-13.

本文介绍了一个FPGA设计实例,展示了如何通过Verilog HDL实现负数的补码表示,并具体给出了-25和-26的补码表示方式。通过对计数信号的判断来更新寄存器中的数值,进一步转换得到不同负数的补码。

本文介绍了一个FPGA设计实例,展示了如何通过Verilog HDL实现负数的补码表示,并具体给出了-25和-26的补码表示方式。通过对计数信号的判断来更新寄存器中的数值,进一步转换得到不同负数的补码。

7098

7098

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?