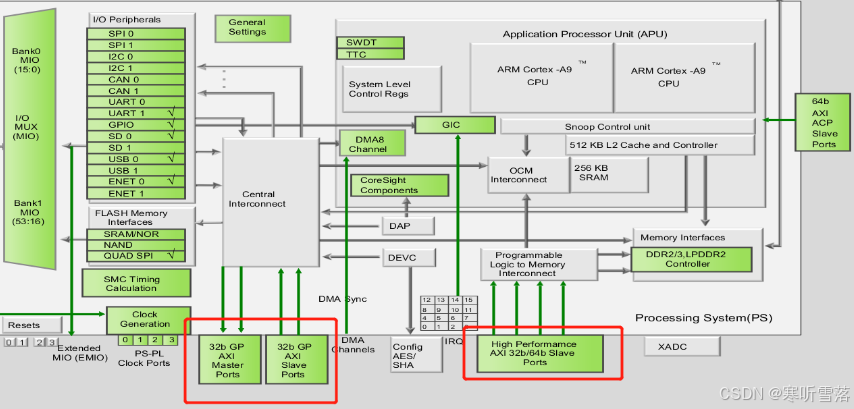

ZYNQ的PS部分核和PS部分的交互需要使用AXI总线。使用该IP核首先要注意的是它的两种模式存储转发模式核直通模式,弄清楚这两个模式才能知道怎么使用该IP核

1、存储传递模式

该模式下无论是MM2S,还是S2MM,得到的数据都会暂存到内部的FIFO中,只有当设置长度信息,数据完整了才会开始传递数据,且该模式下的能转发最大包的容量是与设置的FIFO有关系。

2、直通模式

在接受到数据后的第3个周期转发数据,但是最后一个数据是需要输入长度信息后才转发的。

不同模式下的寄存器是如何具体操作的,可以查找手册的,手册中举例了收发所有情况的寄存器变化很详细。

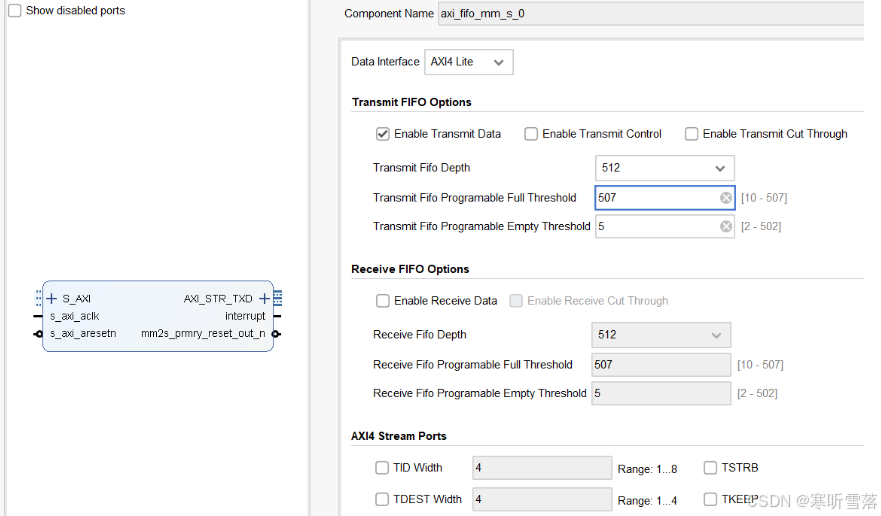

IP核的设置界面,分为4部分,最上面是设置AXI端接口,最下面是设置AXI_Stream接口。中间部分是设置内部FIFO的大小与FIFO读写的差异,stream端一共可以设置3种接口

AXI4-Stream TXD : 流数据发送接口

AXI4-Stream TXC : stream形式的控制信号

AXI4-Stream RXD : 流数据接受接口

PS端需要有M_AXI的输出接口,外设仅需要打开串口即可。测试IP核的功能,写数据为例

本文介绍了如何使用Vivado的IBERT核对ZYNQ FPGA的高速串行收发板进行千兆和万兆速率的测试。详细步骤包括配置IBERT IP核,修改example design以确保收发回环测试正常,以及在不同速率下进行长时间的误码测试,验证硬件的稳定性。

本文介绍了如何使用Vivado的IBERT核对ZYNQ FPGA的高速串行收发板进行千兆和万兆速率的测试。详细步骤包括配置IBERT IP核,修改example design以确保收发回环测试正常,以及在不同速率下进行长时间的误码测试,验证硬件的稳定性。

订阅专栏 解锁全文

订阅专栏 解锁全文

1万+

1万+