采用自感技术的GHz范围开关电感LC压控振荡器的设计与实现

1. 引言

由于吉赫兹频段内不断出现新的通信标准,双频段以及多频段收发器已变得具有吸引力[1]。对于n频段系统而言,采用多个压控振荡器(VCO)来生成载波信号需要单个VCO实现面积的n倍,而任意时刻只有一个振荡器处于开启状态。因此,研究人员致力于探索多频段VCO解决方案。由于LC压控振荡器拓扑结构具有更优的相位噪声性能,通常比环形振荡器更受青睐[2]。电容调谐LC压控振荡器可提供较大的调谐范围[3],但为了降低功耗,需要较大的电感[4]。当目标频率升高时,电容值随之减小,进而导致调谐范围减小。为克服这一限制,已提出采用切换式电感的方法[5–17]。

切换式电感方法利用MOS晶体管将集成电感的部分绕组短路,从而改变电感Lcoil,进而改变振荡频率f OSC ¼ 1= 2π ffiffiffiffiffiffiffiffiffiffiffiffiL coil p C。通过这种方法,使用单个压控振荡器即可利用同一电感实现不同的频段。此外,也已提出模拟电感调谐方法[18, 19]。

本文针对2至3吉赫兹、3至4吉赫兹以及4至6吉赫兹的目标频段,研究了采用自感技术的三种切换式电感LC压控振荡器的设计与实现。我们选择使用先进的65纳米CMOS制造工艺,因为在该工艺对于目标频段并非严格必需,但它使我们能够在当前典型的片上混合信号系统制造工艺中评估压控振荡器性能。

本文的结构如下。第2节介绍了电路拓扑。第3节描述了设计方法,重点讨论了切换式电感的尺寸设计以及开关对LC压控振荡器性能的影响。第4节展示了压控振荡器的实验表征结果,并将测量结果与仿真结果进行了比较。第5节估算了相关的品质因数(FOM)。最后在第6节给出了结论。

2. 电路拓扑

图1显示了在65纳米CMOS技术中实现的差分LC压控振荡器的原理图[20]。该拓扑结构与[3]中的类似,但移除了尾部电感,并采用了切换式电感。CMOS有源桥包含N沟道MOSFET(NMOS Mn)和P沟道MOSFET(PMOS Mp)交叉耦合对,利用电流复用原理[4],可在给定负阻的情况下降低(理论上减半)电流消耗,如[12]中提出的切换式电感压控振荡器所示。Mp器件的宽长比(W/L)是Mn器件的两倍,以实现gpm≈gn。

在所有条件下均能启动并维持振荡,这一点已通过工艺‐电压‐温度角分析验证。该压控振荡器未使用电流镜进行偏置,从而消除了一项主要的噪声源[21],但代价是无法控制其电流消耗。该压控振荡器设计用于配合低压差稳压器(LDO)工作,后者可提高对电源噪声的抗干扰能力,并减小推压效应,即对电源变化的敏感性。所有考虑的压控振荡器均采用相同的压控振荡器有源核心,这可能对其中某些设计而言并非最优。

频率控制通过以下方式实现:(1)提供频段选择的切换式电感;(2)提供频带内粗略调谐的二进制加权开关电容组;以及(3)提供细调的变容管阵列。

已经提出了多种切换式电感技术,它们可以分为两种主要方法,即自感[5, 8, 11, 12, 14, 15, 18]和互感[9, 10, 13, 16, 17]拓扑结构。

本研究涉及自感拓扑结构的分析与实现(图2)。在此拓扑结构中,开关位于射频(RF)信号路径上。当开关断开(关断状态)时,线圈的所有绕组均被接入,从而产生较大的电感Lcoil和较低的振荡频率fOSC;反之,当开关闭合(导通状态)时则相反。可实现的频率偏移可达几吉赫兹[5, 8, 11, 12, 14, 15, 18],远大于通过电容调谐所能实现的粗略调谐范围[4]。

在关断状态下,开关主要引入寄生电容;而在导通状态下,其等效串联电阻RON必须非常小,以免降低谐振槽路的品质因数Q。这就要求较大的宽度Wswitch,但会导致较高的寄生电容,因此在导通电阻与寄生电容之间存在折衷。

3. 切换式电感的设计

3.1. 线圈拓扑与布局

在利用自感技术的不同线圈拓扑结构中,我们考虑了具有内连接或外部射频连接的线圈(图3)。例如,[5]采用内连接,而[12]采用外部连接。除了图3中的布局外,其他布置也是可能的,例如[11]。

开关的位置选择旨在最小化开关节点处的电压摆幅(从而最小化等效开关电阻[4, 5])。电压摆幅最小的位置是共模节点(图3中的CM),即来自正负射频输入信号路径相连接的点。

在共模点进行切换显然不会改变电感,因此开关应放置在最近的金属交叉处。

如果射频和SW节点位于不同侧,则可获得更简单的版图。因此,绕组匝数n必须为偶数。

在相同面积占用的情况下,开关(处于导通状态)短路的绕组长于内层拓扑;这意味着导通状态与关断状态之间的频率差更大。此外,将开关置于线圈外部更为理想,可避免版图设计和线圈建模中的困难(例如磁场中的MOS器件以及内部含有有源元件的线圈),尽管原则上可以将有源电路放置在线圈内部或下方,并且已在[22]中实现。通过内层拓扑(图3(a))可轻松实现这一点,而对于外层结构(图3(b)),长型跨接通道需要跨越所有绕组以连接开关,因为并不总是可能将开关适配在线圈内部(例如参见图5中的VCO照片)。该跨接通道相关的电阻会叠加到开关本身的电阻上,因此从最小化开关导通时呈现的总电阻的角度来看,内连接更优。

由于上述原因,我们因此选择了内连接版图(图3(a))。

3.2. 线圈的尺寸设计

线圈尺寸设计的流程图在下文中有说明。

- 根据开启和关闭条件下的频率目标(fON和fOFF),通过原理图级仿真估算出LON target和LOFF target的值;

- 下文中的公式(1)[23]被用于估算几何参数

$$

L_{target} \approx \mu_0 n^2 d_{avg} \left( c_1 \ln \left( \frac{c_2}{\rho} \right) + c_3 \rho + c_4 \rho^2 \right)

$$

其中(见图3(a)),n为匝数,davg=(din+ dout)/2,ρ=(dout− din)/(dout+ din),以及c1= 1.07、c2= 2.29、c3= 0.0和c4= 0.19适用于八边形线圈。在整个本文所考虑的L和f范围中,公式(1)在[24,23]中的精度被证明在5%以内。如第1节所述,在关断状态下n必须为偶数。利用公式(1)及实际几何参数,我们发现n= 4是用于GHz范围内的压控振荡器的最佳选择。然后,将公式(1)分别应用于LON target和LOFF target(即分别使用n= 3和n= 4)以确定din和dout。前者在开启和关闭状态中保持不变,而后者取决于有效工作绕组的数量。接着我们选择了金属宽度w= 7 μm,该值在当前工艺下能够在绕组电阻与线圈面积之间提供良好的折衷。针对LON target和LOFF target的公式(1)然后提供din和s。

- 然后进行了开关的尺寸设计(见第3.3节)。

- 基于使用Sonnet进行的电磁仿真,调整了[25], din以满足fOFF目标值。仿真考虑了65nm工艺的实际衬底以及金属/介质层结构。

- 在步骤4得到的din基础上,利用电磁仿真进一步优化间距s的取值,以达到fON目标值。

- 随后通过增加外圈绕组间距(图3(a)中的sL)对fON进行微调,依据的观察结果是:当增大sL时,fON减小,而fOFF几乎保持不变。事实上,尽管预期sL在关断状态(此时外圈绕组起作用)中起重要作用,但在sL介于6至15 μm范围内的仿真结果显示,导通状态下的频率受sL影响,主要原因是最后一圈绕组与其他绕组之间的互感。

3.3. 开关的尺寸设计

基于对开关引入的噪声、寄生电容和占用面积的仔细分析,我们选择了一种基于单个NMOS晶体管的实现方案,该方案相较于单个PMOS(主要在面积节省方面具有优势,因为由于载流子迁移率较低,PMOS需要更大的尺寸才能获得与其NMOS对应器件相同的RON)甚至相较于由NMOS和PMOS并联组成的传输门晶体管都更具优势。事实上,

考虑到NMOS和传输门的面积占用相同,仿真表明,NMOS开关在热噪声区域(即3MHz频率偏移)具有更大的调谐范围和更低的相位噪声;此外,与传输门拓扑相比,NMOS拓扑在开关节点处的电压摆幅更低。

从图4的仿真结果可以看出,如果NMOS不够宽,则振荡频率取决于Wswitch。实际上,开关越大,对线圈部分的短路效果越有效。如果开关不够大,并联电路(由开关和被切换的线圈部分组成)仍然具有一定的电感,该电感会叠加到未被开关短路的线圈部分的电感上。

仿真得到的相位噪声在导通状态时出现最大值,因为增大Wswitch会减小RON并改善品质因数Q,但同时引入了较大的寄生电容。当处于关断状态时,晶体管位于射频路径之外,其对相位噪声的贡献仅来自寄生电容(通过改变振荡频率和波形),而不受导通电阻的影响。因此,我们发现从2毫米增加到4毫米并不会带来显著优势,因为开关已经足够大,能够将外层绕组短路。进一步增加开关宽度将会增加面积和寄生电容。开关节点处的振荡幅度明显低于射频信号,例如在当前设计中约为300毫伏,而开关和射频信号的共模电压相同,均为VDD/2。我们已验证,开关尺寸对差分射频信号的幅度影响可以忽略不计(因为开关靠近线圈的共模点)。

噪声贡献的分析表明,如果开关尺寸不够宽(在本例中即小于约1毫米),则当频偏Δf等于100 kHz和3 MHz时,相位噪声主要由开关漏极电流的热噪声主导。这意味着为了降低相位噪声,开关应尽可能大(图4),并且需要精心设计版图以减小寄生效应。由于Wswitch较大,开关的版图设计尤为关键。主要的权衡在于降低RON以及结和寄生电容。栅极、源极和漏极连接的寄生电阻也应予以考虑。由于开关节点处射频信号幅度较低,开关电阻因过驱动(即射频信号引起的开关偏置变化)而发生的变化不会影响相位噪声。

4. 测量结果

采用切换式电感LC谐振槽的LC压控振荡器已在65纳米CMOS技术中实现了五个实例,其开关宽度和频率范围如表I所示。

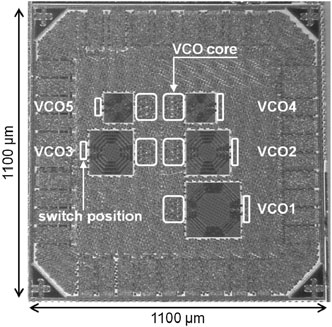

在本次实现中,为了单独分析压控振荡器的性能,未包含用于提高对电源噪声和供电变化抗干扰能力的低压差稳压器(LDO)(第2节)。因此,特别注意使用干净的外部电源为压控振荡器供电。图5显示了芯片照片,其中五个切换电感清晰可辨。表二列出了带4mm宽开关的压控振荡器(即VCO1、VCO2和VCO4)的面积占用情况,该面积占用分为线圈、开关和压控振荡器核心三部分的贡献。五个压控振荡器可以独立供电(但在任意时刻仅有一个压控振荡器运行),并共享一个单一的多路复用器,通过简单的电流模逻辑差分级将信号引出芯片。标称供电为1.3伏特。每个压控振荡器可通过数字字线进行粗调,并通过模拟线进行细调。

我们在此报告实验结果。调谐特性是通过频谱分析仪获得的。相位噪声(以相位的功率谱密度表示)使用Aeroflex PN9000并配合分频器除以8进行测量,然后增加20 log10 8= 18 dB。

表I. 实现的LC压控振荡器

| VCO | 频率范围(吉赫兹) | 开关宽度 (毫米) |

|---|---|---|

| VCO1 | 2–3 | 4 |

| VCO2 | 3–4 | 4 |

| VCO3 | 3–4 | 2 |

| VCO4 | 4–6 | 4 |

| VCO5 | 4–6 | 2 |

表二。Wswitch = 4毫米的压控振荡器的面积消耗

| 组件 | VCO1面积 [mm²] (%) | VCO2面积 [mm²] (%) | VCO4面积 [mm²] (%) |

|---|---|---|---|

| Coil | 0.040 (87) | 0.026 (81) | 0.011 (65) |

| VCO核心 | 0.005 (11) | 0.005 (16) | 0.005 (28) |

| 开关 | 0.001 (2) | 0.001 (3) | 0.001 (6) |

仪器的读数。对于分频器未引入显著噪声的隐含假设,已通过对VCO1在无分频器情况下的测量结果明确验证实。验结果与包含RC寄生元件以及通过电磁仿真获得的线圈完整S参数的版图后仿真进行了比较[25]。

图6显示了测得的精细调谐曲线(顶部)和KVCO(底部),它们随Vtune的变化关系,适用于VCO1和VCO4,即开关宽度相同(4毫米),但目标频段不同。我们看到,KVCO在两个频段中不同,并且在高频时达到非常高的值。这在某种程度上是预料之中的,因为相同的电容变化对于不同的线圈电感会导致不同的频率变化。因此,必须设计方法来控制并保持所选频段下的KVCO恒定。

例如,如果将VCO置于PLL中,可以采用文献[26]中的技术(尽管在当前设计中未实现此操作)。

图7显示了VCO1、VCO2和VCO4的实测与仿真粗略调谐结果(实线),即开关宽度相同(4毫米)但频率范围不同。细调电压为Vtune= 0.6 V。实测振荡频率与仿真结果吻合良好,仅存在约≈300 MHz的偏移,该偏移在整个压控振荡器的粗略调谐范围内几乎保持恒定。该偏移的主要原因是电源线围绕线圈形成的寄生电感环路,导致线圈电感降低,且由于大尺寸线圈(低频)比小尺寸线圈(高频)更敏感,因此该效应在大线圈上影响更为显著。

图8显示了所有已实现的压控振荡器在不同粗调二进制字(Vtune= 0.6 V)下的实测电流消耗,该值与传统压控振荡器相当[3]。需要注意的是,在导通状态(虚线)下电流比关断状态(实线)增加了50%。开关的RON以及电感Lcoil的减小(见图9左图)共同导致了线圈品质因数Q的显著下降(见图9右图)。由于缺乏电流控制,线圈品质因数Q的降低导致在给定电源电压VDD下电流消耗增加。

开关宽度对振荡频率的影响如图10所示,该图展示了针对相同频率范围但采用不同开关的压控振荡器。无论目标频率如何,开关尺寸对高频段(即开关开启时)的振荡频率影响最大,而对低频段(开关关闭时)仅有有限的影响,这与第3.3节中的仿真结果预测一致。

)再次变为正值)

测得的相位噪声谱如图11(实线)所示,针对带有4mm宽开关的压控振荡器,即 VCO1、VCO2和VCO4。在所有目标频段中,测量结果与仿真结果(虚线)吻合良好。如图9所示,由于导通状态下谐振槽路的品质因数下降,关断状态下的相位噪声更低,符合预期。

开关尺寸对针对不同频段的压控振荡器实测相位噪声的影响如图12所示。开关越大,在导通状态下相位噪声的恶化程度越低。以3–4 GHz压控振荡器(即VCO2和VCO3)为例,当开关尺寸为Wswitch= 2 mm时,相位噪声恶化(开关开启与关闭之间)为8 dB,而当开关尺寸增大至Wswitch= 4 mm时,恶化程度降低至3 dB。在较高频率下,开关尺寸的影响更为显著:对于4–6 GHz压控振荡器(即VCO4和VCO5),当开关尺寸为Wswitch= 2 mm时,相位噪声恶化为14 dB,增大至Wswitch= 4 mm后则降低至7 dB。基于李森公式[27]

$$

PN(\Delta f) = 10 \log_{10} \left[ 2kTF \cdot \left(1 + \frac{f_{OSC}}{2Q\Delta f}\right)^2 \cdot \frac{1}{P_s} \right]

$$

(其中k是玻尔兹曼常数,T为温度,F为额外噪声系数,Ps为信号功率,Q为谐振槽路品质因数,fOSC为振荡频率,Δf为偏移频率),可以区分频率、功率和品质因数变化对相位噪声的贡献。结果表明,相位噪声的变化主要由品质因数的变化决定。因为在导通状态下使用较大的开关可降低相位噪声,所以相位噪声受开关的串联电阻影响大于其结和寄生电容的影响。

5. 优值

表III总结了压控振荡器的测量性能。所报告的优值是用于压控振荡器比较的广为人知的优值(见[28]),其定义为

$$

FOM(\Delta f) = -10 \log_{10} \left[ \left( \frac{\Delta f}{f_{OSC}} \right)^2 \cdot \frac{P_s}{1mW} \right] - PN(\Delta f)

$$

并根据振荡频率fOSC、功耗Ps和相位噪声PN(Δf)对性能进行归一化。需要再次强调的是,由于缺少电流源,所实现的压控振荡器需要使用低压差稳压器进行电源调节,以提高其对电源噪声具有免疫力。因此,所报告的优值应理解为在采用此类调节的情况下得出,从而消除了电源噪声,在此处报告的测量中已将电源噪声保持在尽可能低的水平。对于当前实现,优值比传统压控振荡器的现有技术水平低约10分贝,这主要是由于相位噪声代价所致。然而,我们应牢记,当前方法具有极宽的频率范围,与使用两个压控振荡器相比可节省50%的面积,这一优势是以性能降低为代价的。通过迭代调整晶体管和线圈的尺寸以精细优化设计,确实还有进一步改进的空间。例如,我们在优化线圈之前已对有源桥中的NMOS和PMOS进行了尺寸设计。在线圈版图完成后重新调整有源桥的尺寸将有助于实现更优的性能。表III还表明,切换式电感所针对的频率步进越大(即电感值的变化越大),开关尺寸对压控振荡器性能的影响就越显著。表格的最后一列报告了包含版图后寄生参数的压控振荡器的仿真振荡幅度:可以看出,当开关开启时,VCO4和VCO5的振荡幅度osc有所降低,尤其是在VCO5中更为明显,这解释了该压控振荡器在高频工作时优值显著较低的原因。

表III. 在粗调二进制字设为其中心值且Vtune= 0.6 V时,利用相位噪声、电流消耗和振荡频率的实验值,根据公式(3)计算得到的 Δf= 1MHz处的优值。最后一列给出了仿真得到的振荡幅度

| 频率 [GHz] | 功率 [mW] | 1兆赫处的相位噪声 [dBc/Hz] | 1兆赫处的优值 [dB] | Vosc [V] |

|---|---|---|---|---|

| VCO1 OFF | 2.16 | 10.39 | -112.1 | 168.6 |

| VCO1 ON | 3.44 | 13.39 | -109.9 | 169.3 |

| VCO2 OFF | 3.09 | 11.42 | -110.1 | 169.3 |

| VCO2 ON | 4.51 | 13.68 | -107.8 | 169.5 |

| VCO3 OFF | 3.11 | 11.80 | -108.7 | 167.8 |

| VCO3 ON | 4.37 | 15.39 | -105.2 | 166.2 |

| VCO4 OFF | 4.27 | 12.72 | -112.9 | 174.5 |

| VCO4 ON | 6.24 | 16.13 | -109.0 | 172.8 |

| VCO5 OFF | 4.34 | 12.60 | -107.4 | 169.1 |

| VCO5 ON | 6.00 | 16.50 | -97.3 | 160.7 |

| [11] 高频f | 4.56 | 7.56 | -121 | 185 |

| [11] 低频f | 2.305 | 6.0 | -120 | 179 |

| [16] 高f | 5.75 | 19.2 | -120 | 182 |

| [16] 低f | 3.3 | 19.2 | -125 | 183 |

| [17] 高频f | 1.9 | 1.06 | -114 | 179 |

| [17] 低f | 1.1 | 1.06 | -126 | 187 |

表IV. 使用公式(4)根据实验相位噪声、电流消耗和调谐范围计算得到的 Δf= 1 MHz处的PFTN。粗调二进制字设置为中心值,且Vtune= 0.6 V。所列范围值对应于开关处于开启或关闭状态时计算的PN和Ps

| VCO | PFTN (Δf=1MHz) [dB] |

|---|---|

| VCO1 | -9.9 ÷ -13.2 |

| VCO2 | -11.4 ÷ -14.5 |

| VCO3 | -14.0 ÷ -18.7 |

| VCO4 | -6.3 ÷ -11.2 |

| VCO5 | -13.2 ÷ -24.5 |

| [11] | 5.3 |

| [12] | 6.6 ÷ 10.2 |

| [16] | 6.0 ÷ 9.5 |

| [17] | -2.5 ÷ 10 |

我们的设计所表现出的较小性能主要归因于两个原因:(1)在[11, 12, 16, 17]中仅考虑了一个压控振荡器,并且核心针对特定的频段和线圈进行了专门优化,而在我们的工作中,相同的核心用于五个不同的压控振荡器,且未进行专门优化;(2)[16, 17]中采用的切换式电感拓扑比此处使用的简单的并联拓扑复杂得多。

6. 结论

我们基于自感方案,在65纳米工艺中设计并实现了一组具有不同目标频段的切换式电感压控振荡器。通过对版图进行适当调整,可使电感器在开关的开启和关闭状态下均满足所需中心频率值的要求。得益于稳健且精确的电感设计与验证方法,所有设计在仿真结果与实验之间均获得了非常好的匹配度。我们观察到,为了最小化开关对压控振荡器性能的影响,需要使用大宽度的MOSFET器件,但在尺寸上存在一个较宽的最优范围。与传统压控振荡器相比,未观察到明显的功耗增加。所实现的切换式电感压控振荡器的面积基本与单频带压控振荡器相同,相较于使用多个压控振荡器具有显著的面积节省。

本研究的重点集中在电感器本身的设计上,而压控振荡器有源核心仅设计一次后便在所有压控振荡器中重复使用,这导致相位噪声性能次优,优值指标也略低于现有技术水平。尽管受到此限制的影响,该工作仍使我们能够分析简单切换式电感架构的优缺点,并评估此类非常规电路中的硬件与仿真之间的相关性。我们认为,若在每个特定电感器尺寸确定后,针对性地重新调整有源桥的尺寸,从而实现完全优化的设计,将进一步提升性能,并可能产生适用于片上集成可重构无线模块的工作电路。

80

80

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?