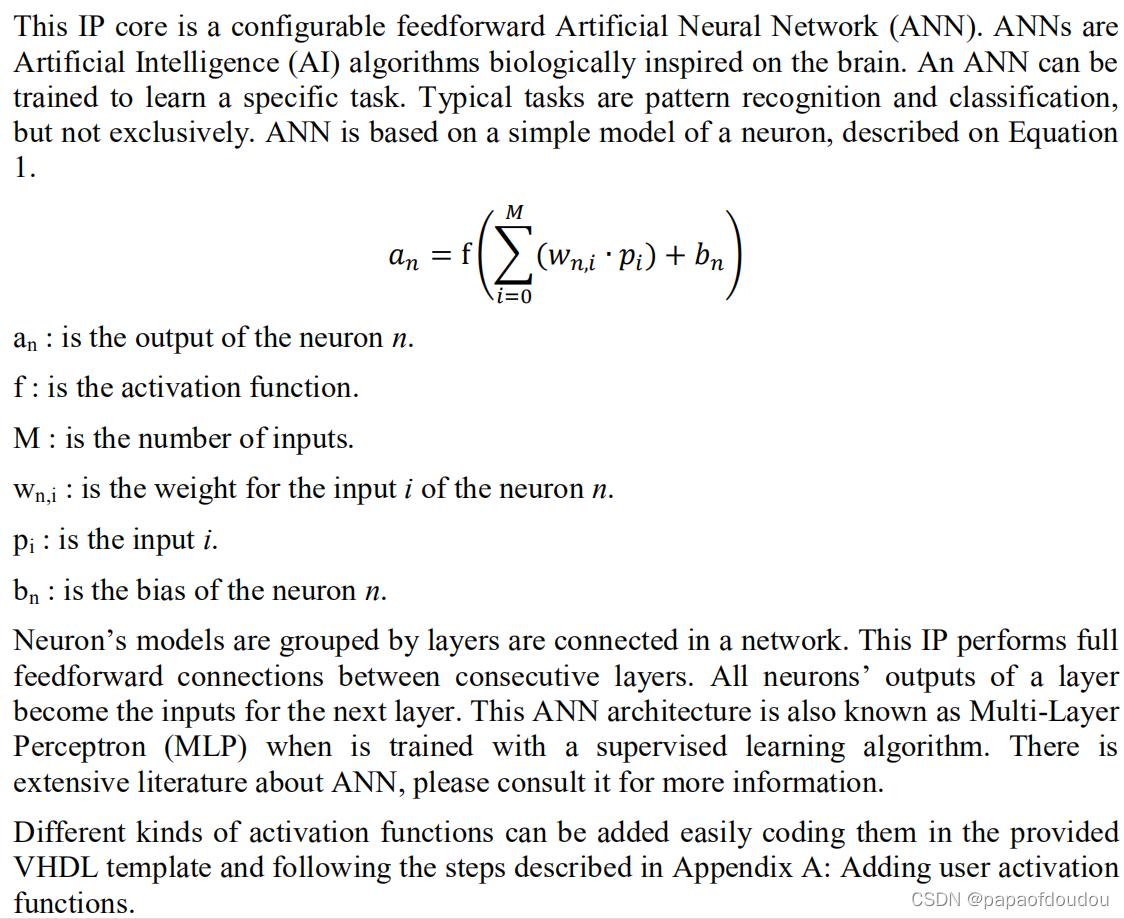

NPU设计的数学模型比较简单,可以看成是对高维空间坐标向量进行一次仿射变换,公式如下图中的样子:

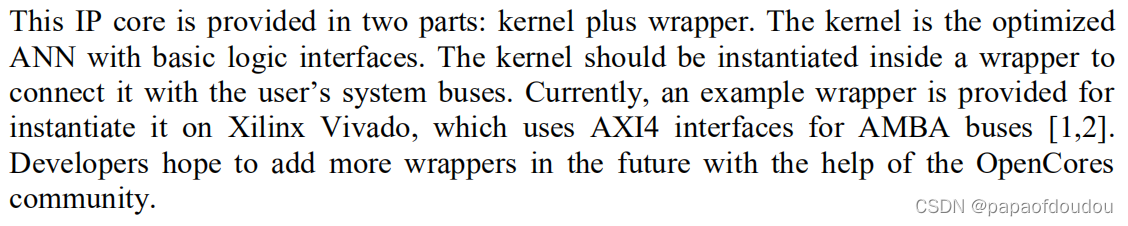

这份ANN IP实现包含两个部分,ANN 核心实现和ANN封装实现,封装实现的作用是可以将ANN的核心实现逻辑与不同的SOC系统总线对接,当前有实现和AXI4对接的wrapper实现。

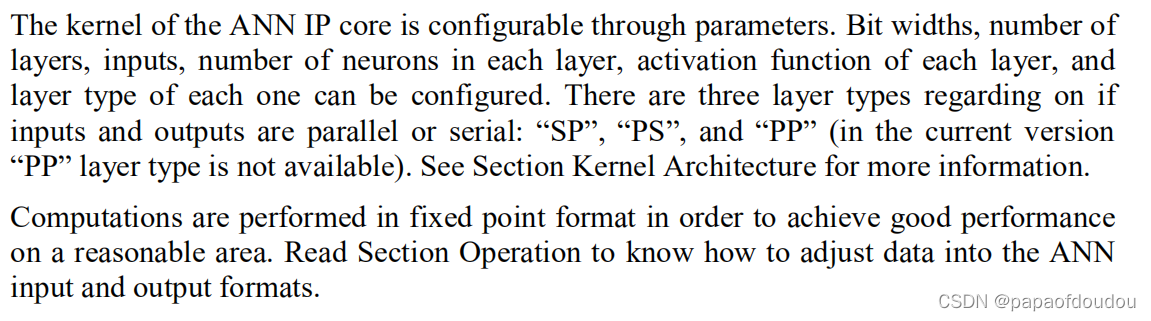

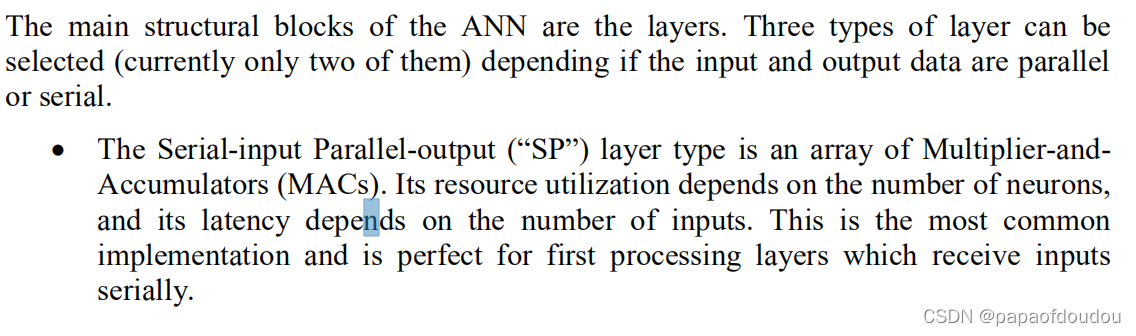

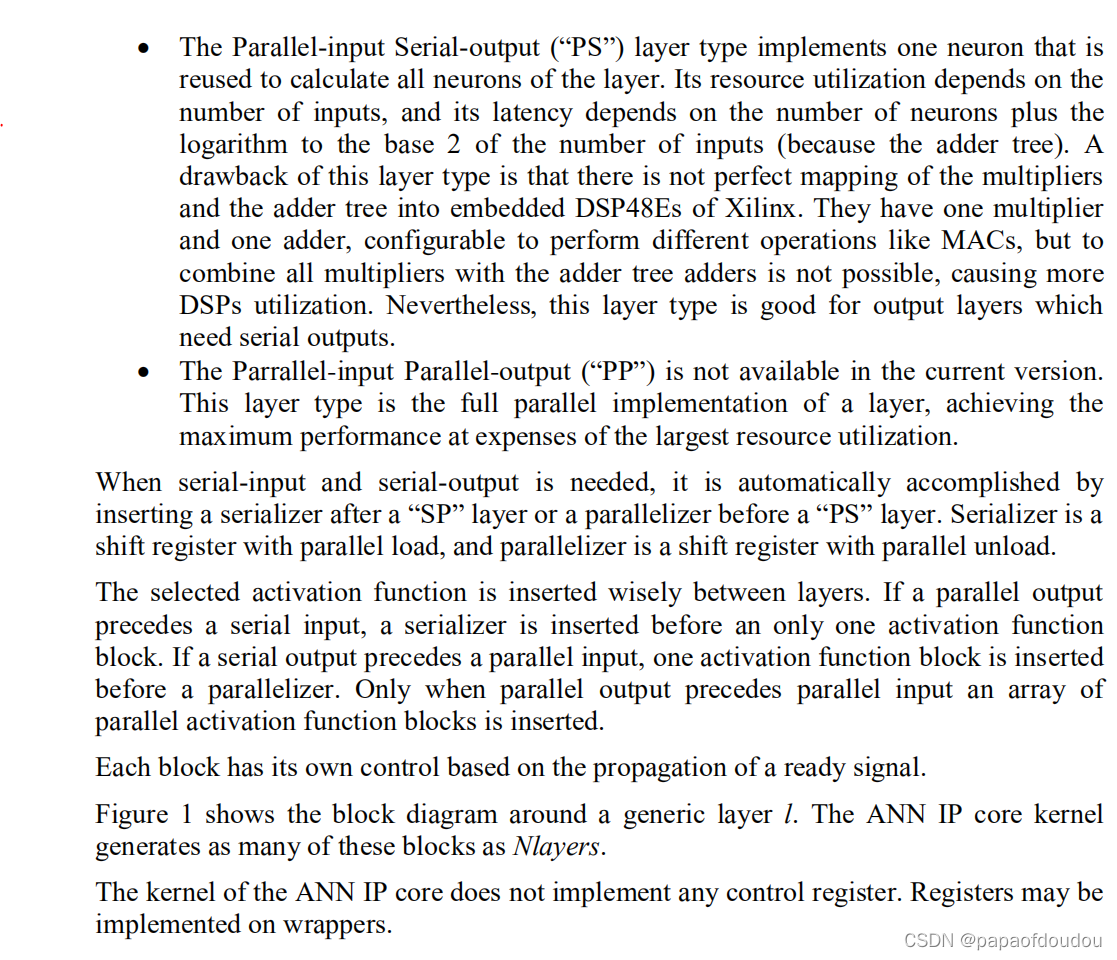

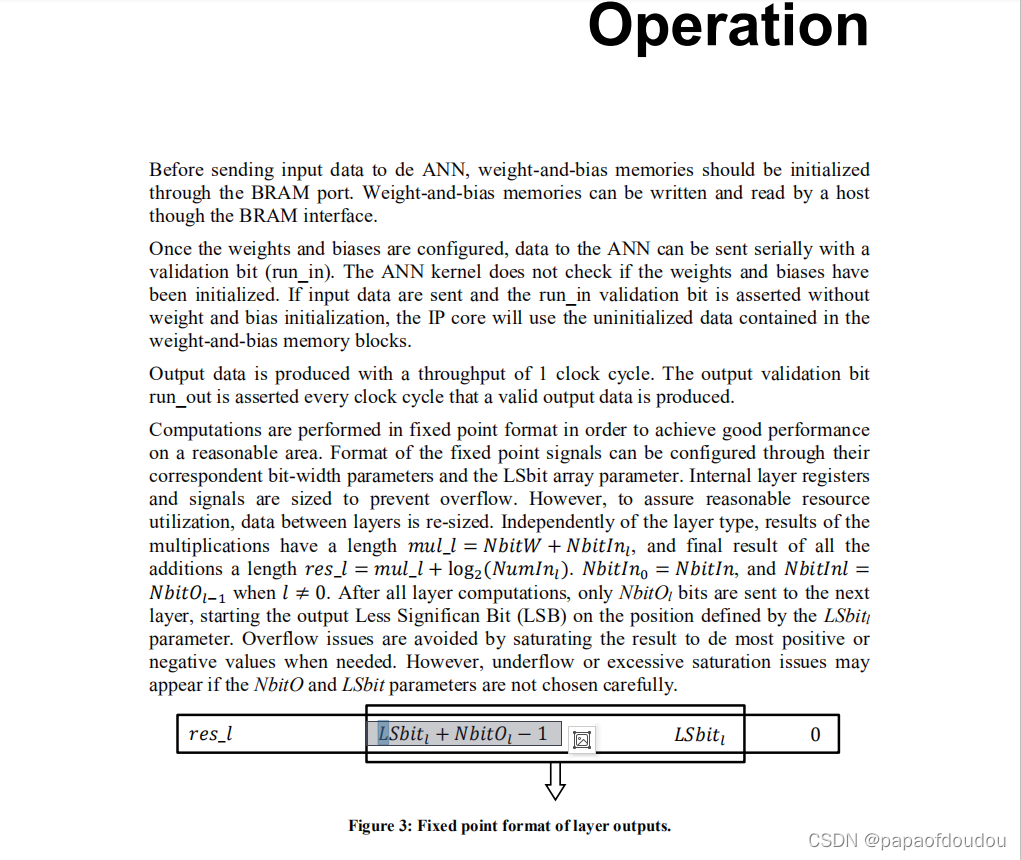

IP核心是可以通过参数进行配置的,包括位宽,层数,输入维度,以及各层的神经元数,根据输入和输出并行、串行方式的不同,可以将各层分为三种类型,分别是"SP","PS","PP",当前的实现还不支持PP。当前的实现,数据操作是按照定点格式进行,目的是为了在有限的IP面积上使性能最大化。

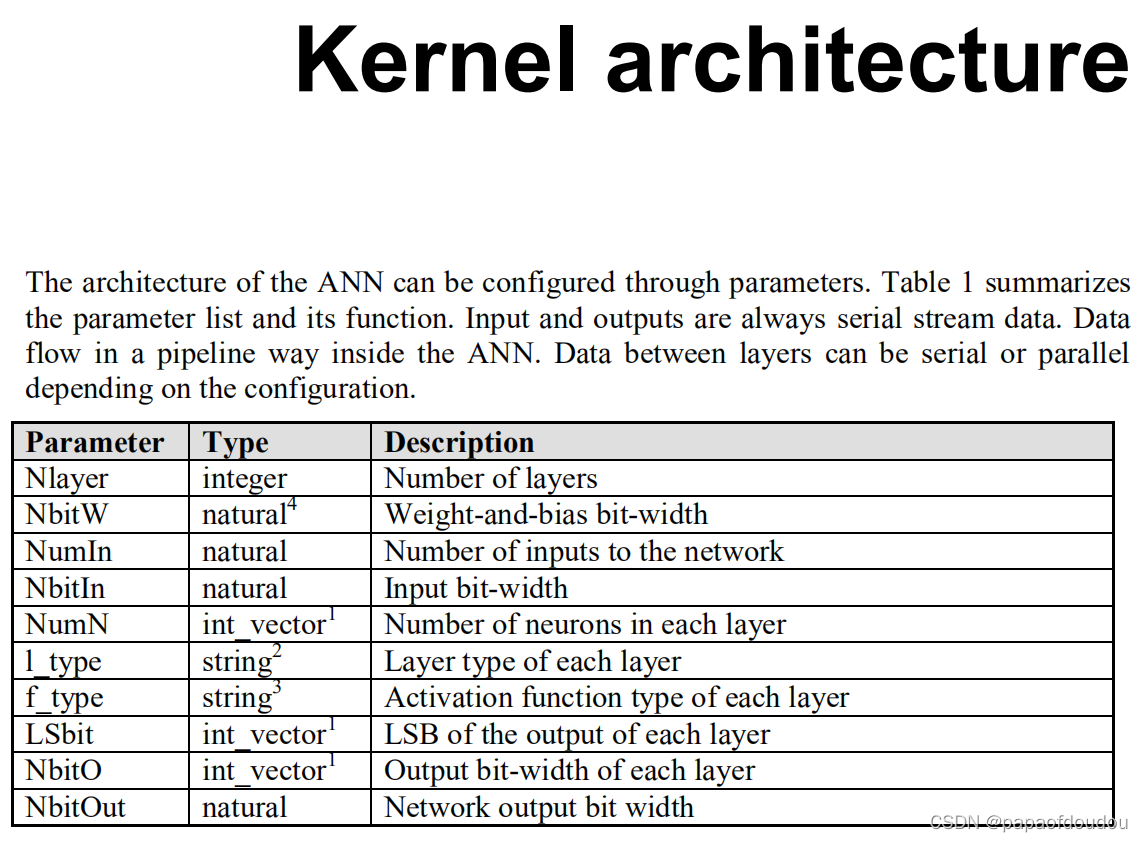

可配置参数如下表所示:

输入层适合SP,输出层适合PS

不同的属性层之间需要串并转换和并串转换:

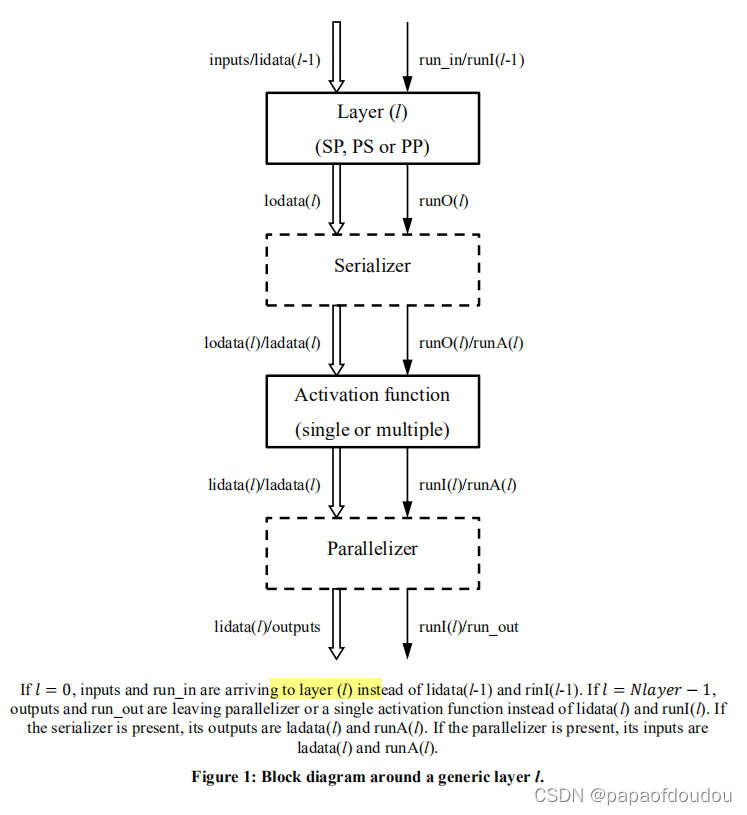

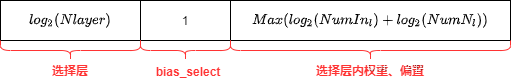

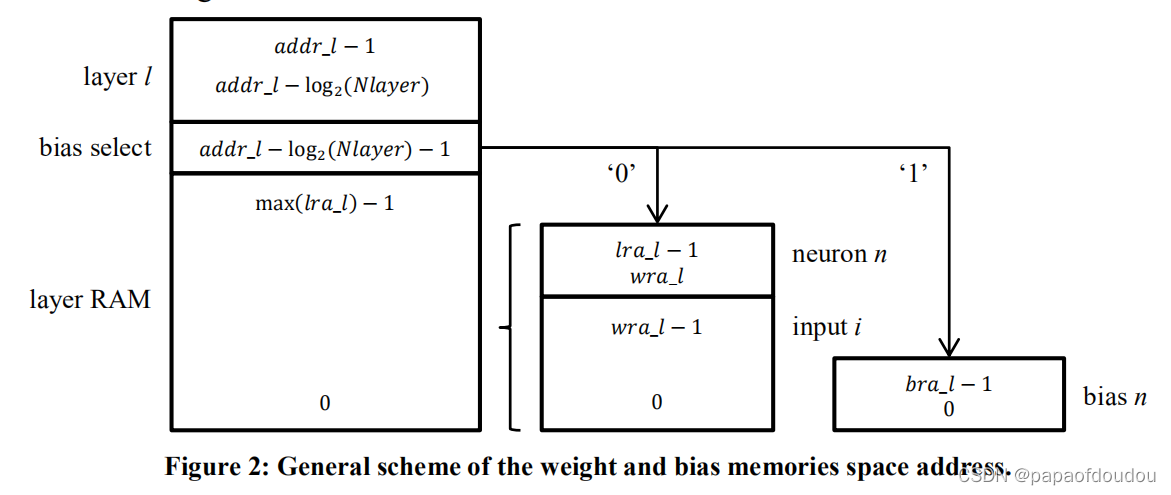

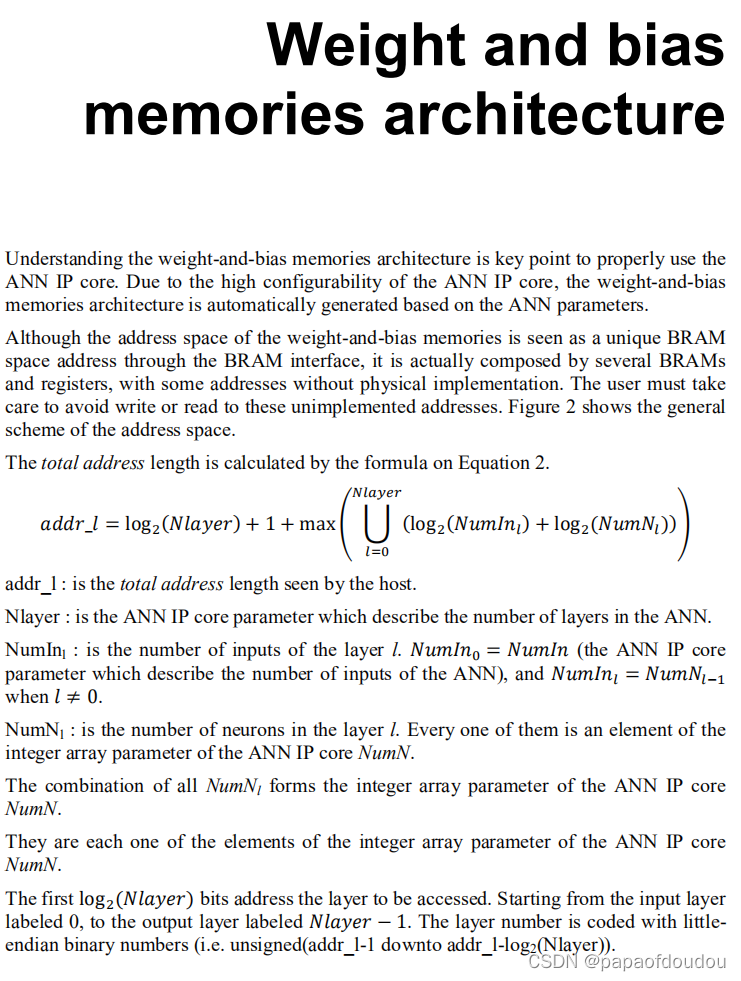

关于权重内存访问很有意思,首先定义的是权重内存地址的宽度,它的定义很有意思,我们可以这样理解,整个地址可以分解成几个部分, 分别是, 表示层号的这部分可以索不同的层,宽度是

。接着是表示索引偏置还是权重的bias_select,它宽度只有1位,身下的位则是索引某层内部的数据了。它的宽度计算很有意思,用文字表达分成两步。

第一步:求出各层的输入数和神经元数的以2为底的对数和。就.

第二步:以第一步计算出来的各层权重位宽位集合元素,组成包含所有层的位宽的集合。

第三步:求集合中的最大值,即为最后的RAM位宽。

将RAM位宽和前面的bias select 1位宽和层ID位宽加在一起,就是最后的权重地址空间总位宽。

至于为何某层所需要的地址空间位数是,可以这样想,假设对于m输入,n个神经元的层,它需要的权重占用多少字节呢?假设每个权重只占用1个字节,所以,权重矩阵元素的个数应该位 mxn个。也就是总权重需要mxn个字节。

mxn个字节,需要占用多少总线位宽呢? 求2为底的对数不久可以了么,也就是

所以,一切这都这么合理,关于神经元的拓扑结构,可以参考这篇博客:

关于NPU的设计逻辑和思路,请教OpenC906 社区群的专家给出的答复:

本文探讨了NPU(神经处理单元)的设计,其数学模型基于高维空间坐标向量的仿射变换。内容涉及IP核心的可配置参数,如位宽、层数和神经元数,并详细阐述了权重内存地址宽度的计算方法。文章还提到了权重内存的访问策略,以及神经网络结构的基本原理。OpenC906社区的专家提供了有关设计思路的解答。

本文探讨了NPU(神经处理单元)的设计,其数学模型基于高维空间坐标向量的仿射变换。内容涉及IP核心的可配置参数,如位宽、层数和神经元数,并详细阐述了权重内存地址宽度的计算方法。文章还提到了权重内存的访问策略,以及神经网络结构的基本原理。OpenC906社区的专家提供了有关设计思路的解答。

https://blog.youkuaiyun.com/tugouxp/article/details/109340428

https://blog.youkuaiyun.com/tugouxp/article/details/109340428

1033

1033

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?