SystemVerilog中数组的维度相关概念解析

1. sv多维数组相关概念解析

首先看下SystemVerilog标准中对packed(合并)和unpacked(非合并)数组的定义

简单说来就是定义在数组名左边的是packed部分,右边的是unpacked部分

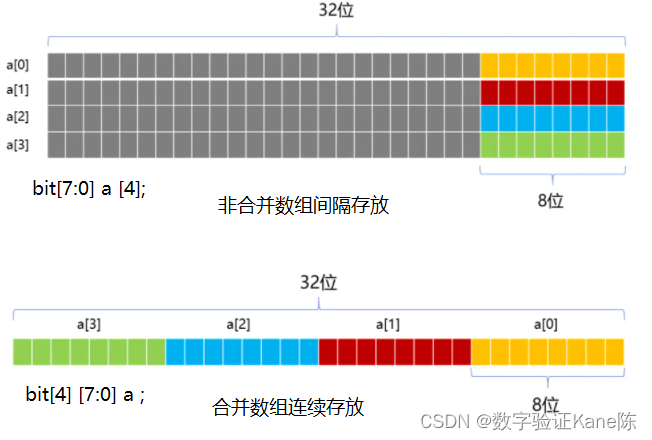

合并数组部分定义的维度在内存空间中是连续排放的,非合并数组是非连续存放,以32位内存系统为例两种数组的内存存储形式如下图所示:

多维数组里packed和unpacked维度示意如下(ijk三个维度对应packed,lmn三个维度对应unpacked):

bit [i][j][k] array [l][m][n];

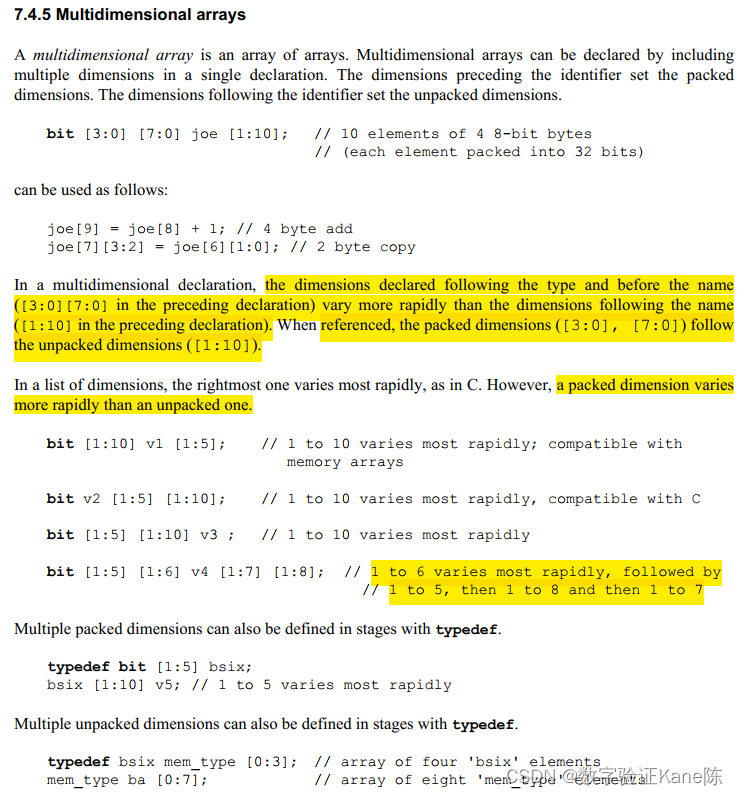

再引申一下看看多维数组的下标对应情况

下面是sv语法中的描述:

可见在进行多维数组引用时,packed部分的维度在引用时比unpacked部分要高,unpacked部分的维度越靠近数组名越低,packed部分也是越靠近数组名越低。

总结下来数组的维度排序从低到高依次是:

1、先从左到右依次对unpacked部分维度排序

2、再从左到右依次对packed部分维度排序

还是用上面多维数组的例子:

// packed unpac

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

676

676

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?