在LPDDR4以后,IO接口信号发生方式采用低电压摆动-终止逻辑(LVSTL)的方式。它由两个NMOS构成了上下拉,信号的摆动电压幅度是可编程控制的。在LPDDR5中也是采用LVSTL,VDDQ(TT)为0.5V,写方向上VOH最大在300mV左右。PHY发送端设置PU/PD的值,下图中间Channel由PHY SOC+PCB+DRAM PKG上的传输线组成一个完整的无源通道,DRAM ODT下拉到地。

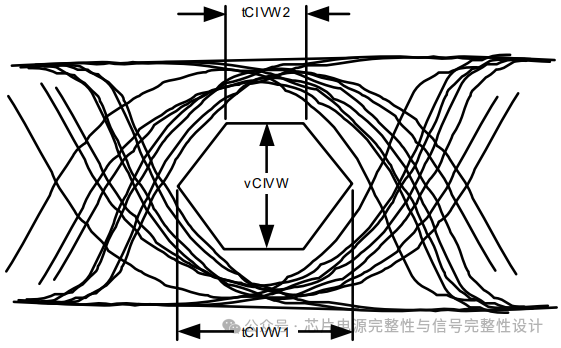

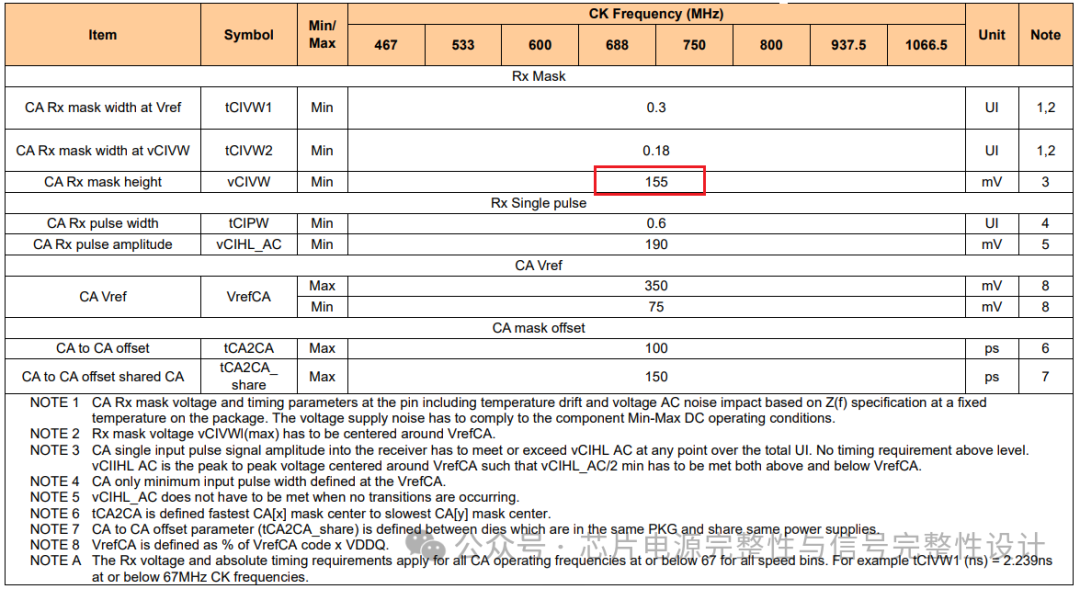

同时JEDEC协会对CA的Mask定义了一个六边形的要求,如下图,如表中可以看到眼高要求为155mV。

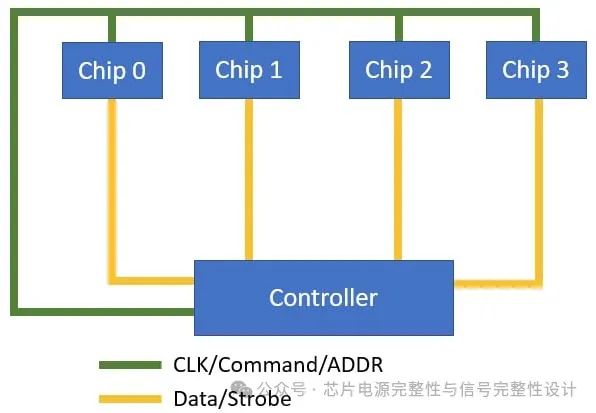

由于DDR的不同应用结构的不同,Load数目增多会带来分压,则眼高为主要关注点。所以采用最大的驱动能力,同时保证阻抗连续性是Drive和ODT适配、串扰及拓扑选择的关键点。串扰可以通过控制走线间距进行管控,而满足阻抗连续性且考虑板厂单线加工能力在30~600hm的约束下,一般连接的拓扑有Star型、F|yby和混合型。

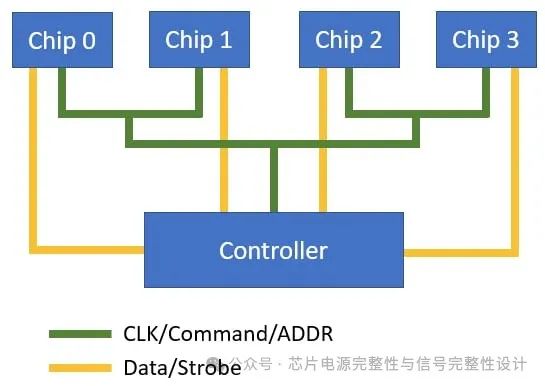

Star型

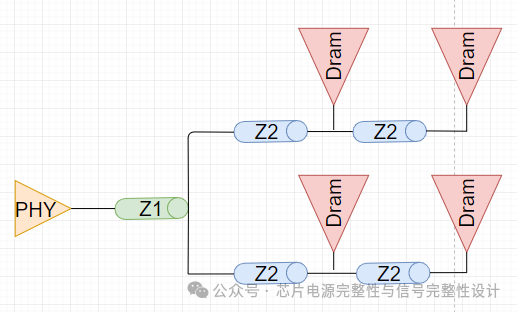

对于Star型拓扑,如下图,为保证阻抗连续性,理论需要Z2=2*Z1。结合一般封装厂和PCB板厂的常规加工能力,则在工程实现上采用:Driver阻抗为34Ohm,SOC封装的阻抗为40Ohm±10%,PCB主干的阻抗30Ohm±15%,PCB分支的阻抗是60Ohm±10%,颗粒封装的阻抗多为40Ohm±10%,4个DRAM的ODT设置需在等效40~60Ohm区间进行sweep,结合眼图结果选取最优解。

同时由于此拓扑需要阻抗比例关系,所以对阻抗敏感度更高(存在35Ohm的PCB主阻抗干和55Ohm的PCB分支阻抗的可能性),因此在仿真中除芯片的Corner外,也考虑加工误差带来的影响。

对上述拓扑中的4个DRAM的ODT设置进行展开说明:由于颗粒封装阻抗由各家内存厂商确定,属于不可控因素,所以需要对4个DRAM的ODT设置为等效区间进行扫描。如等效为60Ohm,可以有多种设置情况,包括4个ODT均为240Ohm,2个OFF且2个120Ohm,3个OFF且1个60Ohm等。此外PCB的主干和分支的线长需要结合Layout的可实现性进行评估,也是一个制约因素。

Fly-by型

对于Fly-by型拓扑,由于分支很短,如下图,只有主干阻抗进行分段,可以结合sweep结果分段微调,但整体差异不大,此处默认阻抗为统一值。结合前述封装厂和PCB板厂的常规加工能力,则在工程实现上采用:Drive阻抗为34Ohm,SOC封装的阻抗为45Ohm±10%,PCB的阻抗45Ohm±10%,颗粒封装的阻抗多为40Ohm±10%,4个DRAM的ODT设置需在等效40~600hm区间进行sweep,最终结合眼图结果选取。

此外PCB的4段的线长需要结合Layout的可实现性进行评估,也是一个制约因素。需要结合产品板的具体Placement和DRAM颗粒的Ball-map约束线长的区间。而各段线长会对最后眼图结果有很大影响。

混合型拓扑

对于混合型拓扑,为保证阻抗连续性,理论上需要Z2=2*Z1,分支混合Flyby拓扑处也默认为统一值。结合封装厂和PCB板厂的常规加工能力,则在工程实现上采用:Drive阻抗为34Ohm,SOC封装的阻抗为40Ohm±10%,PCB主干的阻抗30Ohm±15%,PCB分支的阻抗是60Ohm±10%,颗粒封装的阻抗多为40Ohm±10%,4个DRAM的ODT设置需在等效40~60Ohm区间进行sweep,结合眼图结果选取。同时由于此拓扑需要阻抗比例关系,所以对阻抗敏感度更高(例如存在35Ohm的PCB主阻抗干和55Ohm的PCB分支阻抗的可能性),在仿真中除芯片的Corner外,也考虑加工误差带来的影响。

此外PCB的3段的线长需要结合Layout的可实现性进行评估,也是一个制约因素。需要结合产品板的具体Placement和DRAM颗粒的Ball-map提出线长的区间。而3段线长(尤其是最后一个颗粒处的分支)会对最后眼图结果有很大影响。

6771

6771

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?