LUT 理解

本质就是个真值表

一、使用步骤

1.代码

`timescale 1ns / 1ps

module LUT(

input clk,

input a,

input b,

output reg [2:0] c

);

always@(posedge clk)begin

if((a==1'b1)||(b==1'b1))

c <= 3'd5;

else

c <= 3'd0;

end

endmodule

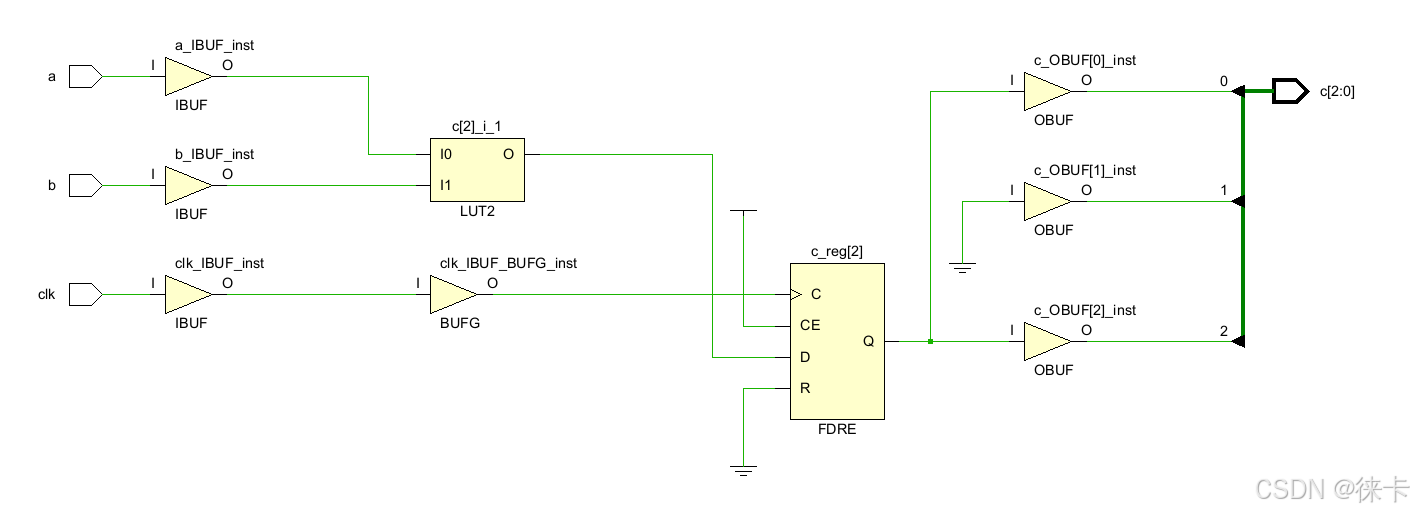

2.综合后的电路图

此时的LUT就是异或门的功能

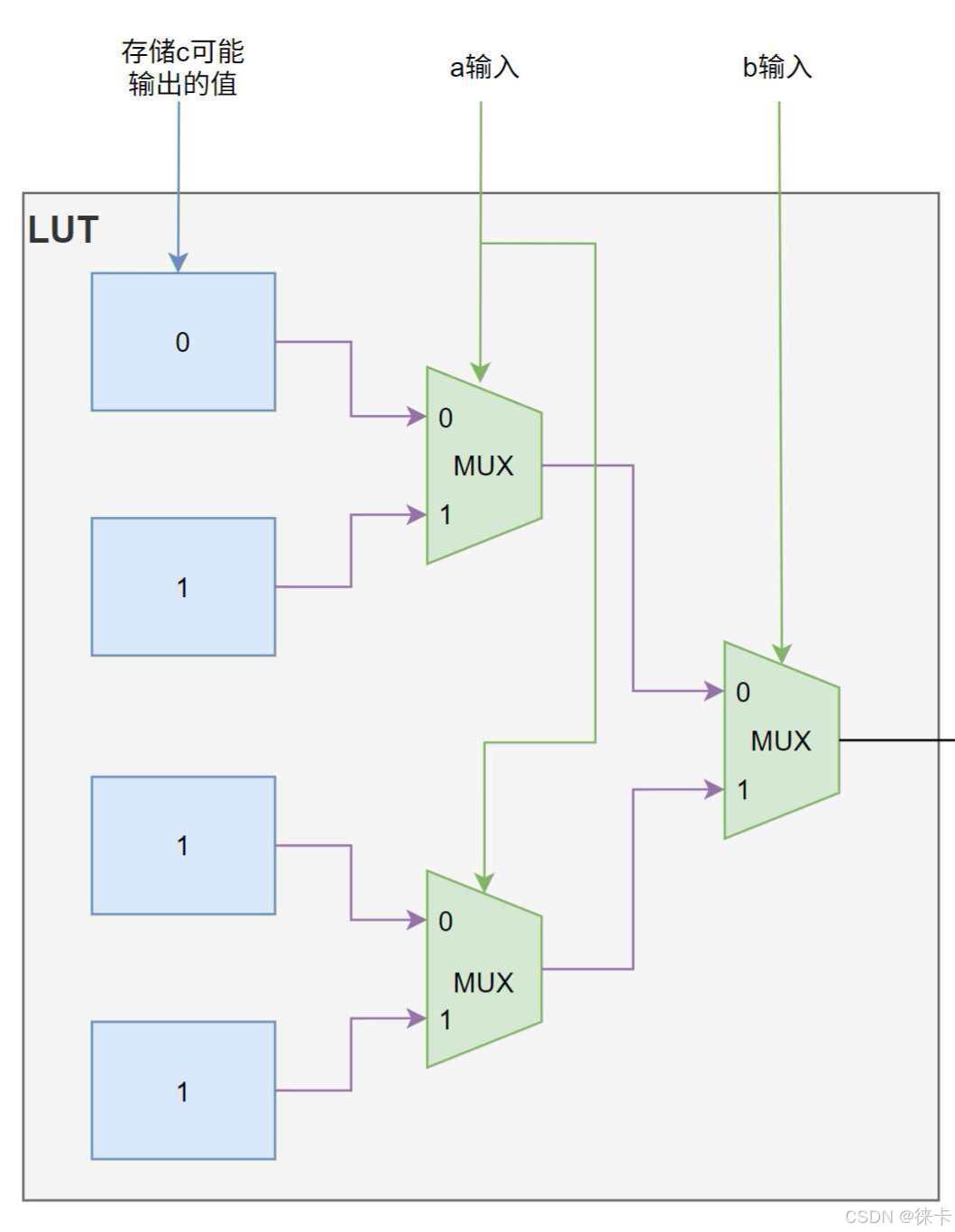

| 输入a | 输入b | 输出c |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

真值表实现功能如下:

总结

所以通常写的always块就是两部分构成,if()条件语句的Lut,以及赋值部分的D触发器。

564

564

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?