阻塞及非阻塞理解

FPGA语法基础学习

一、阻塞 =

assign a = 1;

assign b = a;

最终b = 1的结果经过了a变量,说白了信号就是“串联形式”一级一级往下传的。a就是那个阻塞变量

二、非阻塞 <=

always @(posedge clk ) begin

a <= 1;

end

always @(posedge clk ) begin

b <= a;

end

或者如下

always @(posedge clk ) begin

if(a==1)

b <= a;

end

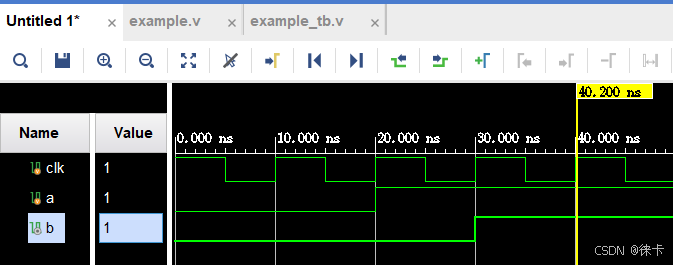

电路是同时运行,因为代码并行运行,同一时钟上升沿a被赋值为1,但是由于a传递到b端口有延迟,所以同一时刻b是采集到未赋值时刻a的值,而在下一个时钟周期b会变1。对应时序如下

总结

可以记忆为赋值语句落后于条件语句一个时钟周期。

阻塞与非阻塞赋值解析

阻塞与非阻塞赋值解析

1683

1683

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?