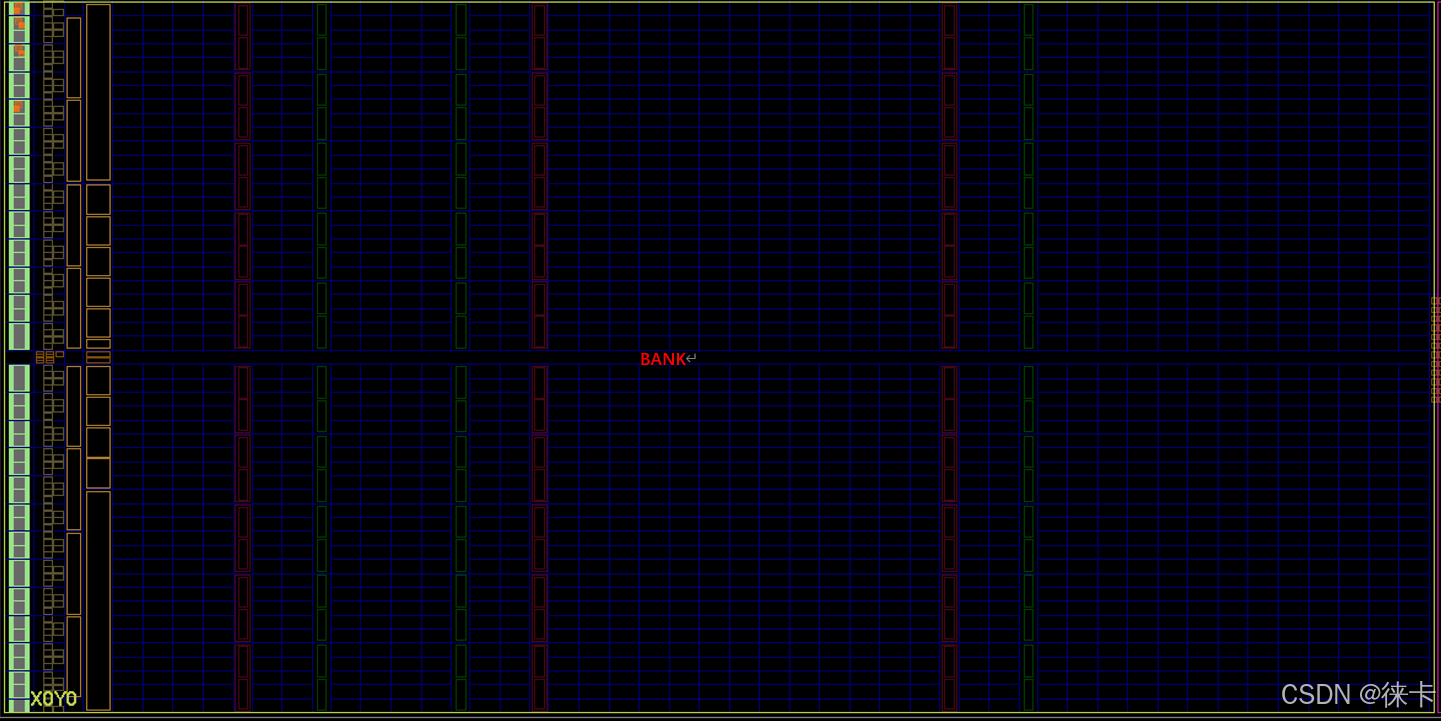

一、BANK整体视图

一个BANK整体资源

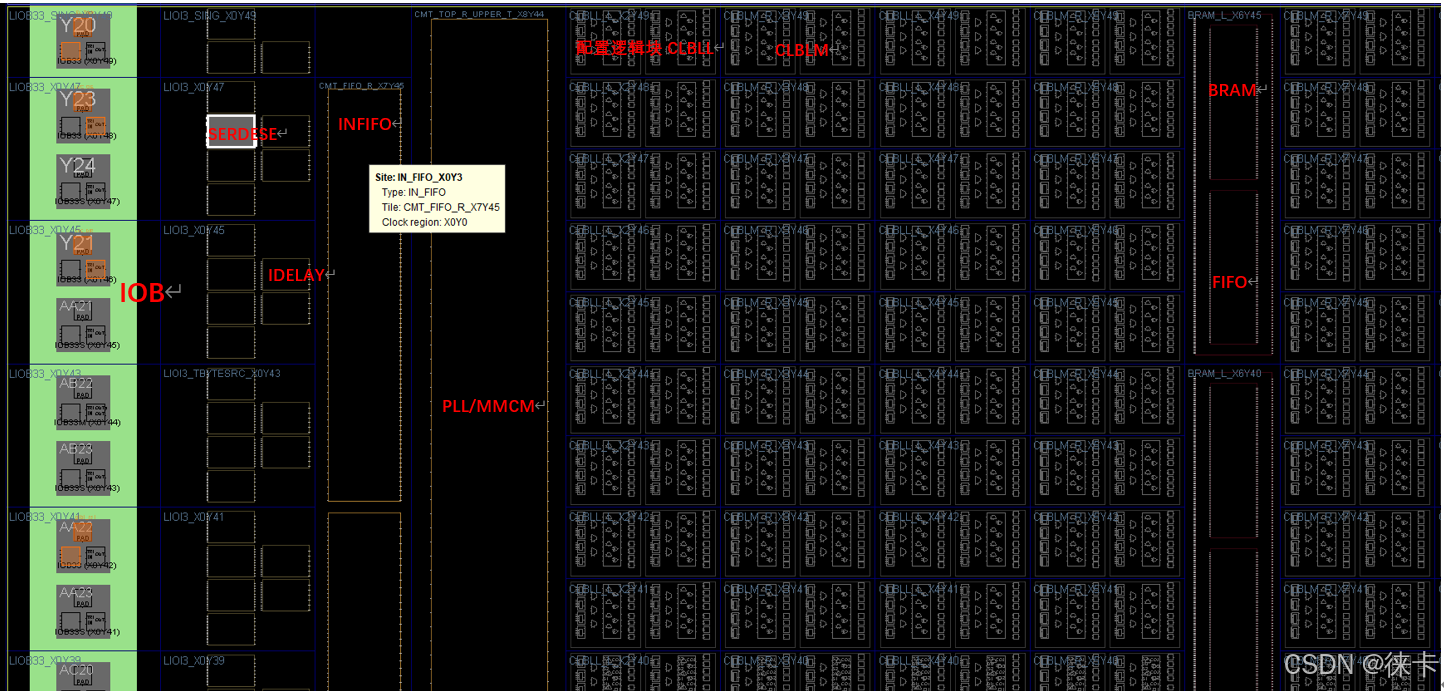

二、BANK局部放大视图

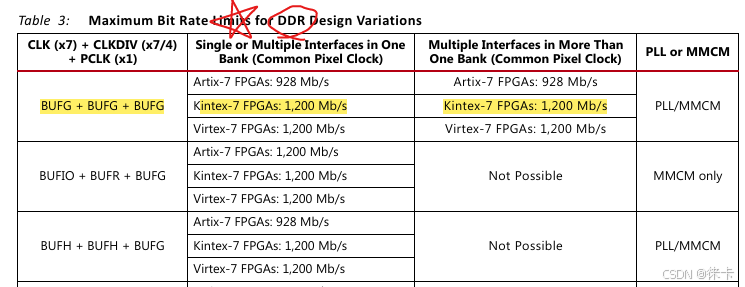

可编程输入输出单元IOB:最高速率要参考芯片说明书,我记得当时查文档时候DDR模式下能跑到1.2Gbps

idelay:对输入信号具有一定的延迟功能

i/oserdese:串并转换功能、数据对齐功能,仅记录我用的功能,主要用于高速数据传输。

可配置逻辑块CLB:

嵌入式块 RAM:

乘法/除法的累加单元DSP:

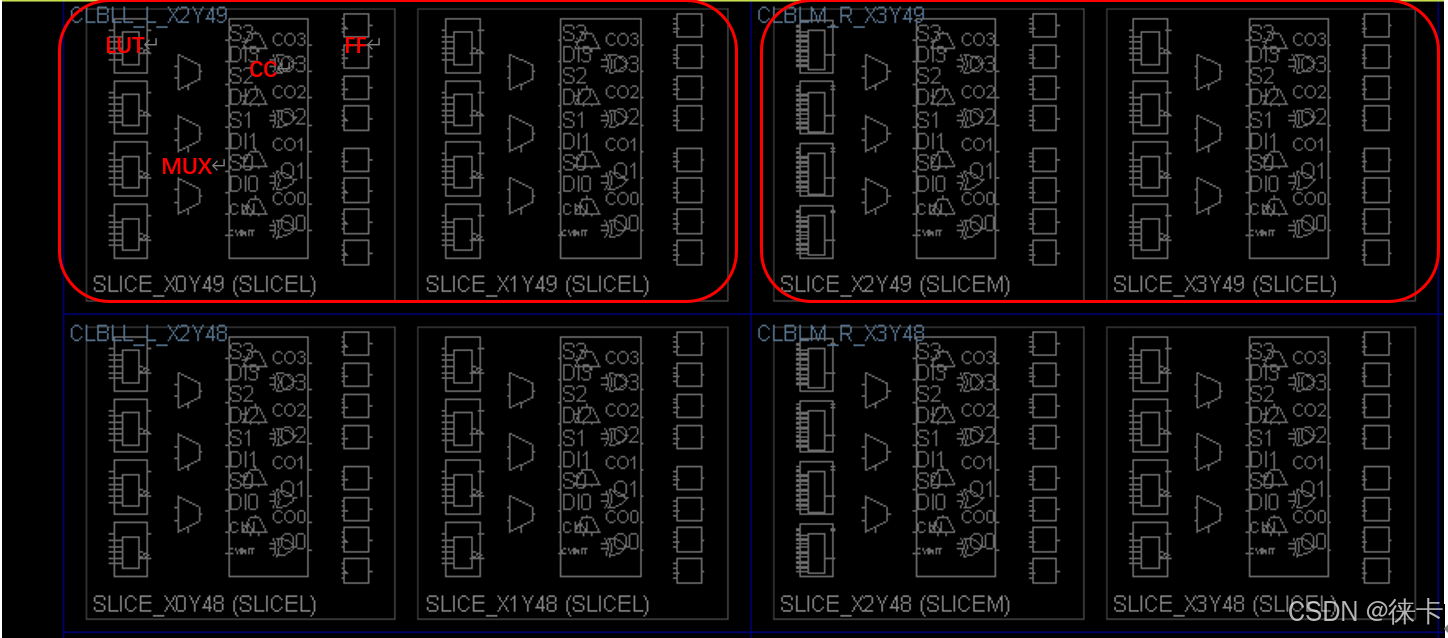

三、CLB放大视图

CLBLL :由两个SliceL组成,主要提供逻辑功能,用于实现组合逻辑。

CLBLM:由一个SliceM和一个SliceL组成,除了具备CLBLL的逻辑功能外,其内部的LUT还可以用作存储资源,如分布式RAM或移位寄存器。SliceM可以将自身的LUT用作于64位分布式RAM或移位寄存器,而SliceL不可以。

备注

仅用于记录日常学习,侵权必究

9313

9313

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?