系列文章目录

学习使用Vivado和SDK进行Xilinx ZYNQ FPGA开发 | (一)开始

学习使用Vivado和SDK进行Xilinx ZYNQ FPGA开发 | (二)学习方法选择

学习使用Vivado和SDK进行Xilinx ZYNQ FPGA开发 | (三)安装并破解Vivado和SDK

学习使用Vivado和SDK进行Xilinx ZYNQ FPGA开发 | (四)安装并破解Modelsim

学习使用Vivado和SDK进行Xilinx ZYNQ FPGA开发 | (五)ZYNQ-7000芯片摘要

学习使用Vivado和SDK进行Xilinx ZYNQ FPGA开发 | (六)ZYNQ-7000芯片的PS有什么资源

学习使用Vivado和SDK进行Xilinx ZYNQ FPGA开发 | (七)ZYNQ-7000芯片的PL有什么资源(本文)

摘要

ZYNQ-7000的PL相当于A7或者K7,其中低配相当于A7,高配相当于K7,资源有可编程逻辑块CLB、时钟管理MMCM/PLL、块RAM、DSP、IO、收发器、ADC,某些支持PCIe的型号还有Endpoint/Root接口。

一、可编程逻辑块CLB

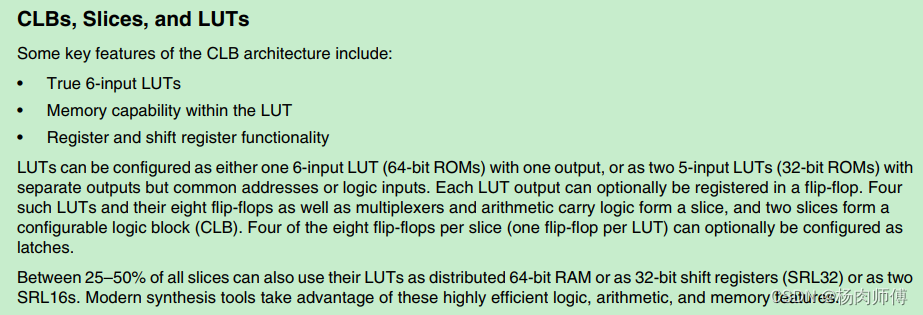

Configurable Logic Block(CLB)是PL的可编程逻辑资源,它的特点如下:

- LUT为6输入LUT,也可以当做2个非独立的5输入LUT用

- LUT的输出可以接到触发器

- 4个LUT和8个触发器和多路复用起和进位逻辑组成一个slice

- 2个slice组成一个CLB

- 25–50%的slice可以将里面的LUT用作分布式RAM或位移寄存器

二、时钟管理单元CMTs

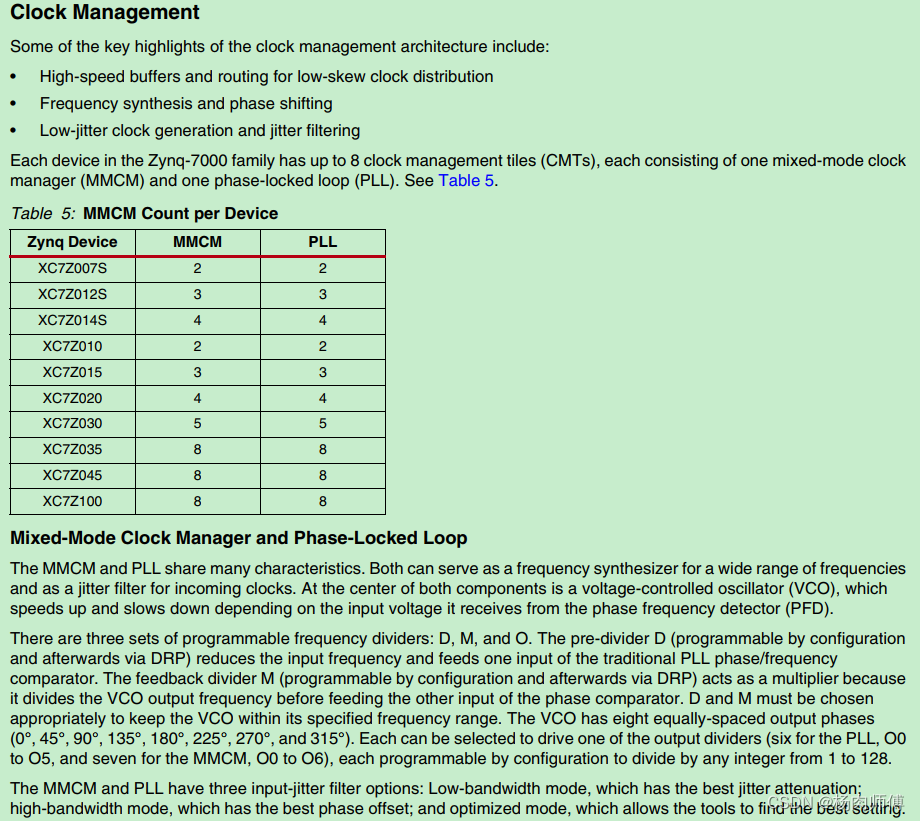

Zynq-7000系列的时钟管理单元clock management tiles最多有8个,我现在用的XC7Z010有2个,每个时钟管理单元包括一个MMCM和一个PLL。

现在的MMCM和PLL的核心部件都是VCO,可以倍频或者分频,同时还可以做一些特定值的相移。

Zynq-7000的时钟可以接到6种时钟线,包括BUFG、BUFR、BUFIO、BUFH、BUFMR、high-performance clock。

三、Block RAM

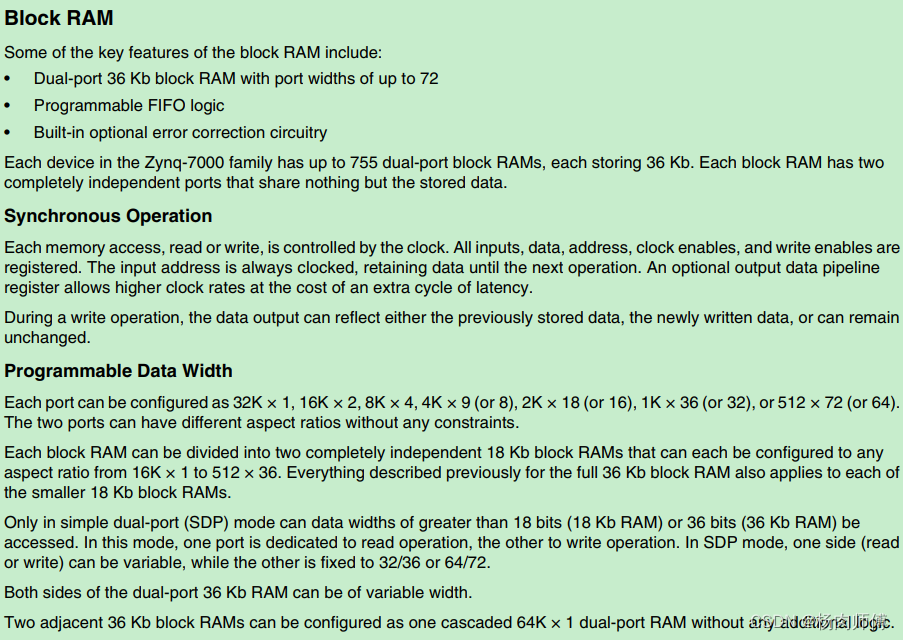

Zynq-7000的BRAM是双端口36Kb BRAM,带FIFO控制器,带ECC。

36K的RAM可以配置成32K1、16K2、8K4……51272。配置成小块的时候,如果能被36K整除,就能把36K利用完。

我现在用的XC7Z010有60个36K的BRAM。

FIFO控制器可以是单时钟或者双时钟,FIFO的宽度和深度可以自己设置,但是写和读的位宽需要是相同的。

四、DSP单元

DSP单元由一个25*18的乘法器和一个48位累加器组成,在乘法器前面还有一个前置加法器。

我现在用的XC7Z010有80个DSP。

五、I/O口

IO口根据型号和封装各有不同,高性能IO支持1866Mb/s的DDR3,集成有去耦电容,且可以支持三态、低功率或者高速IO操作。

所有的IO口都可以单独配置,IO delay可以配置成32级,每级增量为78ps或52ps。还支持串并转换和并串转换,每个IO口有一个8位的IOSERDES,最大可以支持8位的转换,如果用两个相邻引脚级联两个IOSERDES,还可以支持10位和14位的宽度。

六、串行收发器

Zynq-7000上包括GTX高速收发器,不同封装上的最高速度不一样。

七、PCIe接口

Zynq-7000上的PCIe是2.1,支持Gen1和Gen2。

八、ADC

Zynq-7000上还有2个12位的ADC,ADC最大可以选17个输入,参考电压可以选内部或者外部,还带温度和电源传感器,且可以从JTAG连ADC。

本文系列详细介绍了使用Vivado和SDK进行XilinxZYNQFPGA开发,涉及PL的CLB、CMTs时钟管理、BlockRAM、DSP、I/O功能、串行收发器、PCIe接口和ADC等资源。

本文系列详细介绍了使用Vivado和SDK进行XilinxZYNQFPGA开发,涉及PL的CLB、CMTs时钟管理、BlockRAM、DSP、I/O功能、串行收发器、PCIe接口和ADC等资源。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?