LVDS逻辑电平介绍及其应用要点

1.LVDS介绍

LVDS(Low-Voltage Differential Signaling)指低压差分信号,是美国国家半导体公(National Instruments)提出的高速信号电平模式,其支持的最高速率为3.125Gbps,一般应用于点到点的场合。

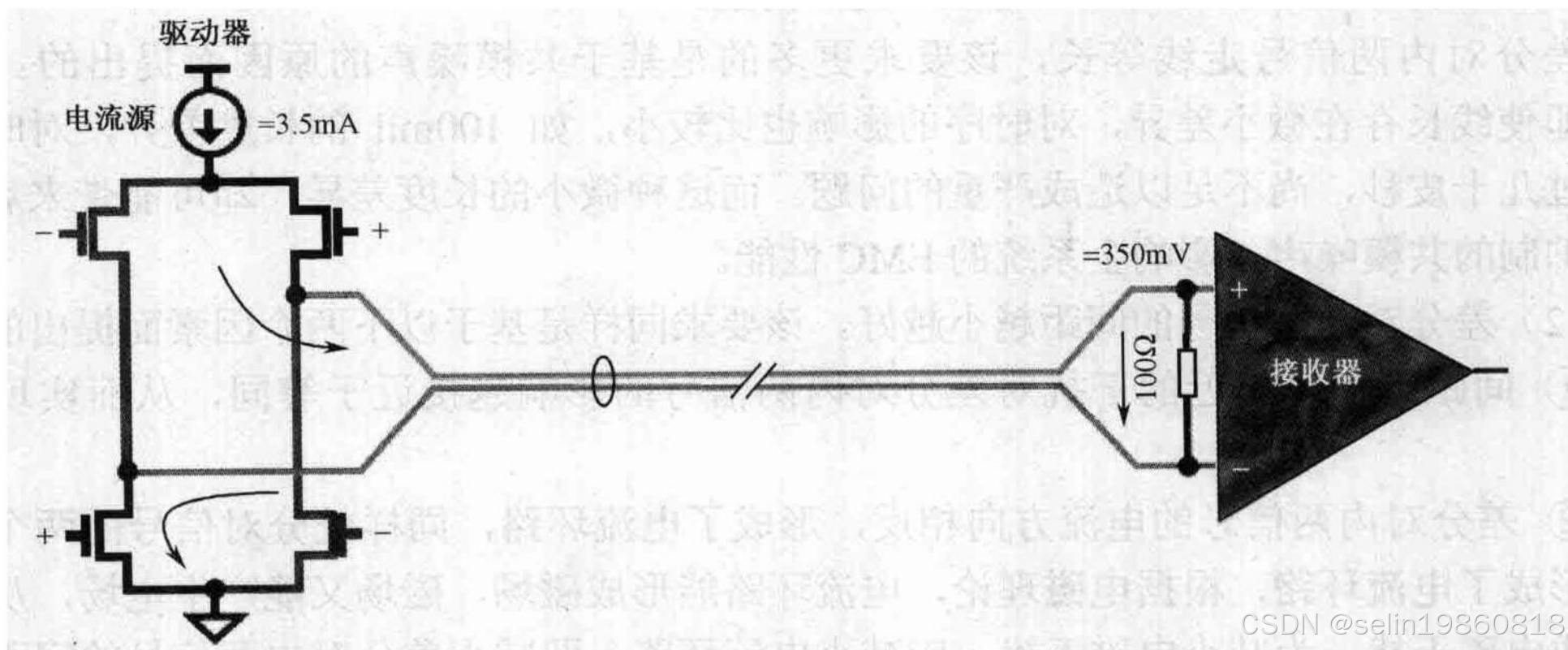

LVDS的应用场合有很多,如并行高速总线SPI4.2的1/O接口电平即为LVDS,其结构如图所示。

在发送方,由3.5mA 电流源提供驱动,在接收方,通过100电阻形成350mV的电压摆幅。当电流正向流动时,如上图中的箭头方向所示,产生逻辑“1”,反之,则产生逻辑“0”。由于摆幅小,有利于降低功耗。同时由于LVDS 采用电流驱动模式,因此与TTL、CMOS电平不同的是,LVDS功耗并不随工作频率的升高而相应增大,对单个端口而言,负载功耗仅为1.2mW(350mV×3.5mA=1.2mW),在高速逻辑电平中,LVDS的功耗是最小的。

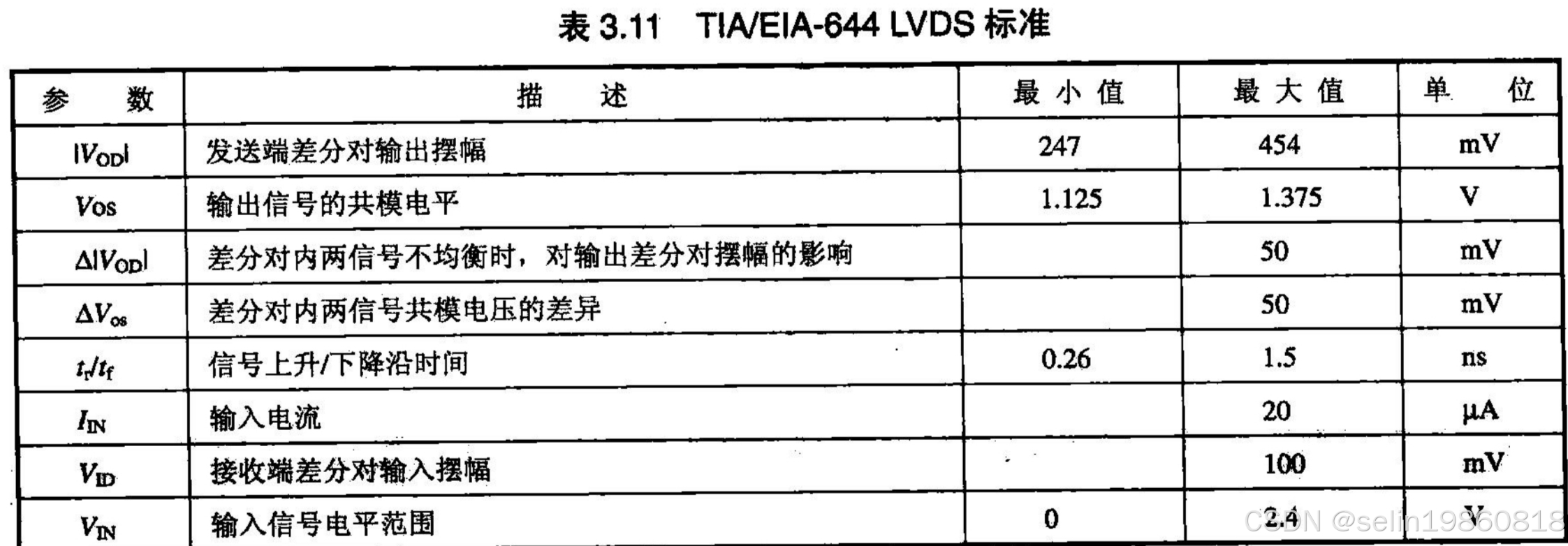

LVDS电平应遵循下表所定义的标准。

在应用中,设计者应重点关注以下几个方面:

(1)LVDS 接收方对信号的共模电平要求很弱,差分对内单个信号的电平范围在0~2.4V 均可,即LVDS的发送方和接收方对电源电压和直流偏置没有特殊要求,这种特性是LVPECL等电平所不具备的,这使得LVDS特别适宜于板间长距离信号的传输。由于输入信号电平范围为0~2.4V,而差分对摆幅最大值为454mV,因此输入端允许信号上携带的直流偏置电平范围为0.227~2.173V,当不满足此要求时,应采取AC(交流)耦合。

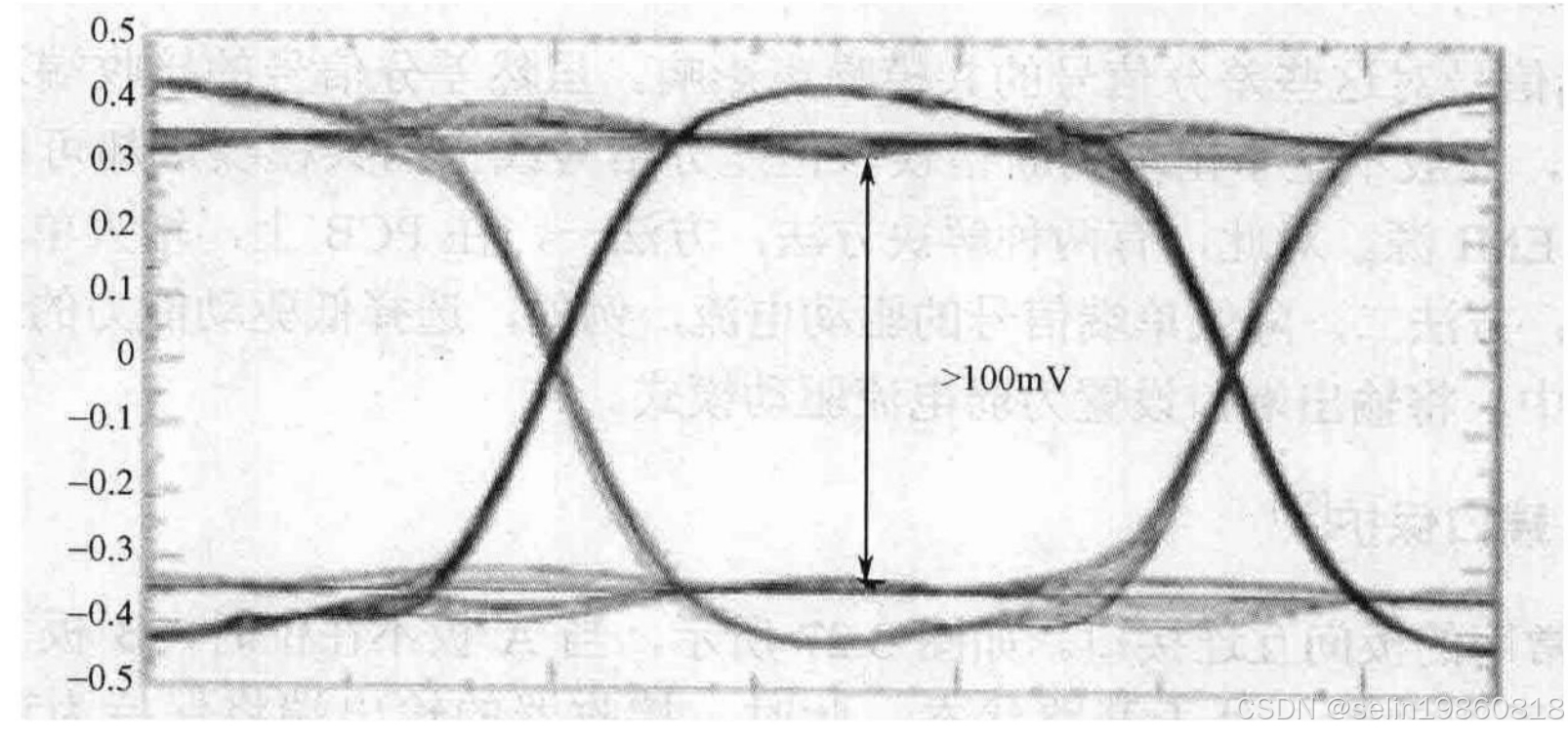

(2)LVDS 接收端对输入差分对信号摆幅的要求是100mV,可通过对眼图的测试来验证,如下图所示。

(3)端接方法。LVDS 电平通过在接收端增加100并联电阻以实现端接。相比LVPECL,端接方法简单。该端接电阻有两个作用,一方面用于实现电流向电压的转化,另一方面用于实现阻抗匹配。在某些情况下,该电阻可能已内置于接收端器件内,此时,不应该再外接匹配电阻。

(3)端接方法。LVDS 电平通过在接收端增加100并联电阻以实现端接。相比LVPECL,端接方法简单。该端接电阻有两个作用,一方面用于实现电流向电压的转化,另一方面用于实现阻抗匹配。在某些情况下,该电阻可能已内置于接收端器件内,此时,不应该再外接匹配电阻。

(4)信号沿变化速率较低。LVDS的边沿爬升时间约为0.5ns,因此信号沿变化速率是0.7V/ns,该速率甚至低于某些低速应用对信号变化沿速率的要求。在第8章将提到,信号变化沿速率越低,EMI值越小,所以LVDS电平有助于减小EMI。

(5)空闲输入引脚应浮空,以防噪声的引入;空闲输出引脚应浮空,以减小功耗.

(6)LVDS 不适用于数据速率为2Gbps以上的应用,对于这种应用,应考虑LVPECL或CML电平。

【案例】空闲输入引脚处理有误导致FPGA检测到错误输入某设计中,采用FPGA的LVDS接口作为板间高速互连接口,主控板FPGA上空闲的

LVDS引脚做上、下拉处理。在逻辑验证中,FPGA工程师发现,插入业务板瞬间,在主控板上未用的LVDS输入端口上,能不断检测到逻辑状态的变化。

【讨论】

设计者在检查PCB设计图的时候发现,由于主控板FPGA附近的空间被电容、电阻、信号过孔等占据,因此空闲LVDS引脚的上下拉电阻被放置在较远处,并通过约1000mil的走线连接到FPGA,走线附近存在大量的板间接口信号走线。

插拔业务板时,测量主控板上FPGA输入端空闲的LVDS引脚,测得摆幅超过100mV。在PCB设计时,设计者认为上、下拉只是为FPGA的空闲引脚提供一个确定的输入状态,因此并没有严格地执行差分对走线规则,导致插拔时相邻信号线所产生的干扰被引入至上下拉电阻到FPGA的走线。

LVDS 电平的摆幅很小,输入端出现100mV 的摆幅即可被认作为有效的逻辑状态,因此即便对空闲端口,也不能掉以轻心。在改板设计中,删除空闲端口的上下拉走线,问题得到解决。对该问题,还可以通过关闭FPGA内部的空闲端口予以解决。

【拓展】

在高速设计中,高速差分对常被作为板间互连接口信号,设计者应特别关注 TTL、CMOS 等单端信号对这些差分信号的共模噪声影响。虽然差分信号的接收端对共模噪声的抑制能力很强,一般不至于出现判断错误,但差分信号线上的共模噪声却可以产生对外辐射,成为一种EMI源。对此,有两种解决方法,方法一,在PCB上,增大单端信号与差分对信号的间距;方法二,降低单端信号的驱动电流,例如,选择低驱动能力的逻辑器件,或在FPGA设计中,将输出端口设置为弱电流驱动模式。

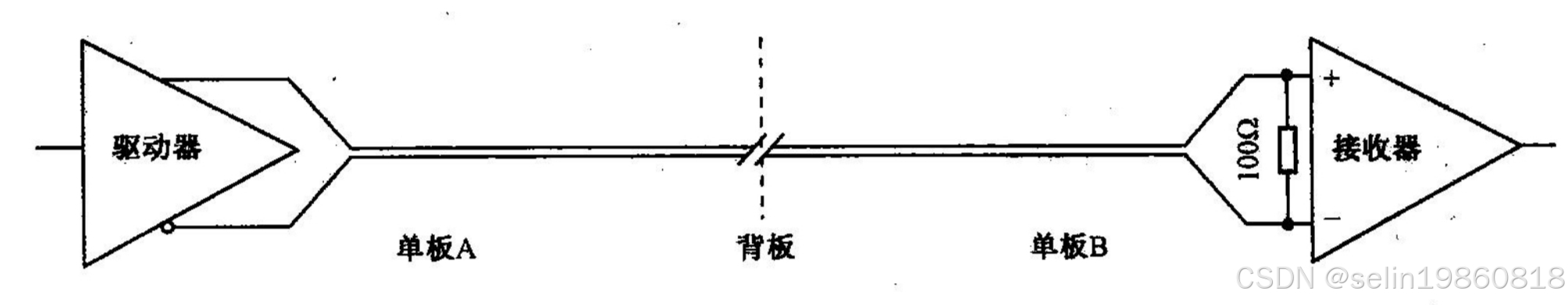

2.LVDS端口保护

LVDS 是常用的板间互连接口。如下图所示,当A板不在位时,B板LVDS接收器的输入端失去了驱动源,处于开路状态,此时,接收器的输出端将保持为逻辑“1”(由LVDS器件的内部逻辑保证),这种状态是正确的。 一旦输入端信号线(在B板上,从背板连接器到LVDS接收器之间的信号线)上引入了噪声,且达到接收端的阈值100mV,这种正确的状态将被打破,使接收器的输出端状态翻转为逻辑“0”。

一旦输入端信号线(在B板上,从背板连接器到LVDS接收器之间的信号线)上引入了噪声,且达到接收端的阈值100mV,这种正确的状态将被打破,使接收器的输出端状态翻转为逻辑“0”。

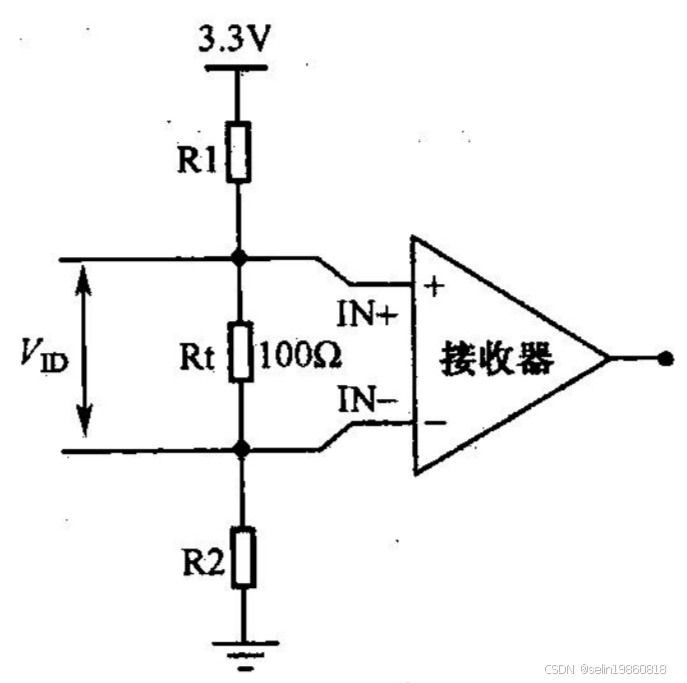

解决方法有多种,某些 LVDS接口器件内置有保护电路,使用时和普通 LVDS 器件一样,外加100端接电阻即可,某些LVDS接口器件则需外加保护电路,下文以外置保护电路为例,如下图所示,讨论对LVDS端口的保护。 除端接电阻Rt外,外置保护电路增加了R1和R2两个电阻以形成偏置电路。LVDS接收器输入端浮空时,偏置电路使 IN+和IN-之间形成正的偏置电平Vid,以提供更大的噪声冗余,即当噪声小于Vid时,接收器输出端仍可保持为逻辑“1”状态。以偏置电平 Vid等于25mV 为例(可实现25mV的噪声冗余),R1和R2阻值的计算方法为:

除端接电阻Rt外,外置保护电路增加了R1和R2两个电阻以形成偏置电路。LVDS接收器输入端浮空时,偏置电路使 IN+和IN-之间形成正的偏置电平Vid,以提供更大的噪声冗余,即当噪声小于Vid时,接收器输出端仍可保持为逻辑“1”状态。以偏置电平 Vid等于25mV 为例(可实现25mV的噪声冗余),R1和R2阻值的计算方法为:

上图中LVDS输入端的外置保护电路

Vid=25mV=100×3.3V/(RRi+ RR2+100)

Vos=1.25V=(Rp2+50) X3.3V /(RRi+ RR2+100)

其中,第一个等式是为得到25mV的偏置电平,

第二个等式是为保证输出共模电平(LVDS 要求输出共模电平的范围是1.125~1.375V,取中间值1.25V)。可得到RR1=8.25k,RR2=4.95k。

在PCB设计中需注意,R1、Rt、R2都应尽量靠近接收端放置,且偏置电流应远远小于LVDS驱动器提供的3.5mA电流,以免影响LVDS接收器的正常工作。

这种外部保护电路存在一定的局限性,例如,可能导致 LVDS输入信号的占空比失真,同时,增加的两个电阻也可能构成PCB布局的限制等。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?