EDA工具软件厂商三大巨头Synopsys、Cadence、Mentor。国内,华大九天。

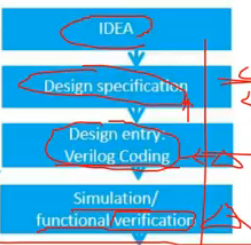

前端工作流程 一个推荐的参考书

目录

Verilog RTL

verilog 是硬件语言描述 (HDL),借鉴了C语言,专用来描述硬件。system Verilog 2012版本,是Verilog 上的扩展。

语义、语法:标准文档 《IEEE 1364 standard》

特点:描述数字电路。

抽象层:

- 门电路 Gate,

- RTL (寄存器传输级) ,用的是always,没有and or

- behavioral 乘法 加法

- layout

结构模型

由gate primitive 和/或其他模块构建。

它们使用逻辑门描述电路--就像你在电路实现中看到的那样

例子加法器 :

module adder_4_RTL(a,b,c_in,sum,c_out); //端口声明

output [3:0] sum; //端口方向、位宽为4

output c_out; 不指定位宽,默认1 位

input [3:0] a,b;

inuput c_in;

assign {c_out,sum} = a+b+c_in; //连续赋值语句

//{}为拼接符,{MSB,LSB}

endmodule

语言特点

1、并发性,硬件有并发性。concurrency

2、结构

3、过程化语句 begin end

4、Time 时序,

标识符

- 不能数字开头, 由[a,z][A,Z] [0,9] _ ¥下划线组成。大小号敏感,

- 注释:// /**/

- value 值: 0 表示低电平或 false, 1为高电平或 true, x 为未知的逻辑状态, z 为高阻态。

- 数字:

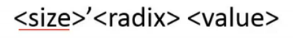

位宽、进制、值。比如: 16‘h FF00, 8'h ax=1010xxxx, 数字里可以加下划线 _, 增强可读性。12’b 000_111_010_100

位宽、进制、值。比如: 16‘h FF00, 8'h ax=1010xxxx, 数字里可以加下划线 _, 增强可读性。12’b 000_111_010_100 - Nets: 线

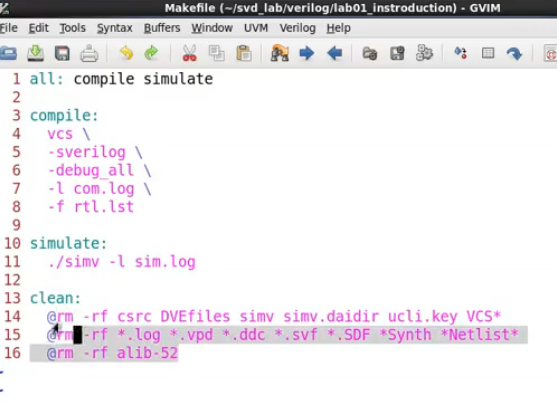

- makefile, 使用vcs 工具。

- 看波形文件.vpd 和 .VCD 文件,看仿真的结果对不对。逻辑综合可以用脚本执行,dc_shell,调用design compile和 DFT工具等。

逻辑综合输出的一些信息:

- #5 延迟会报warning

- operation typical, 电气规格类

- 约束类: 扇出、面积、最大delay

- 将RTL 电路进行映射,有面积。

- check timing,area ,max delay,

- 输出ddc 文件,RTL code 也写出来。

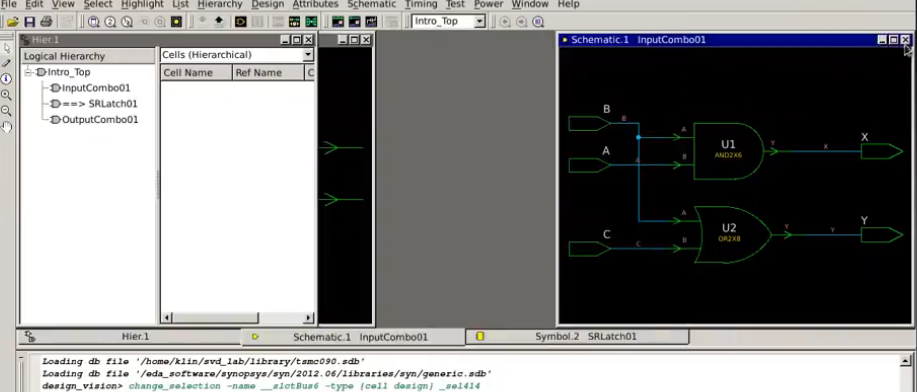

逻辑综合工具 design version,

可以在GUI界面,转换成具体的电路。大项目基本都是跑脚本。

设计工程师:逻辑语法OK, 会写test bench, 用verilog 写。

前端工具:逻辑仿真工具、逻辑综合工具、DFT(可测性设计)

语法介绍 syntax

reg,寄存器数据类型,

寄存器是数据储存单元的抽象,寄存器数据类型的关键字是 reg。

reg 类型数据的默认初始值为不定值x。通过赋值语句可以改变寄存器储存的值,其作用与改变触发器储存的值相当。

reg 型数据常用来表示“always”模块内的指定信号,常代表触发器。在“always”模块内被赋值的每一个信号都必须定义成reg 型。

reg 型数据的格式如下:

reg [n-1:0] 数据名1,数据名.2,⋯,数据名i;

reg A,C; //默认位宽1

A=1;

C=A;

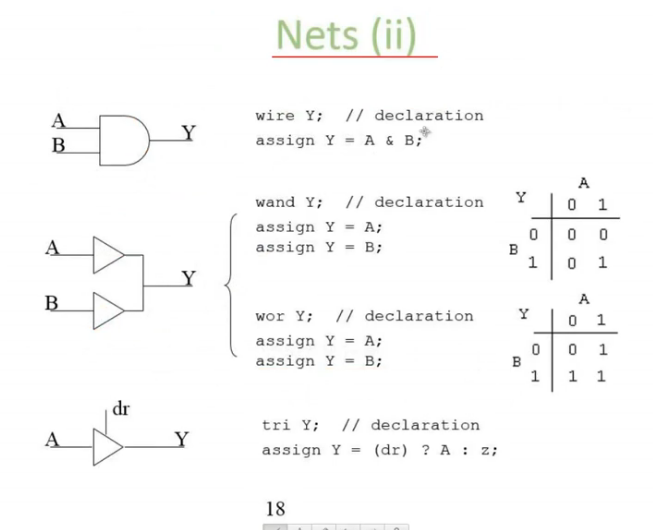

wire型

- 常用来表示 用以assign 关键字指定的组合逻辑信号。

- Verilog 程序模块中输入输出信号类型默认自动定义为 wire 型。

- wire 型变量通常是用来表示单个门驱动或连续赋值语句驱动的网络型数据。

wire 型属于网络类型,网络类型的变量不能储存值,而且它必须受到驱动器(例如门或连续赋值语句,assign)的驱动。

如果没有驱动器连接到网络类型的变量上,则该变量就是高阻的,即其值为z。

wire [3:0] busA; //位宽[MSB,LSB] 比如 [3:0]

wire a; //定义一个 1 位的wire 型数据

reg [1:0] busC;

busC=busA[2:1]; //在A 的[3:0]中选择 [2:1], 叫 位宽选择。连接是高位对高位,低位对低位。

-> busC[1]=busA[2]; //

-> busC[0]=busA[1];

wire和reg 的区别

Verilog中reg和wire类型的差异

存储与连线的区别:

reg 类型相当于存储单元,有记忆功能,可以保持上次的输入值,无需持续激励。

wire 类型相当于物理连线,主要用于表示硬件中的信号连接。

赋值方式的不同:

reg 变量只能在 initial 和 always 块中被赋值,

而 wire 变量只能通过 assign 语句进行连续赋值.

如果 reg 在组合逻辑(如 always@(*))中被赋值,它会被综合成连线(类似于 wire)。因此,reg 的本质是“可以被赋值的变量”,而不是“一定是寄存器”.

使用场景:

wire 通常用于表示直通路径,即输入有变化时,输出马上无条件地反映,适用于组合逻辑。

reg 用于需要触发才能改变状态的情况,适用于时序逻辑,如计数器、状态机等

integer & real 整数和实数

integer i,k; //没有初值

real r; // 默认值0.0

i=1;

r=2.9;

k=r; // k is rounded to 3

time 用于模拟时间测量的特殊数据类型

time my_time;

my_time=$time; //get currenr simulate time 仿真的时间

arrays 数组

- integer count[1:5]; //类型, 数组名字,元素个数,这里是1~5,共5个

- reg var[-15:16]; //32 个 1bit regs

- reg [7:0] mem[0:1023]; // 1024个 8 bit regs, 引用 mem[10]= 8'b 10101010

- 不支持二维 reg var[1:10] [1:10];

string 字符串

- reg [8*13:1] string_val; // 8位存一个字符,这里最多存1~13 =13个字符。先从最低位存

- string_val="hello word";

- 转义字符 : \n \t %% \\ \"

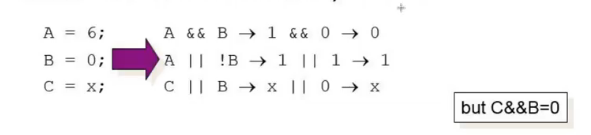

逻辑操作符

&& =and, II = or, ! =not

结果是1 0 或者 x, 占 1 bit

按位操作符:

1、& 按位与 |或 ~ 按位取反 ^ 按位异或XOR ~^ 按位同或

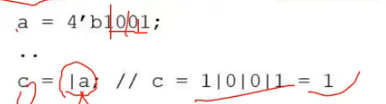

2、递减操作符:reduction operators

& | ^ , 与 或 异或, A= &B=0, B=1010, 从高位到低位,依次两位与操作,最终为 1 bit

~^ ~| ~&

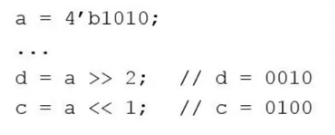

3、移位 >> <<

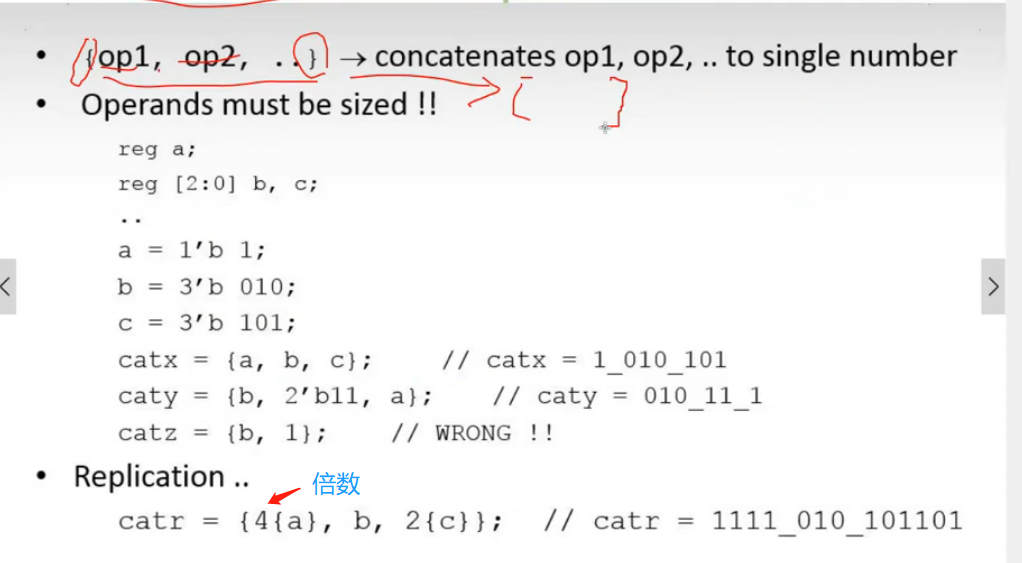

拼接符 {}

几个元素 拼成一个,每个元素要指明size

关系 运算符

> , < , >= , <=, 最终结果 1 0 x

1>0 结果为 -> 1

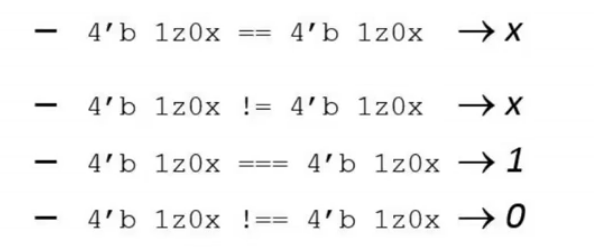

等号运算符

== , != ,=== 全等, z x 对应, !== 不全等,做验证会用到

+ - * / % , reg 是无符号数,

不同进制的标识: 2进制 b, 10进制 d, 8进制 O, 16进制 h.

reg [15:0] regA;

regA= -4'd12 ; //转为10进制, = 2^16 -12

908

908

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?