软件版本:Quartus Prime Pro 22.3

报错描述

在英特尔® Quartus® Prime Pro Edition 软件 22.3 版本中,工程已经存在 DisplayPort 英特尔® Arria® 10 FPGA IP 设计示例,此时新增 PLL Reconfig Intel FPGA IP 时,在 Analys & Synthesis 阶段将出现以下错误:

Error (13452): Verilog HDL Module Instantiation error at pclk_reconfig.v(35): module "altera_pll_reconfig_top" has no parameter named "WAIT_FOR_LOCK" File: D:/DP/PRJ/rtl/VX1_TX/AlteraIP/pclk_reconfig/pclk_reconfig/synth/pclk_reconfig.v Line: 35

报错产生原因

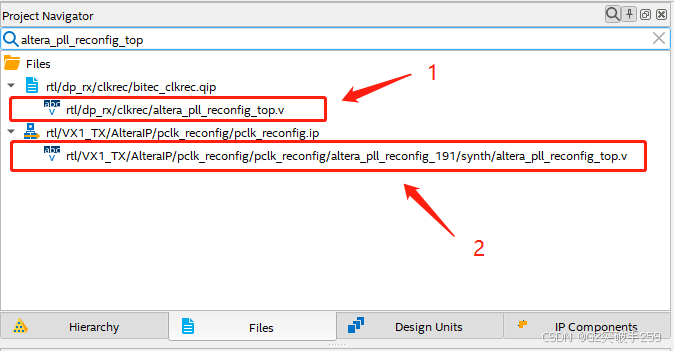

在 Project Navigator 窗口搜索 altera_pll_reconfig_top,可以发现,工程中存在两个 altera_pll_reconfig_top.v 同名文件。如下图所示:

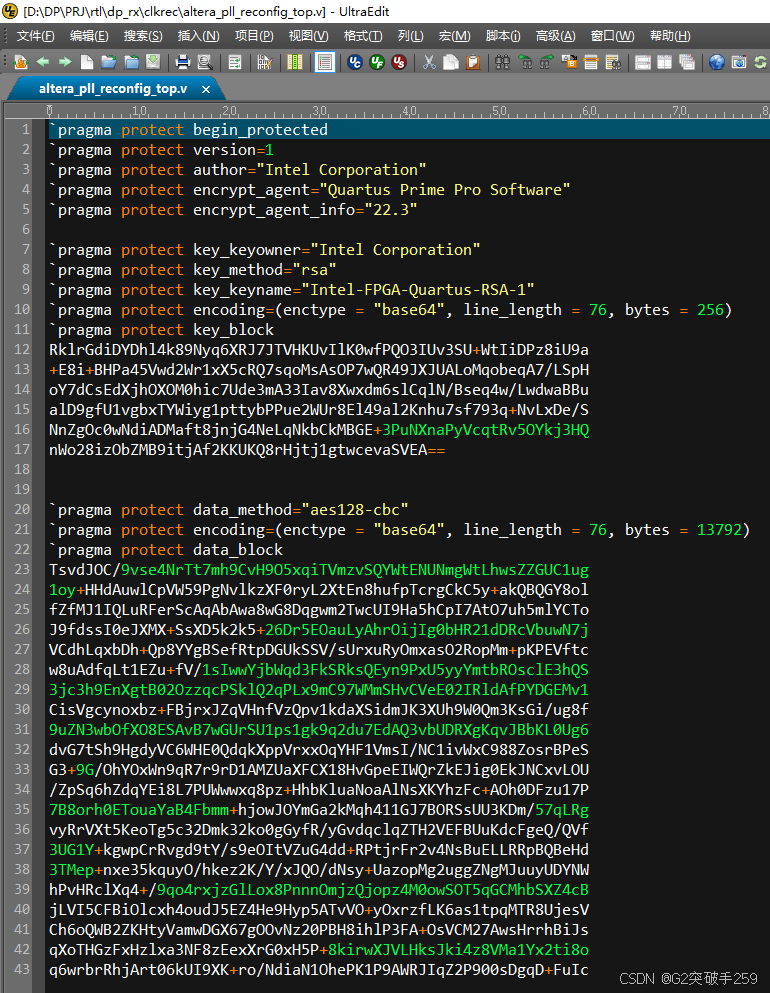

文件 1 为 DisplayPort 英特尔® Arria® 10 FPGA IP 设计示例中,bitec_clkrec 模块的文件,打开此文件,可以发现,此文件为加密状态,如下图所示:

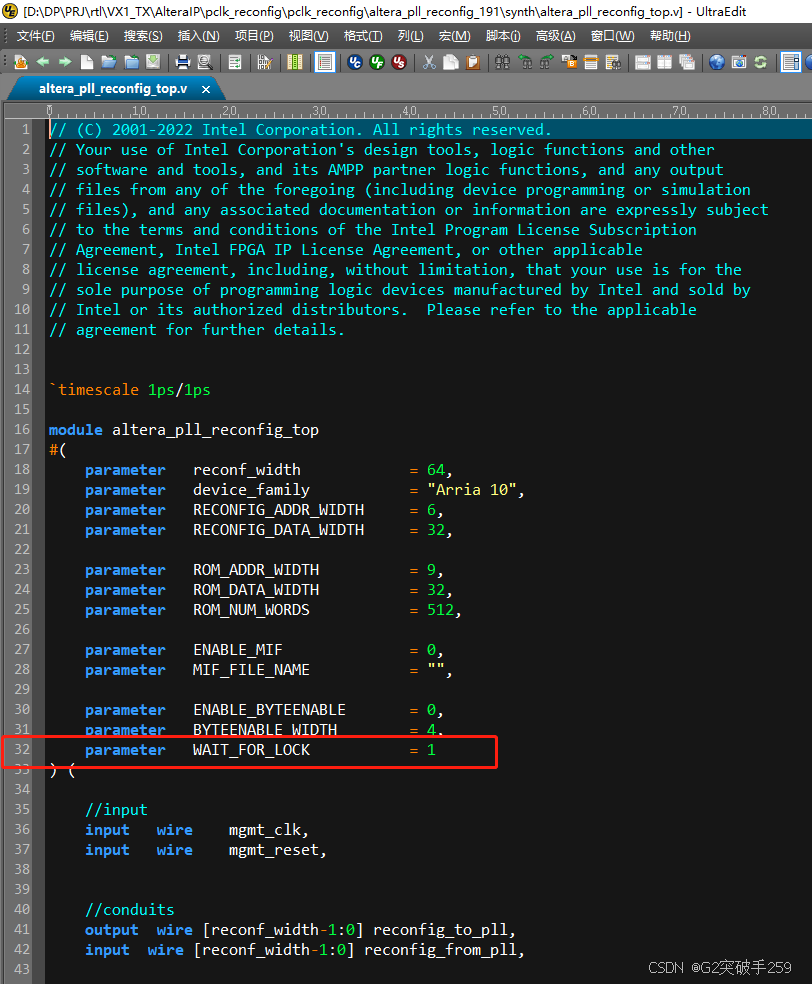

文件 2 为新增的 PLL Reconfig Intel FPGA IP 的文件,打开此文件,可以发现,此文件为非加密状态,如下图所示:

可以判断,bitec_clkrec 模块调用的加密 altera_pll_reconfig_top.v 文件与英特尔® Quartus® Prime Pro Edition 软件 22.3 版本中 PLL Reconfig Intel FPGA IP 调用的 altera_pll_reconfig_top.v 文件不一致,加密 altera_pll_reconfig_top.v 文件中不包含 WAIT_FOR_LOCK 参数,导致报错。

报错解决方案

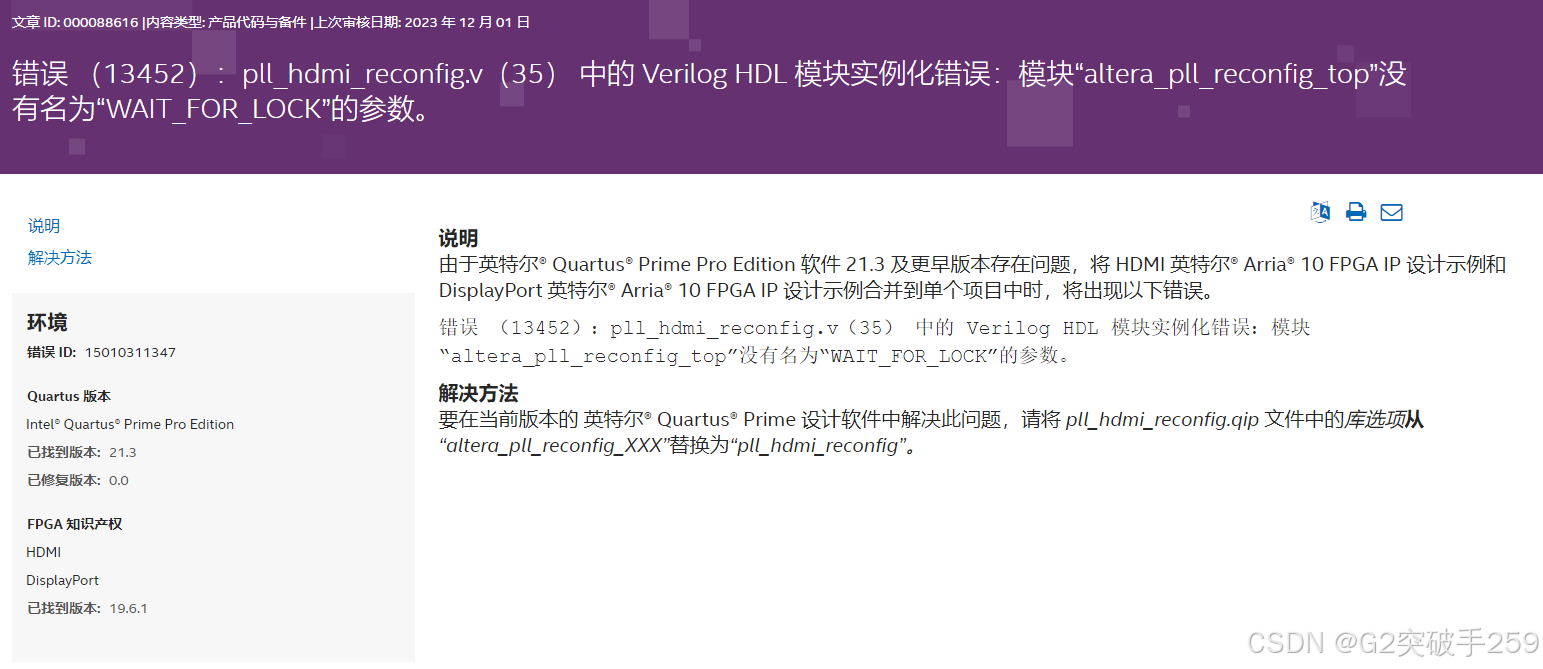

网上搜索一下,可以看到官方给出的解决方案:https://www.intel.cn/content/www/cn/zh/support/programmable/articles/000088616.html

这个方案是什么意思呢?首先我们需要了解一下 .qip文件的作用。

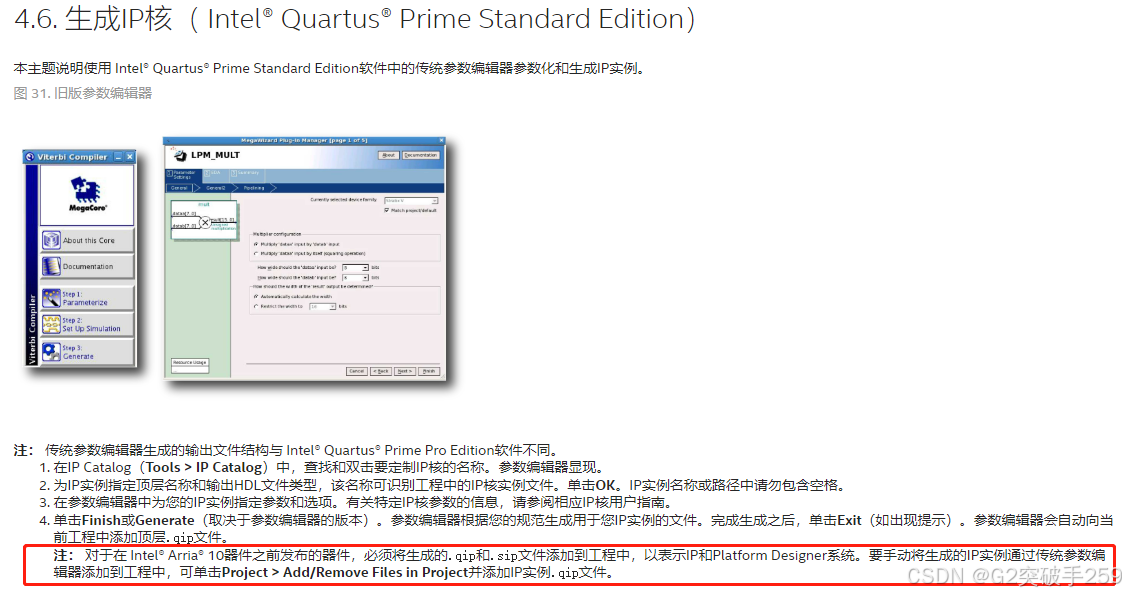

在文档 Intel® Quartus® Prime Standard Edition用户指南: 入门 第 4.6 章节:生成 IP 核中有如下描述:

在 EETOP 博客中有如下描述:

QIP 应该就是 Quartus IP 的缩写,就是我们在 Quartus II 里面是有 Altera 的 IP 的时候产生的一个文件,一般我们在使用 MegaWizard 插件管理器例化一个 IP 后会自动提示你是否需要将生成 IP 时产生的 QIP 文件加入到工程里。

现在逻辑设计都是基于层次架构来进行模块化的设计,所以很多时候我们会将不同模块的源文件存储在不同的目录下,特别是一些可以重复使用的模块更加应该如此。每个模块可能包含多个源文件,那么我在再次使用这些模块的时候是不是需要一个个地将所有源文件添加到工程里呢?答案是没有这种必要的,因为从上述 QIP 的介绍中,我们知道其实只需为每一个模块添加一个 QIP 文件即可。所以 QIP 文件对于逻辑设计的好处就是非常有利于我们的模块设计以及对于原始设计文件的管理。

使用 DeepSeek 搜索,得到以下回复:

在 Quartus 软件中,.qip文件(Quartus IP File)是用于管理和集成IP核(Intellectual Property Core)的配置文件。它的主要作用是帮助Quartus识别项目中使用的IP模块,并确保相关源文件、参数设置和依赖项在编译过程中被正确包含。

.qip 文件的核心作用:

- IP 核的声明与引用

当通过 Quartus 的 IP Catalog 工具生成一个 IP 核(如 PLL、存储器控制器、处理器等)时,系统会自动生成一个 .qip 文件。该文件记录了 IP 核的以下信息:

- 相关的 HDL 源文件路径(如 Verilog 或 VHDL 文件)。

- IP 核的配置参数(如时钟频率、数据宽度等)。

- 仿真模型(如 Testbench 文件)。

- 其他依赖项(如约束文件或第三方库)。

-

简化项目管理

通过将 .qip 文件添加到 Quartus 项目中,用户无需手动添加 IP 核的所有相关文件。Quartus 会根据 .qip 中的路径和配置自动处理 IP 核的集成,从而减少人为错误并提高效率。 -

版本控制与协作

.qip 文件允许团队共享 IP 核配置。只需传递 .qip 文件(而非所有 IP 相关文件),其他人即可复现相同的 IP 设置,确保项目一致性。

典型应用场景示例:

- 生成 IP 核时:使用 Quartus IP Catalog 创建 IP(例如一个 FIR 滤波器),工具会自动生成

.qip和.v/.vhd文件。将 .qip 添加到项目后,Quartus 会编译该 IP。 - 复用 IP 配置:若需在不同项目中重用同一 IP 核,可直接复制其 .qip 文件,确保配置参数和路径正确。

.qip 文件与其他文件的区别:

- .qsf(Quartus Settings File):存储整个项目的全局设置(如器件型号、引脚分配),而 .qip 仅针对 IP 核。

- .qsys(Platform Designer 系统文件):用于定义片上系统(如总线连接、IP 互联),而 .qip 用于单个 IP 的配置。

- .tcl 脚本:可通过脚本动态生成或修改 .qip 内容,但 .qip 本身是静态配置文件。

注意事项:

- 路径正确性:.qip 文件中引用的文件路径需与项目目录结构匹配,否则编译会报错。

- 避免手动修改:建议通过 Quartus 工具生成或更新 .qip,直接编辑可能导致配置错误。

- 版本兼容性:不同 Quartus 版本的 .qip 格式可能略有差异,跨版本使用时需注意兼容性。

通过合理利用 .qip 文件,用户可以高效管理 FPGA 设计中的复杂 IP 核,提升开发流程的可靠性和可维护性。

操作流程

需要保证 bitec_clkrec.qip 与 PLL Reconfig Intel FPGA IP 所调用的 altera_pll_reconfig_top.v 文件是同一个文件。用非加密的 altera_pll_reconfig_top.v 文件替换掉加密的 altera_pll_reconfig_top.v 文件即可。或者修改 bitec_clkrec.qip 文件的调用路径,让他调用 PLL Reconfig Intel FPGA IP 文件夹下的非加密的 altera_pll_reconfig_top.v 文件。再次编译工程,报错已经解决。

438

438

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?