一、流水线

总结指令流水线 CPI 的优化技术,

如基于硬件还是软件, 主要思想, 对应了 CPI 公式的哪个分量等。

现代处理器通过流水线来实现指令级并行(ILP),提高性能。流水化处理器的CPI为:

流水线 CPI = 理想流水线 CPI + 结构化冒险停顿 + 数据冒险停顿 + 控制冒险停顿

停顿的单位是每条指令。主要的ILP技术有:

| 技术 | 降低CPI的哪一部分 | 基于硬件/软件 |

|---|---|---|

| 前推、转发 | 数据冒险停顿 | 硬件 |

| 基本动态调度(记分牌) | 数据冒险停顿 | 硬件 |

| 采用重命名的动态调度(Tomasulo) | 数据冒险停顿 | 硬件 |

| 延迟分支和基本分支预测 | 控制冒险停顿 | 硬件 |

| 动态分支预测 | 控制冒险停顿 | 硬件 |

| 循环展开 | 控制冒险停顿 | 软件 |

| 编译器流水线调度 | 数据冒险停顿 | 软件 |

二、依赖

简单描述什么是真数据依赖(True data dependence),输出依赖(Output dependence),

反依赖(Antidependence), 寄存器重命名(Register renaming)

- 真数据依赖/流依赖 True data /flow dependence【RAW】

- S1定义了一个值,随后S2使用了这个值。

记作 S 1 δ f S 2 记作 S1\ \delta^f\ S2 记作S1 δf S2 - 举例:值-a

- S1定义了一个值,随后S2使用了这个值。

a = b + c // S1

d = a + c // S2

- 输出依赖(Output dependence)【WAW】

- 两个语句都定义了一个值。

记作 S 1 δ o S 2 记作S1\ \delta^o \ S2 记作S1 δo S2 - 举例:值-a

- 两个语句都定义了一个值。

a = b + c // S1

a = d // S2

- 反依赖(Antidependence)【WAR】

- S1使用了一个值,而随后S2定义了这个值。

记作 S 1 δ a S 2 记作S1\ \delta^a \ S2 记作S1 δa S2 - 举例:值-b

- S1使用了一个值,而随后S2定义了这个值。

a = b + c // S1

b = c + d // S2

- 输入依赖(Output dependence)【RAR】

- 两个语句都使用了一个值。

记作 S 1 δ i S 2 记作S1\ \delta^i \ S2 记作S1 δi S2 - 举例:值-b

- 两个语句都使用了一个值。

a = b + c // S1

d = b + 2 // S2

- 寄存器重命名(Register renaming)

- 作用:

- 消除假数据冒险:WAR,WAW

- 当指令执行发生错误而取消时,后面的指令可以保证现场的精确

- 思路:

- 当一条指令写结果寄存器时,不直接写入,而是先写到一个中间寄存器过渡一下

- 当这条指令提交时,再写到结果寄存器中

- 方法:

- 使用重排序缓冲(Reorder Buffer,ROB)来实现;

- 将逻辑寄存器(Architecture Register File,ARF)扩展来实现;

- 使用统一的物理寄存器(Physical Register File,PRF)来实现寄存器重命名。

- 作用:

三、cache

(1)一个计算机系统用 32 位内存地址。它有 128KB 8 路组相联缓存,每个块大小为 64B。

计算标签(tag)、缓存索引(cache index) 和块偏移(block offset)的位数。

解:

- 块偏移(block offset):64=26—>6位

- 缓存索引(cache index):128KB/(8*64B)=217/(23*26)=28—>8位

- 标签(tag):32-6-8=18位

(2)处理器有一个小型直接映射缓存, 能够容纳四个缓存块。

内存是按字节寻址的, 每个缓存块由 32 字节组成。

处理器使用 12 位内存地址。 假设每个缓存块的初始标签值如下:

| 块 | 标签 |

|---|---|

| 00 | 00110 |

| 01 | 00001 |

| 10 | 00000 |

| 11 | Invalid |

处理器从以下十进制地址顺序读取数据: 32, 48, 64, 128。

对于上述每个地址,指出缓存访问将导致命中还是未命中。 并给出详细过程。

解:

- ( S , E,B,m)–>(2,1,5,12)

- b-块偏移(block offset):32=25—>5位

- s-缓存索引(cache index):4)==22—>2位

- (m-s-b)-标签(tag):12-5-2=5位

- 读32–未命中

- 32=0b10 0000=0b01 00000:tag=00000,cache index=01,offset=00000;

- 与缓存中块01的tag-00001不匹配,故不命中;

- 替换操作后:块01,标签00000;

- 读48–命中

- 48=0b11 0000=0b01 10000:tag=00000,cache index=01,offset=10000;

- 与缓存中块1的tag匹配(读32不命中后替换了之前的块1),故命中;

- 读64–命中

- 64=0b100 0000=0b10 00000:tag=00000,cache index=10,offset=00000;

- 与缓存中块10的tag-00000匹配,故命中;

- 读128–不命中

- 128=0b1000 0000=0b1 00 00000:tag=00001,cache index=00,offset=00000;

- 与缓存中块00的tag-00110匹配,故不命中;

- 替换操作后:块00,标签00001;

四、内存访问时间

(1)简述平均内存访问时间公式,总结附录 B 的 6 种缓冲优化技术。

解:

- 平均内存访问时间公式

- 平均内存访问时间 = 命中时间 + 缺失率 x 缺失代价

- 缺失:

- 冷不命中:首次访问一个块时缺失【增大块的大小,但可能增加其他的缺失】

- 容量不命中:缓存的所有行均已满时发生丢失【增大缓存】

- 冲突不命中:Cache中仍有空行,主内存块与Cache中已填充的行发生冲突(即使有可用的空位,该块也试图占用已填充的行);冒险缺失会随相联度的增大而减小【采用全相联,但硬件实现成本高,可能降低处理器时间频率】

- 6种缓冲优化技术

| 技术 | 目的 | 优 | 劣 | 衡量折中 |

|---|---|---|---|---|

| 增大块大小 | 降低缺失率 | 降低冷不命中;更好利用空间局部性 | 增加容量不命中、冲突不命中的代价 | 低级存储器为高带宽、高延迟:大块;低带宽、低延迟:小块 |

| 增大缓存 | 降低缺失率 | 降低容量不命中 | 可能延长命中时间,增加成本和功耗 | |

| 提高相联度 | 降低缺失率 | 降低冲突不命中 | 提高缺失代价 | 经验规律:采用八路组相联和全相联一样有效 |

| 多级缓存 | 降低缺失代价 | 加快缓存速度,扩大缓存容量 | 二级缓存的缺失率更高,偏向减少缺失,采用更高相联度和更大的块 | |

| 读缺失优先于写缺失 | 减少命中时间 | 对于RAW,若未写完、还在写入缓冲区,则让读缺失先检查写入缓冲区的内容 | ||

| 索引缓存时避免地址转换 | 减少命中时间 | 缓存中使用物理地址 | 少部分计算采用:地址空间保护等原因 | 一部分页偏移量索引缓存,标志匹配采用物理地址–>索引读取缓存的同时,进行地址的转换 |

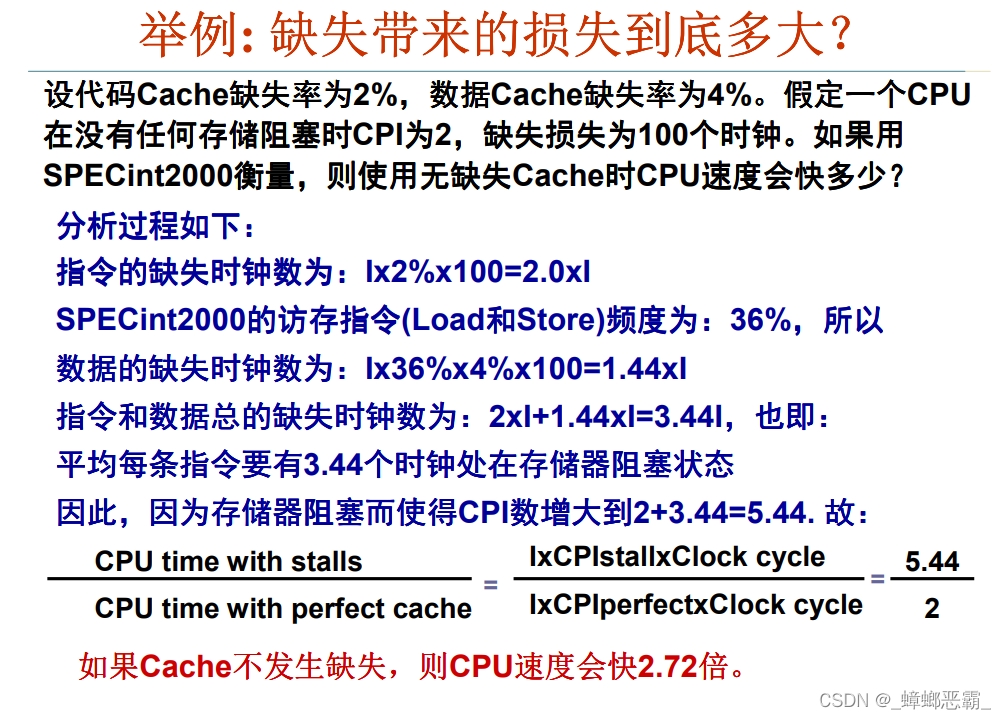

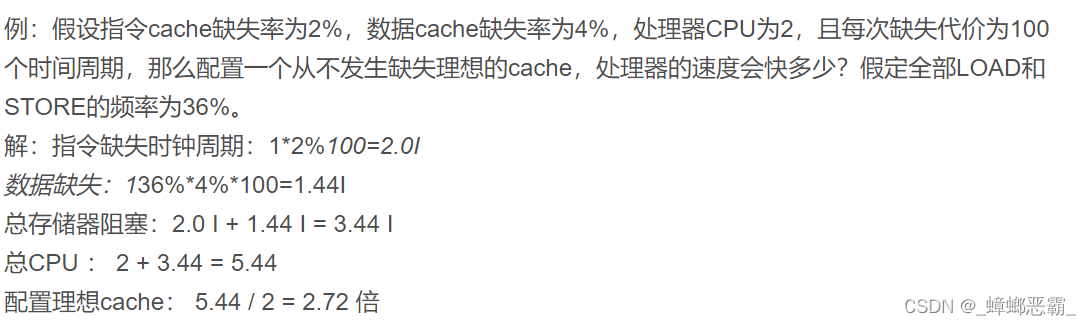

(2)计算题: 假设存在一个计算机,CPI 是 2(没有储存器停顿(Memory stalls)),仅有载入/储存指令进行数据访问,并且载入/储存的指令的占比是 36%。

假如缓存命中时间是 0, 缺失代价(Miss penalty)是 40 个时钟周期, 指令缓存缺失率(Instruction miss rate)是2%, 数据缓存缺失率(Data miss rate)是 4%。

请计算指令缓存和数据缓存平均内存访问时间、不使用 cache 技术的 CPU 的平均 CPI(等同miss rate 100%),和使用了 cache 技术相对无 cache 计算机获得的加速比。

解:

- 1)指令缓存和数据缓存平均内存访问时间

- 命中时间=0

- 指令缓存缺失率=2%, 数据缓存缺失率= 4%

- 缺失代价=40个时钟周期

- 指令缓存平均内存访问时间:0+0.02*40=0.8 (个时钟周期)

- 数据缓存平均内存访问时间:0+0.04*40=1.6(个时钟周期)

- 2)不使用 cache 技术的 CPU 的平均 CPI(等同miss rate 100%)

- 没有储存器停顿的CPI:2

- 缺失周期:指令缓存不命中+数据缓存不命中

- 因为指令缓存不命中的缺失周期:IC*1*40=IC*40

- 因为数据缓存不命中的缺失周期:IC*0.36*1*40=IC*14.4

- 平均CPI:2+40+14.4=56.4

- 3)使用了 cache 技术相对无 cache 计算机获得的加速比

- 有Cache的平均CPI:

- 没有储存器停顿的CPI:2

- 缺失周期:指令缓存不命中+数据缓存不命中

- 因为指令缓存不命中的缺失周期:IC*0.02*40=IC*0.8

- 因为数据缓存不命中的缺失周期:IC*0.36*0.04*40=IC*0.576

- 平均CPI:2+0.8+0.576=3.376

- 加速比: 56.4/3.376=16.7

- 有Cache的平均CPI:

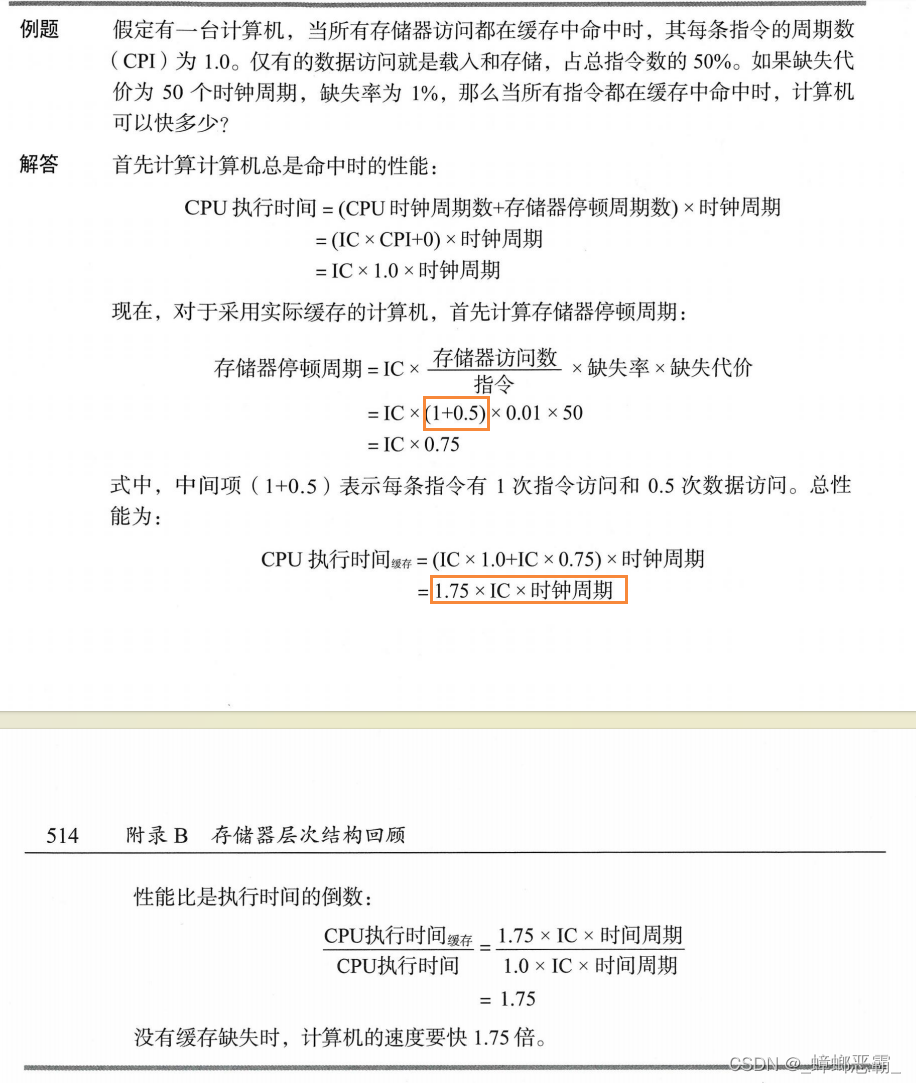

这里感觉有点问题(2024/5/8经评论区指点,已改正合理版的想法):

- 解答的依据1:

- 解答的依据2:

- 解答的矛盾/问题:(2024/5/8经评论区指点,已改正【合理版的想法】)

- 合理版的想法是:下面的问题:指令缓存缺失率=数据缓存缺失率= 1%

- 缺失周期(总存储器阻塞):

- 因为指令缓存不命中的缺失周期:IC*0.01*50=IC*0.5

- 因为数据缓存不命中的缺失周期:IC*0.5*0.01*50=IC*0.25

- 总CPI:1IC+IC*0.5+IC*0.25=1.75IC

- 加速比:1.75/1=1.75

- 缺失周期(总存储器阻塞):

- 如果按上面的解法:下面的问题应该是

- 缺失周期(总存储器阻塞):0.5*0.01*50=0.25

- 总CPI:1+0.25=1.25

- 加速比:1.25/1=1.25

- 合理版的想法是:下面的问题:指令缓存缺失率=数据缓存缺失率= 1%

1317

1317

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?