笔记根据正点原子官方教学视频第33讲

时间:2025/2/7

【第一期】手把手教你学领航者&启明星ZYNQ之FPGA开发篇【真人出镜】FPGA教学视频教程_哔哩哔哩_bilibili

有错误的地方希望可以告诉博主

前言

什么是以太网帧

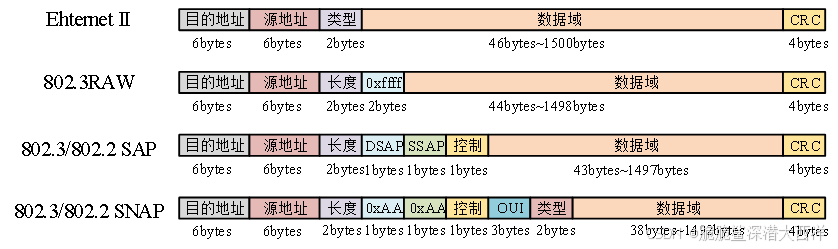

在以太网链路上的数据包称作以太帧。 以太帧有很多种类型。不同类型的帧具有不同的格式和MTU(Maximum Transmission Unit最大传输单元)值。 常见的以太网帧格式有Ethernet II、Ethernet802.3 RAW 等。

以太网帧格式区分

以下是Ehtemet II和Ethernet802.3 的一种以太帧网帧格式:

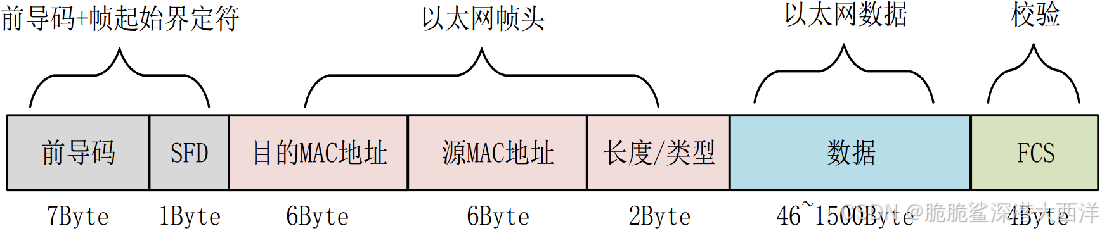

这里需要了解的是,7Byte 长度的前导码固定为:7个0x55;1Byte 长度的 SFD 固定为:0xd5。

区分长度和类型的依据:小于等于1500是长度,大于1500是类型。

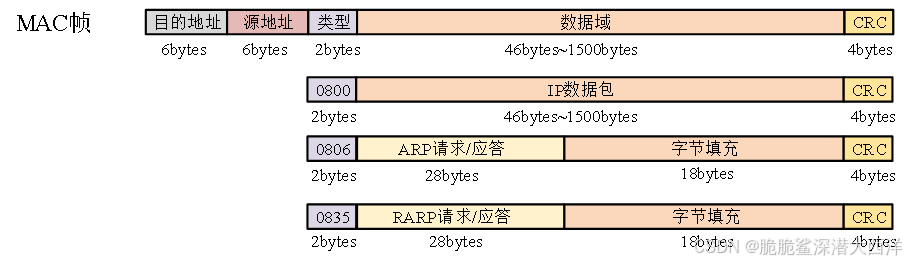

以太网MAC帧数据格式:

当类型为0800时:IPv4协议。

当类型为0806时:ARP协议:知道IP地址获取MAC地址。

当类型为0835时:RARP协议:知道MAC地址获取IP地址。

其余类型用到以后再补充。

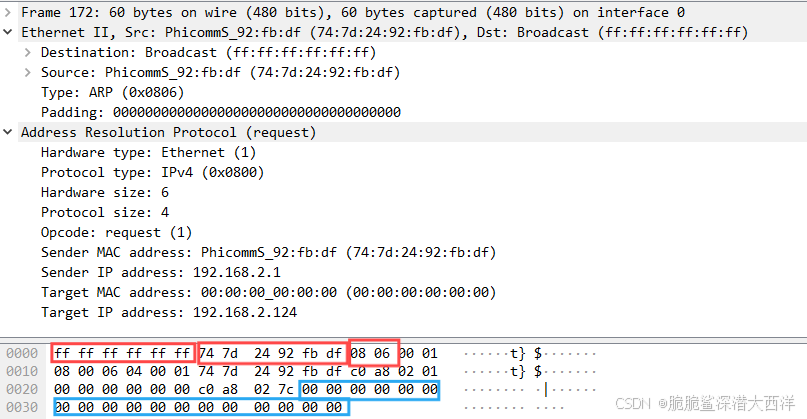

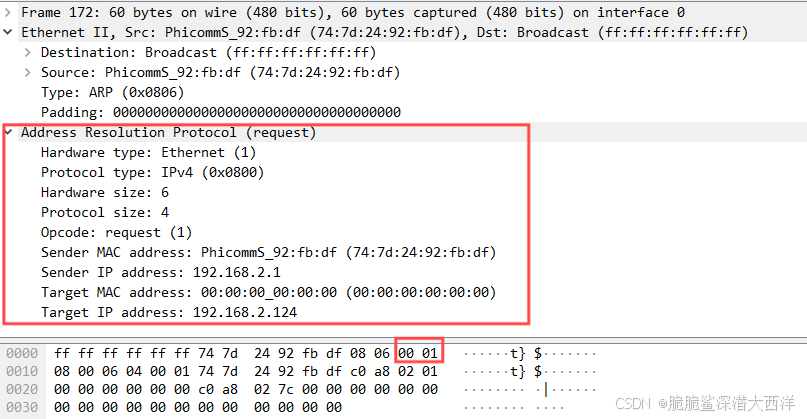

以下是一个小例子:

这是一个广播信号,源地址为:74:7d:24:92:fb:df,类型为0806(ARP协议)。ARP应答/请求在中间未标记字段,后续的全0字段为字节填充。

以太网帧传输方式

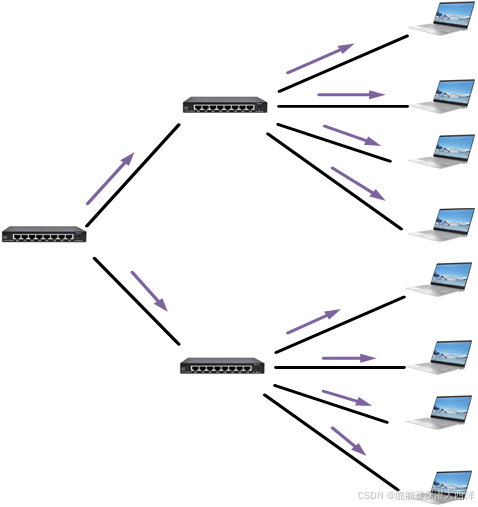

单播:指从单一的源端发送到单一的目的端。

广播:表示帧从单一的源发送到共享以太网上的所有主机。

组播:组播可以理解为选择性的广播 。

如何通过地址来进行区分:广播的地址为全1;单播地址的第一个Byte为 0x00,而组播地址的第一个Byte为 0x01。

以下从左到右依次是:单播、广播、组播。

帧间隙:(IFG,Interpacket Gap)

帧间隙的时间就是网络设备和组件在接收一帧之后,需要短暂的时间来恢复并为接收下一帧做准备的时间,IFG 的最小值是 96 bit time。96 bit time 的含义:在媒介中发送96位原始数据所需要的时间,在不同媒介中IFG的最小值是不一样的。

10Mbit/s 最小时间为: 96*100ns = 9600ns;(10M以太网下发送 1bit 数据需要100ns)

100Mbit/s 最小时间为: 96*10ns = 960ns;

1000Mbit/s 最小时间为: 96*1ns = 96ns 。

ARP协议

ARP:Address Resolution Protocol(地址解析协议)。ARP 是根据 IP 地址(逻辑地址) 获取 MAC 地址的一种 TCP/IP 协议。

ARP的映射分为静态映射和动态映射。

所谓静态映射,就是指手动将 IP 地址和 MAC 地址绑定到一起。

ARP协议的工作方式

ARP工作方式: ARP请求; ARP应答; 免费ARP 。接下来解释一下这三种工作方式有何区别:

ARP请求 的发送过程为:主机A会广播一个ARP请求数据包,该数据包包含主机A的IP地址和MAC地址,以及主机B的IP地址。以此来询问网络中哪个设备的IP地址与主机B的IP地址匹配,并请求该设备返回其MAC地址。

ARP应答 的工作过程为:主机B会向主机A发送一个ARP应答数据包,该数据包包含主机B的IP地址和MAC地址。这是一个单播消息,直接发送给主机A。主机A收到ARP应答后,将主机B的IP地址和MAC地址的映射关系存储在ARP缓存中,以便后续通信时直接使用。

免费ARP 是一种特殊的ARP请求,设备主动使用自己的IP地址作为目的IP地址发送的ARP请求。这样做的目的如下:

1、IP冲突检测:设备通过发送免费ARP报文,检测网络中是否有其他设备使用了相同的IP地址。如果有设备响应,则说明存在IP冲突。

2、刷新ARP表:当设备更改了MAC地址或获得了新的IP地址后,会发送免费ARP报文,通知同一广播域内的其他设备更新其ARP表中的映射关系。

3、VRRP主备切换:在虚拟路由冗余协议(VRRP)中,当主设备故障切换到备用设备时,备用设备会发送免费ARP报文,刷新其他设备的ARP表。

4、服务器集群:部分集群通过免费ARP报文作为心跳报文,告知其他服务器其在线状态。

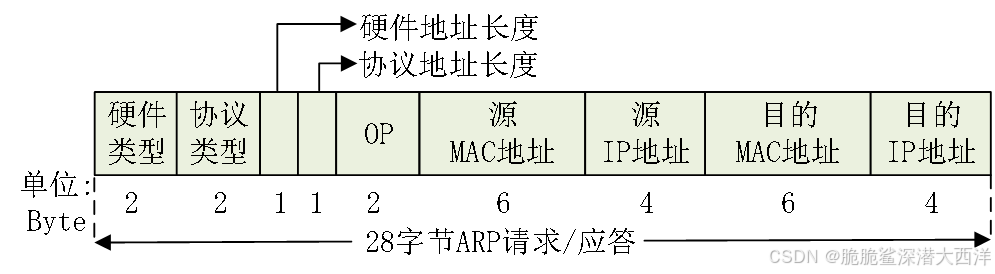

ARP协议的内容

ARP协议的内容在以太网帧中占28Byte,具体内容如下:

其中,硬件类型一般都是以太网接口(0x0001) ,协议类型一般是IPv4(0x0800),硬件地址长度为6字节,协议地址长度为4字节,OP为0x0001为ARP请求,0x0002为ARP应答。

值得一提的是,目的MAC地址在ARP请求中可以是全1或全0,因为本身就不知道目的MAC地址嘛。

ARP报文实例如下:

ARP报文段从标记的0001开始 ,上面带有各个字段的解析。

PHY通信接口简介与时序

PHY通信接口简介

PHY芯片通信接口:MII(Medium Independent Interface),即“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、GMII、RGMII等。但一块PHY通常不会集成以上全部接口,而是根据需求有选择的集成一部分。下面对它们进行一一介绍。

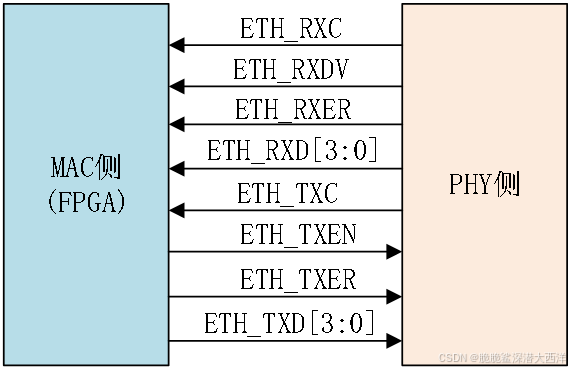

MII

| 接口 | 方向 | 作用 | 补充 |

| ETH_RXC | PHY —> FPGA | 发送由PHY芯片产生的时钟信号 | 发送时钟 |

| ETH_RXDV | PHY —> FPGA | 数据有效信号, 高电平时数据有效 | |

| ETH_RXER | PHY —> FPGA | 数据错误信号,高电平时数据有误 | 接收端接收此数据后可以选择丢弃 |

| ETH_RXD[3:0] | PHY —> FPGA | 发送数据的接口(对于PHY) | |

| ETH_TXC | PHY —> FPGA | 发送由PHY芯片产生的时钟信号 | 接收时钟 |

| ETH_TXEN | FPGA —> PHY | 数据有效信号,高电平时数据有效 | |

| ETH_TXER | FPGA —> PHY | 数据错误信号,高电平时数据有误 | |

| ETH_TXD[3:0] | FPGA —> PHY | 发送数据的接口(对于FPGA) | |

| CRS | PHY —> FPGA | 载波侦测信号 | |

| COL | PHY —> FPGA | 冲突检测信号 |

MII 接口只支持10M和100M,当处于10M的情况下,因为数据位宽是4位,所以此时的时钟频率为 2.5MHz;当处于100M的情况下,时钟频率为 25MHz。此外,还有MDIO接口:用于配置PHY芯片的寄存器。

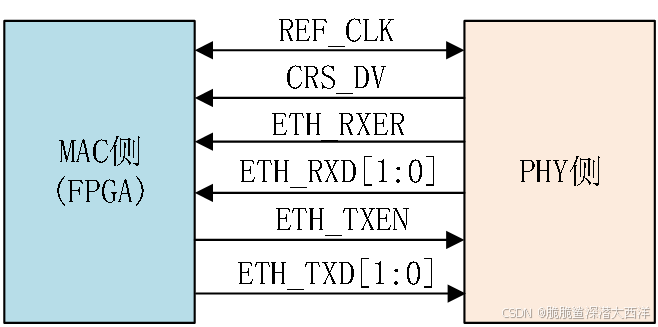

RMII

RMII: Reduced Media Independent Interface,即简化媒体独立接口。同样也只支持 10M 和100M。

| 接口 | 方向 | 作用 | 补充 |

| REF_CLK | 双向 | 时钟信号 | 由外部晶振产生 |

| CRS_DV | PHY —> FPGA | 由 MII 的 ETH_RCDV 和 CRS 合并到了一起,高电平时表示数据有效 | |

| ETH_RXER | PHY —> FPGA | 数据错误信号,高电平时数据有误 | 接收端接收此数据后可以选择丢弃 |

| ETH_RXD[1:0] | PHY —> FPGA | 发送数据的接口(对于PHY) | |

| ETH_TXEN | FPGA —> PHY | 数据有效信号,高电平时数据有效 | |

| ETH_TXD[1:0] | FPGA —> PHY | 发送数据的接口(对于FPGA) |

RMII 接口也只支持10M和100M,当处于10M的情况下,因为数据位宽是2位,所以此时的时钟频率为 5MHz;当处于100M的情况下,时钟频率为 50MHz。

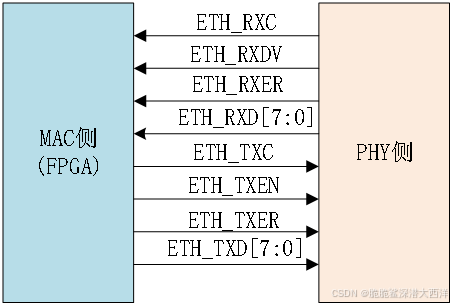

GMII

GMII: Gigabit Media Independent Interface,即千兆比特媒体独立接口。

| 接口 | 方向 | 作用 | 补充 |

| ETH_RXC | PHY —> FPGA | 发送由PHY芯片产生的时钟信号 | 发送时钟 |

| ETH_RXDV | PHY —> FPGA | 数据有效信号, 高电平时数据有效 | |

| ETH_RXER | PHY —> FPGA | 数据错误信号,高电平时数据有误 | 接收端接收此数据后可以选择丢弃 |

| ETH_RXD[7:0] | PHY —> FPGA | 发送数据的接口(对于PHY) | |

| ETH_TXC | FPGA —> PHY | 发送由PHY芯片产生的时钟信号 | 接收时钟 |

| ETH_TXEN | FPGA —> PHY | 数据有效信号,高电平时数据有效 | |

| ETH_TXER | FPGA —> PHY | 数据错误信号,高电平时数据有误 | |

| ETH_TXD[7:0] | FPGA —> PHY | 发送数据的接口(对于FPGA) | |

| CRS | PHY —> FPGA | 载波侦测信号 | |

| COL | PHY —> FPGA | 冲突检测信号 |

GMII支持千兆网,同时也向下兼容10M和100M网。GMII的接口基本与GII相同,但数据位宽为8位,且ETH_TXC信号转为由MAC侧发送(MII中ETH_RXC和ETH_TXC均由PHY侧发送)。

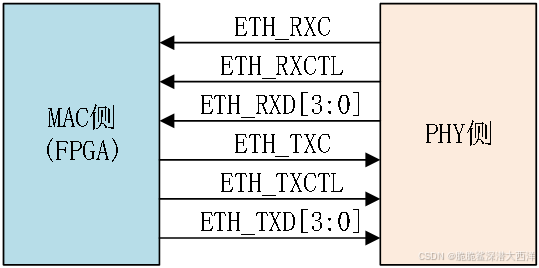

RGMII

RGMII: Reduced Gigabit Media Independent Interface,即简化千兆比特媒体独立接口。

| 接口 | 方向 | 作用 | 补充 |

| ETH_RXC | PHY —> FPGA | 发送由PHY芯片产生的时钟信号 | 发送时钟 |

| ETH_RXCTL | PHY —> FPGA | 上升沿和下降沿同为高电平有效 | 由RXDV和RXER合并 |

| ETH_RXD[3:0] | PHY —> FPGA | 发送数据的接口(对于PHY) | |

| ETH_TXC | FPGA —> PHY | 发送由PHY芯片产生的时钟信号 | 接收时钟 |

| ETH_TXCTL | FPGA —> PHY | 上升沿和下降沿同为高电平有效 | 由TXEN和TXER合并 |

| ETH_TXD[3:0] | FPGA —> PHY | 发送数据的接口(对于FPGA) |

ETH_RXCTL:

在时钟上升沿,ETH_RXCTL 表示接收数据有效信号(ETH_RXDV),高电平表示当前接收的数据是有效的。

在时钟下降沿,ETH_RXCTL 表示接收数据错误信号(ETH_RXER)与接收数据有效信号(ETH_RXDV)的异或值(ETH_RXER xor ETH_RXDV)。如果 ETH_RXER 为高电平,表示接收到的数据存在错误。

ETH_TXCTL:

在时钟上升沿,ETH_TXCTL 表示发送数据使能信号(ETH_TXEN),高电平表示当前发送的数据是有效的。

在时钟下降沿,ETH_TXCTL 表示发送数据错误信号(ETH_TXER)与发送数据使能信号(ETH_TXEN)的异或值(ETH_TXER xor ETH_TXEN)。如果 ETH_TXER 为高电平,表示发送的数据存在错误。

RGMII是如何达到千兆网的?只需125M时钟,通过双沿采样和4为数据位宽即可达到,125×2×4=1000。此时数据在上升沿和下降沿都会被采样。

PHY接口时序

以下的时序都是针对PHY芯片而言的,发送时序为PHY芯片发送数据的时序,接收时序为PHY芯片接收数据的时序。

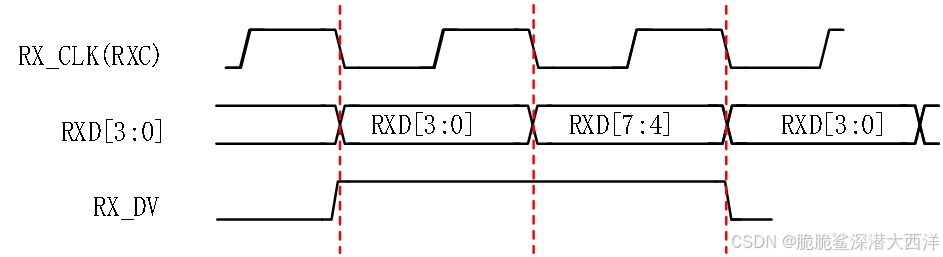

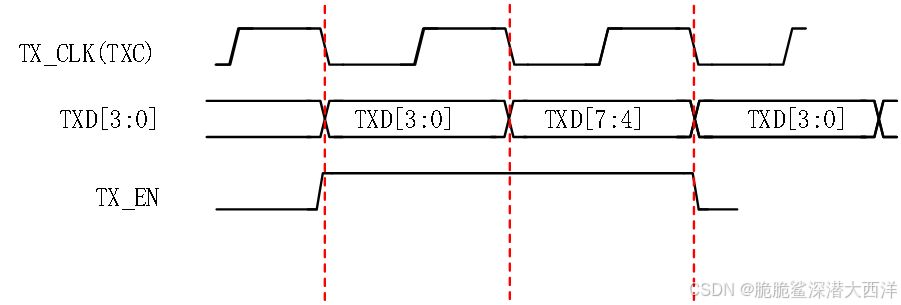

MII接口时序

发送时序

PHY芯片会在上升沿时采样,下降沿时输出,如下图所示。

PHY 芯片会在在 RX_CLK 下降沿输出数据 RXD,两个时钟发送一字节数据,先发送低四位数据,后发送高四位数据,发送数据时RXDV信号也会拉高。 MAC侧的FPGA会在时钟上升沿采集 RXDV 和 RXD 的状态。

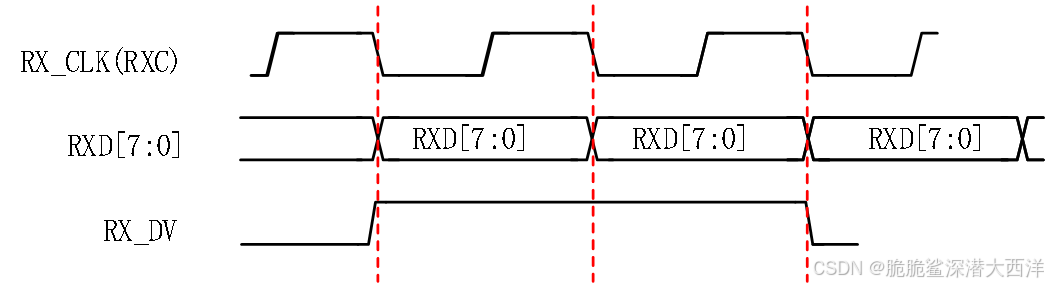

接收时序

与发送时序基本相同。

RMII接口时序

与 MII 接口时序一致。

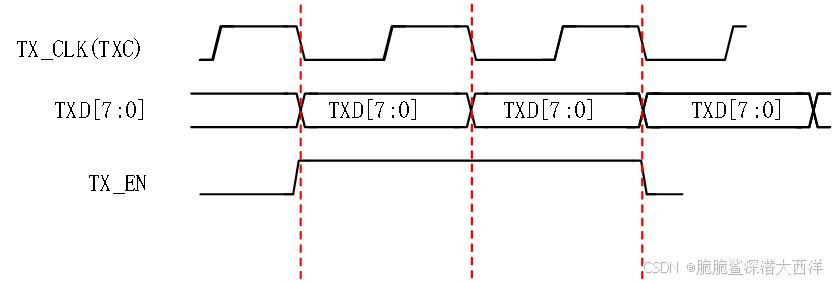

GMII接口时序

发送时序

与 MII 接口时序相同,PHY 芯片同样是在 RX_CLK 下降沿输出数据,MAC 侧的 FPGA 在上升沿采集数据。区别是 GMII 在每个时钟周期都会传输 1Byte 数据。

接收时序

与接收时序基本相同。

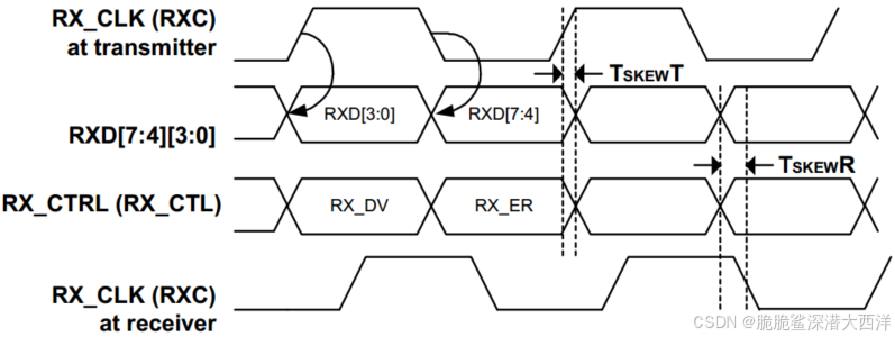

RGMII

发送时序

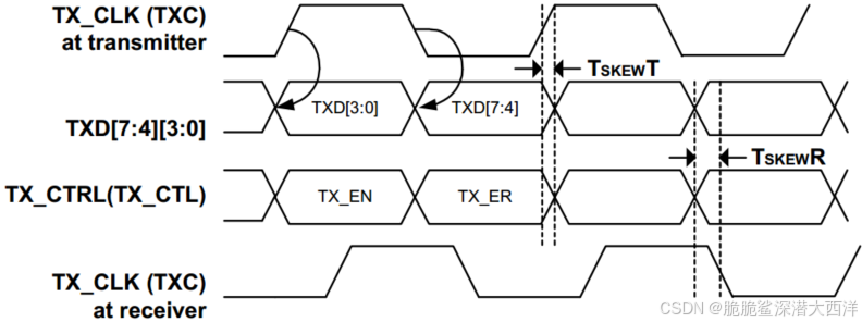

与上面不同的是,RGMII接口会在上升沿和下降沿都进行数据发送:在时钟的上升沿发送低4位数据,在时钟的下降沿发送高4位数据。每个时钟周期能发送 1Byte 数据。

注意,RX_CLK要延迟2ns后再输出给接收端,因为接收端会在时钟的上升沿采集数据,但发送端也是在上升沿发送数据,延迟2ns能保证接收端能够采集到数据。延迟2ns的方法可以使用PLL(可以参考这篇文章:PLL学习笔记-优快云博客)。

另一个需要注意的是图中标记出来的 TskewR 和 TskewT,分别是接收端和发送端的时钟偏斜,即 RX 和 RX_CTRL 信号对于 RX_CLK 的延迟。这个延迟是需要严格控制的,一般是±500ps。

接收时序

与发送时序基本相同。

1167

1167

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?