笔记根据正点原子官方教学视频第33讲

时间:2025/2/21

【第一期】手把手教你学领航者&启明星ZYNQ之FPGA开发篇【真人出镜】FPGA教学视频教程_哔哩哔哩_bilibili

有错误的地方希望可以告诉博主

前言

XILINX器件原语

原语,是FPGA厂商针对其器件特征开发的一系列常用模块的名称。原语是FPGA芯片中基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等。原语在设计中可以直接例化使用,是最直接的代码输入方式,原语和HDL原语的关系,类似于汇编语言和C语言的关系。

XILINX原语的分类

Xilinx公司的原语按功能分为10类,包括计算组件、I/O端口组件、寄存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及吉比特收发器组件。常用的原语包括时钟缓冲、差分和单端信号相互转换以及I/O处理(IDDR、ODDR)原语等。

IO 端口组件

时钟组件

时钟组件包括各种全局时钟缓冲器、全局时钟复用器、普通I/O本地的时钟缓冲器以及高级时钟管理模块。与其相关的原语包括: BUFG、 BUFR、BUFH、 BUFIO、 BUFGCE、 BUFGDLL和DCM等。

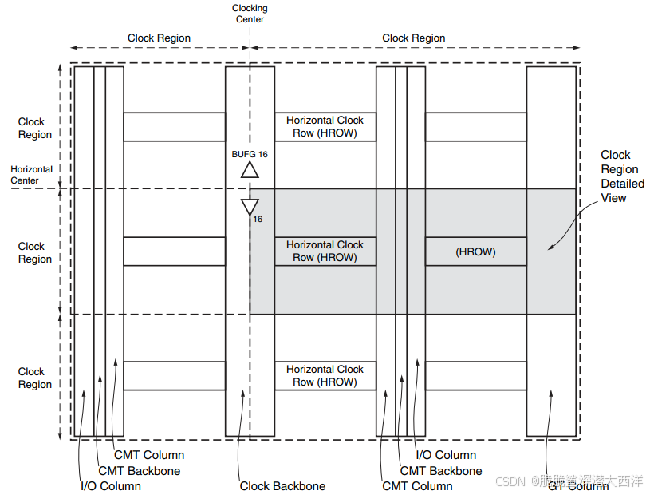

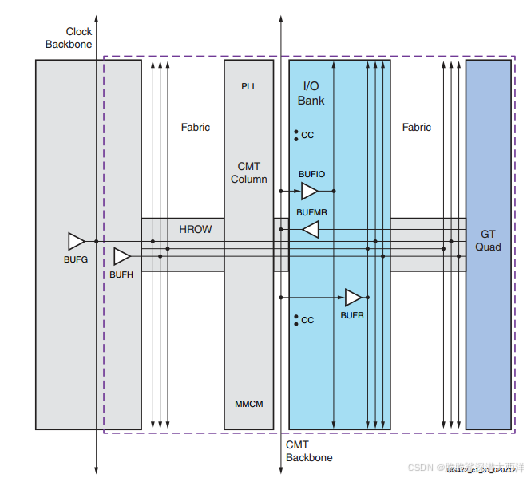

7系列FPGA高级时钟结构视图:

Clocking Center:时钟中心。

Horizontal Center水平中心线将BUFG分为上下两个部分,每个部分16个BUFG,上下部分的BUFG是不能混用的。

Clock Region:时钟域。从图中可看出7系列FPGA拥有6个时钟域,分为三行两列。一个时钟域包含50个IO,50个CLB,这些资源被HROW隔开,上下平均分布——即上部25个IO,25个CLB;下部同理。

I/O Column:I/O列,包括I/OB,IDDR,ODDR等。

CMT Backbone:区域时钟网络。

CMT Column:是MMCM、DCM、PL等这些时钟管理单元所在的区域。

GT Column:高速串行收发器所在的列。

HROW:行时钟,BUFH就在其中走线。

一些常用组件原语

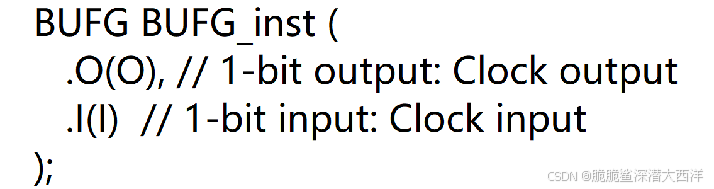

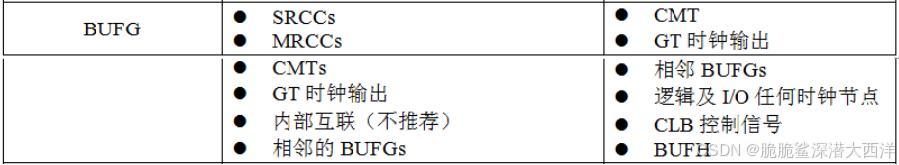

BUFG

BUFG:全局缓冲器, BUFG 的输出到达 FPGA 内部的 IOB、 CLB、块 RAM 的时钟延迟和抖动最小 。 BUFG原语模板:

BUFG的输入和输出:

这里解释一下 SRCCs 和 MRCCs 的区别:SRCCs和MRCCs都是专用的时钟输入管脚,但SRCC只能被本区域内的时钟所用,要被别的区域的BUFR/BUFIO使用要先经过BUFG;MRCC可以被相邻的两个区域的BUFR/BUFIO使用。这会导致使用 SRCCs 和 MRCCs 来供相邻区域使用时, MRCCs 的时延会更低。

内部互联是指从逻辑时钟连接到BUFG。

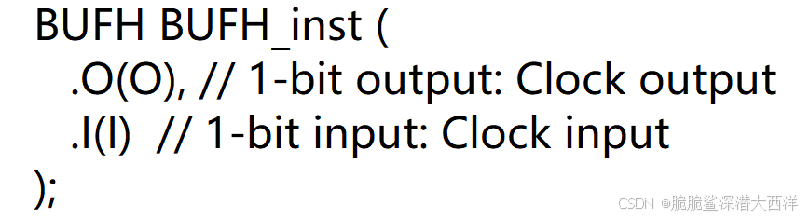

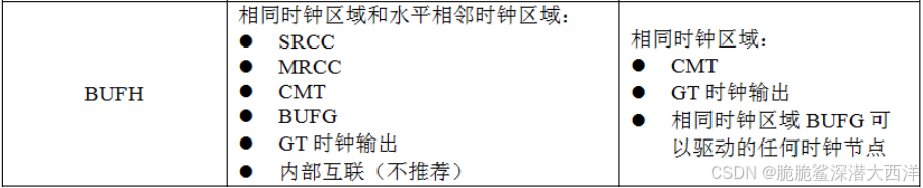

BUFH

BUFH:水平时钟缓冲器,它相当于一个功能受限的BUFG,其输出时钟只能通过HROW在左右相邻的时钟区域内工作。每个区域内有12个BUFH可用。 BUFH原语模板:

BUFH 的输入(左)和输出(右):

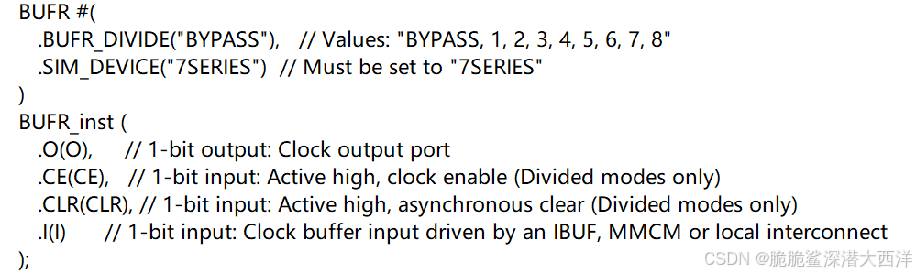

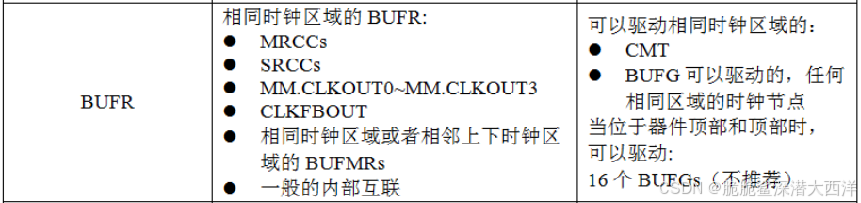

BUFR

BUFR:区域时钟缓冲器,其输出只能作用在一个时钟区域,相当于BUFH的阉割版。 BUFR原语模板:

BYPASS:指输入时钟和输出时钟直接对接,1-8是指分频,对输入时钟分频后再接给输出时钟。

BUFR的输入和输出:

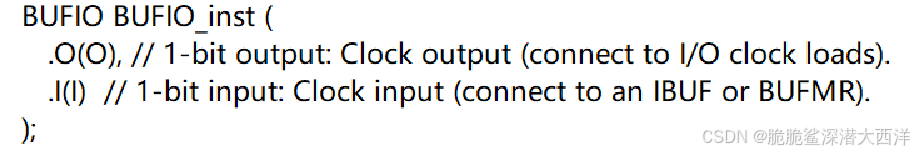

BUFIO

BUFIO: IO时钟缓冲器,其输出时钟只能作用在一个时钟区域的IO寄存器处,无法在FPGA内部逻辑使用。

BUFIO的作用为:稳定 I/O 时钟信号,减少抖动和噪声,确保时钟信号的完整性。

BUFIO原语模板:

BUFIO的输入和输出:

时钟区域视图:

一个时钟区域内有4个BUFIO、4个BUFR、2个BUFMR。

IODDR

缓冲器使用场景:

| BUFG | BUFH | BUFMR | BUFR | BUFIO | |

| 使用场景 | 一般用在跨多个时钟区域的时钟上 | 一般用在相同时钟区域或者相邻时钟区域的时钟 | 当输入时钟需要连接多个区域的BUFR或者BUFIO时使用 | 可用于不需要跨区域的时钟,但一般用作IO资源的接口时钟 | 只能用于IO资源的接口时钟 |

既然BUFG可以跨多个时钟区域使用,为什么还需要BUFH呢?因为有些功能执行的次数很少,比如某些串口可能只在上电时发送一次数据,这个时候使用BUFH可以节省功耗,在不使用后通过BUFHCE来控制BUFH的休眠。

IO端口组件:

I/O组件提供了标准单端I/O缓存(IBUF/OBUF)、DDR专用I/O信号缓存(IDDR/ODDR)、可变抽头延迟链(IDELAY/ODELAY)、上拉(PULLUP)、下拉(PULLDOWN)以及单端信号和差分信号之间的相互转换(IBUFDS/ OBUFDS) 等。

Bank

在 FPGA 中, Bank 是指一组物理位置和特性相近的 I/O(输入/输出)引脚的总称。Bank 的特性如下:

- 每个 Bank 独立供电,其接口标准由接口电压 VCCIO 决定。一个 Bank 只能有一种 VCCIO,但不同 Bank 的 VCCIO 可以不同。

- 同一 Bank 内的 I/O 引脚具有相同的电气特性,只有相同电气标准的端口才能连接在一起。

- 通过将 I/O 引脚划分为不同的 Bank,FPGA 可以适应多种电气标准,增强 I/O 设计的灵活性。

Bank 还分为 HP Bank(High Performance)、HR Bank(High Range)和 HD Bank(High Density),并不是每一块FPGA都同时拥有所有的 Bank。

| Bank | 说明 |

| HP Bank | 高性能Bank,应用于高性能场景,如 DDR 或其他高速差分总线,Bank 电压最高为 1.8V。 |

| HR Bank | 高范围Bank,支持更宽范围的 I/O 标准,最高电压可达 3.3V |

| HD Bank | 高密度Bank,应用于低速 I/O 场景,最高速率限制在 250M 以内,最高电压支持到 3.3V。 |

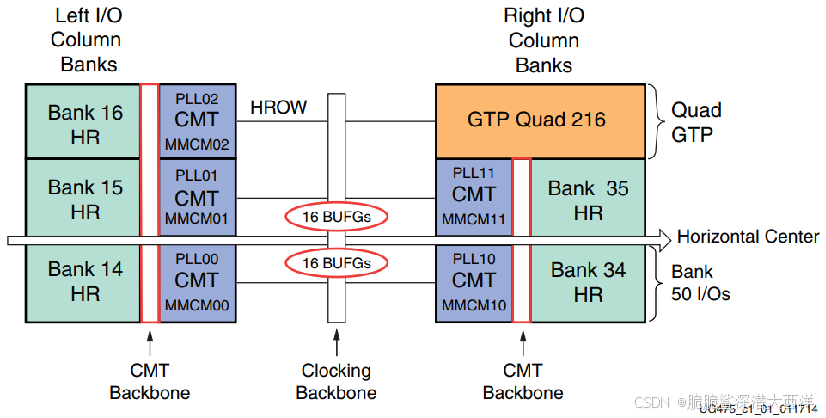

XC7A35T BANK分布

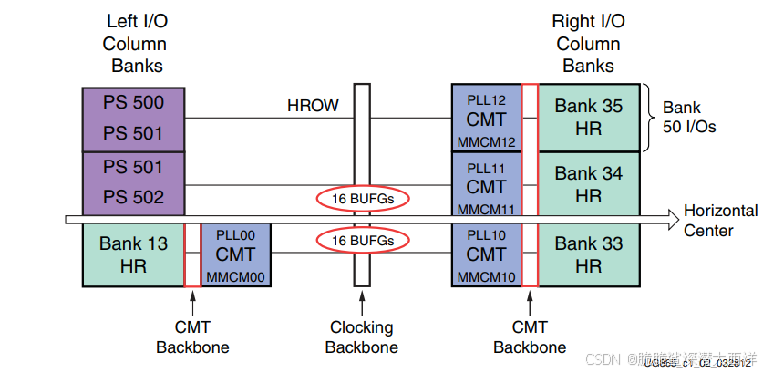

XC7Z020 BANK分布

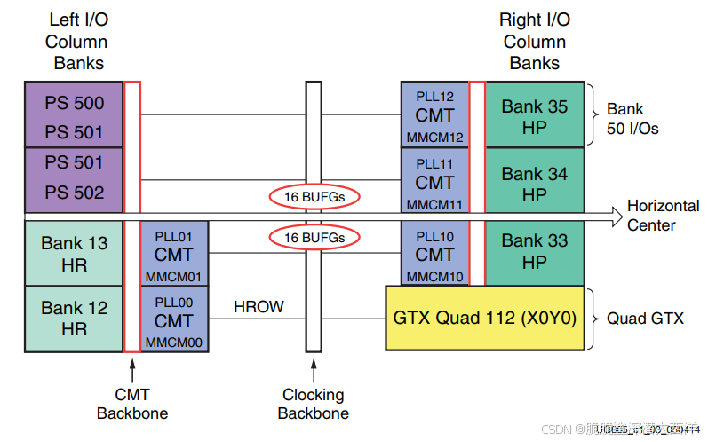

XC7Z030 BANK分布

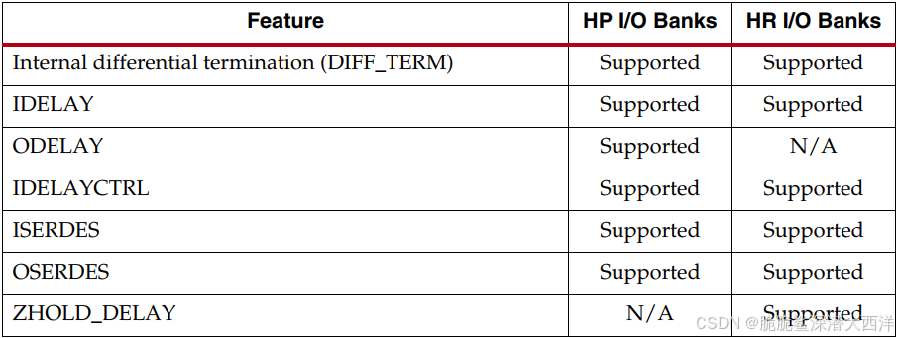

HP BANK与HR BANK IO资源的区别:

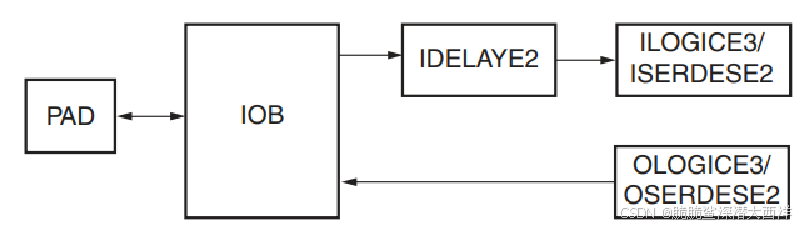

HR的IO资源结构

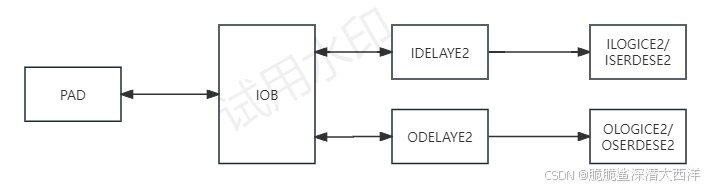

HP的IO资源结构是在以上的基础上,在IOB和OLOGICE/OSERDESE2之间增加了ODELAYE2,且ILOGICE3和OLOGICE3变为了ILOGICE2和OLOGICE2,如下:

输入信号:

1、从 PAD 进入 IOB。

2、在 IOB 中进行初步处理。

3、进入 ILOGICE3 进行逻辑操作。

4、进入 FPGA 的内部逻辑进行进一步处理。

输出信号:

1、从 FPGA 内部逻辑进入 OLOGICE3。

2、在 OLOGICE3 中进行逻辑操作。

3、通过 IOB 进行进一步处理。

4、从 PAD 输出到外部电路。

IDDR

IDDR :输入数据的双沿采样,是ILOGIC块中专用的寄存器,用于实现输入数据双沿采样。

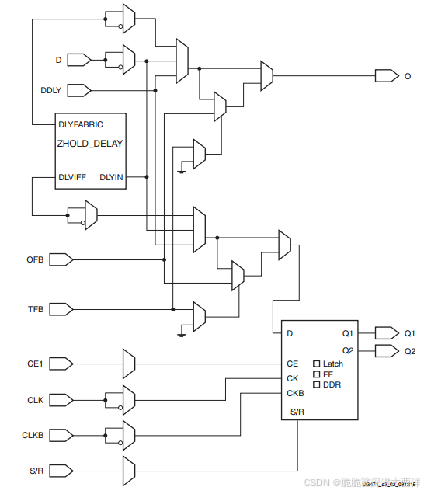

ILOGICE3 结构

CE是使能信号,为高时才代表有效。

IDDR工作模式

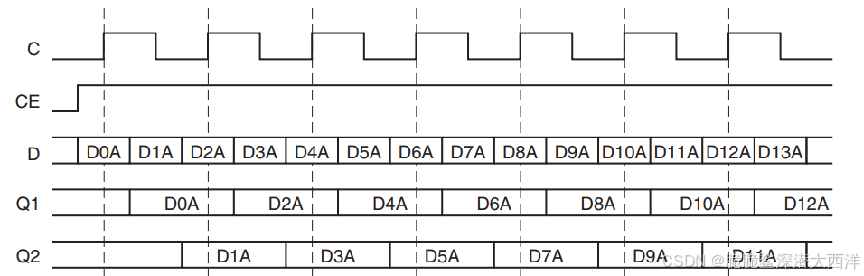

1、相反沿模式:OPPOSITE_EDGE mode ,时序如下:

这种情况下,要在下降沿采集D0A,上升沿采集D1A,往后类推,这样数据才比较有序。这种模式在实际项目中不太使用,比较麻烦。

这种情况下,要在下降沿采集D0A,上升沿采集D1A,往后类推,这样数据才比较有序。这种模式在实际项目中不太使用,比较麻烦。

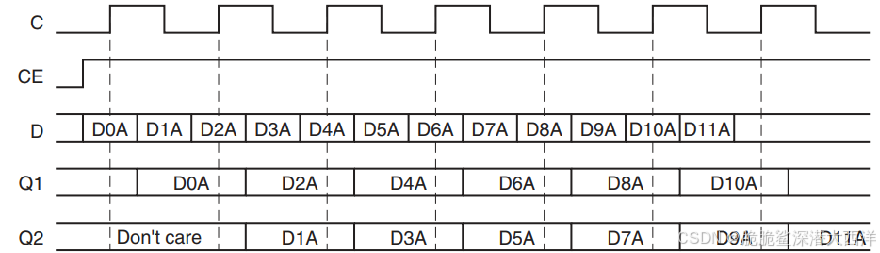

2、相同沿模式:SAME_EDGE mode ,时序如下:

这种模式在实际项目中也不太使用。

这种模式在实际项目中也不太使用。

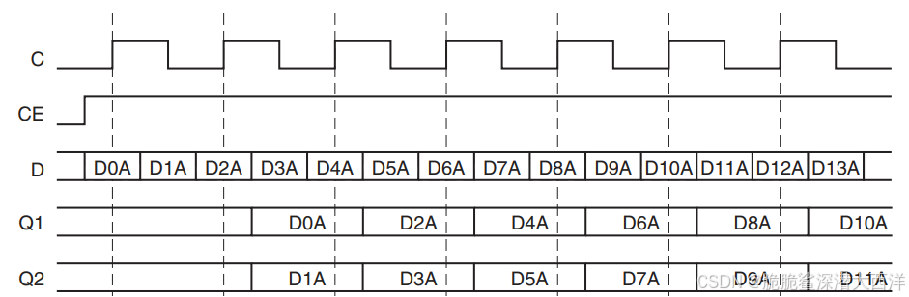

3、相同沿的流水模式:SAME_EDGE_PIPELINED mode,时序如下:

这种模式最常用。

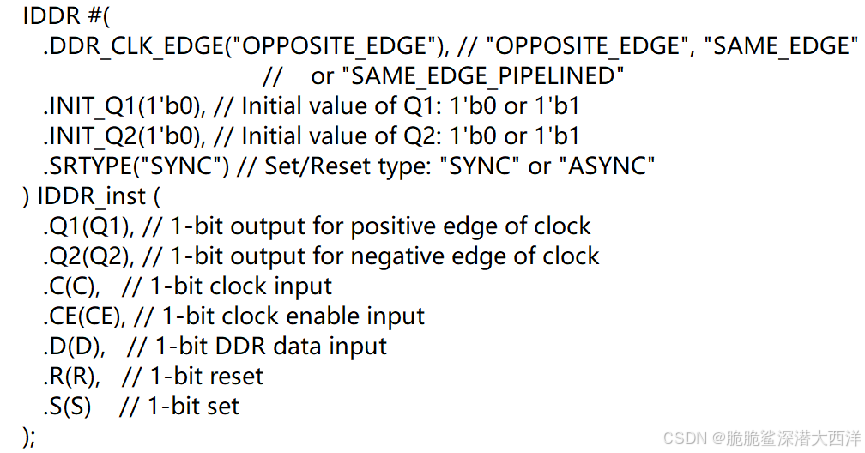

IDDR 原语

DDR_CLK_EDGE:时钟边沿配置,可选择上述三种模式。

INIT_Q1:设置 Q1 的初始值。

INIT_Q2:设置 Q2 的初始值,Q1 和 Q2 用于接收 IDDR 转换后的单沿数据。

SRTYPE:复位/置位类型。可选同步和异步。

C 为时钟引脚。

CE 为控制使能引脚,高电平时才将新数据加载至 DDR 触发器。

D 为输入引脚。

R是复位,S是置位,两者同时只能一个为高。

ODDR

ODDR :输出数据的双沿采样,是OLOGIC块中专用的寄存器,用于实现输出数据双沿采样。

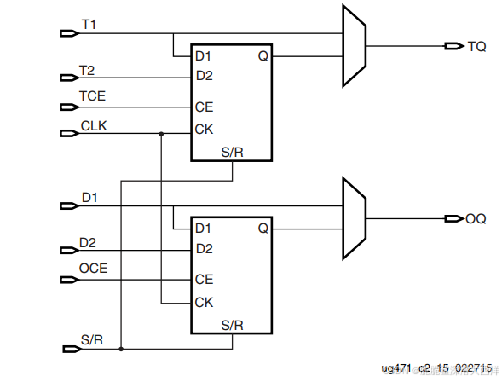

OLOGICE3 结构

不管是 OLOGICE3 还是 OLOGICE2 内部结构是一样的。

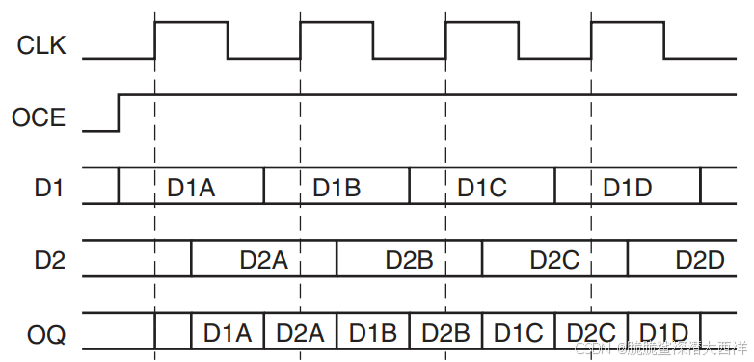

ODDR工作模式

1、相反沿模式 :OPPOSITE_EDGE mode,不怎么使用。一般来说上升沿采样 D1,然后将 D1 放到 OQ 上;下降沿采样 D2,然后将 D2 放到 OQ 上。

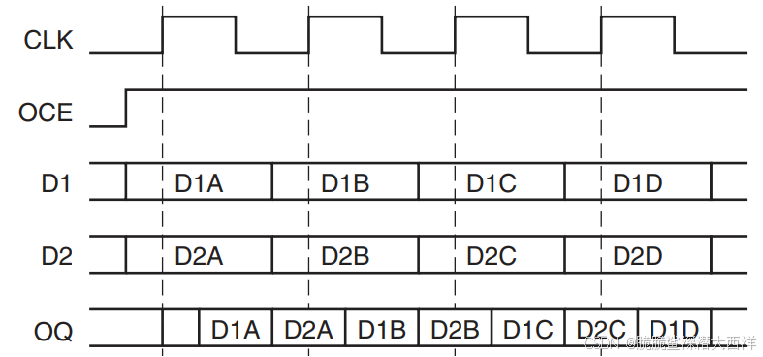

2、相同沿模式:SAME_EDGE mode。在时钟CLK上升沿同时采集D1、D2的数据,然后进行输出,这个输出并非对齐时钟信号的边沿,而是有把控在严格范围内的时钟偏斜。

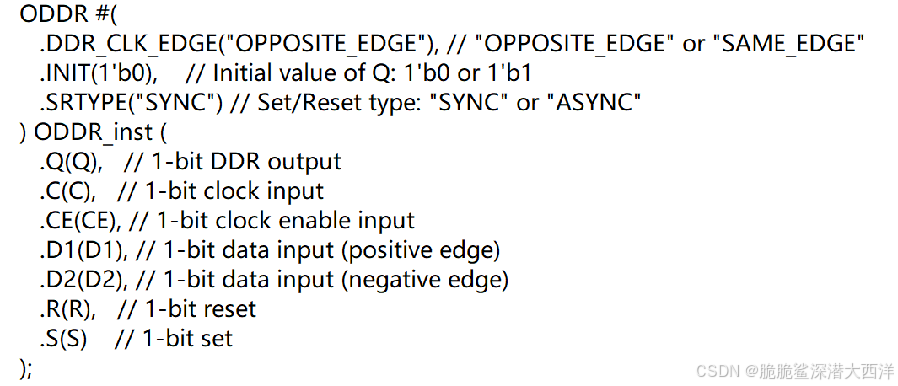

ODDR 原语

DDR_CLK_EDGE:时钟边沿配置,可选择上述两种模式。

INIT:初始化 OQ (以下端口标记为 Q)的值。

SRTYPE:复位/置位类型。可选同步和异步。

D1 和 D2 都是输入引脚。

Q 是输出引脚。

IDELAY 原语

IDELAY :每个I/O模块都包含了一个可编程的延迟原语,称作IDELAYE2 。 IDELAY2是一个可编程的31阶延迟原语,它既可以应用于组合逻辑也可以应用于时序逻辑或者同时用于两者。

IDELAY参数

IDELAY的参数如下表所示。另外附上一些详细说明。

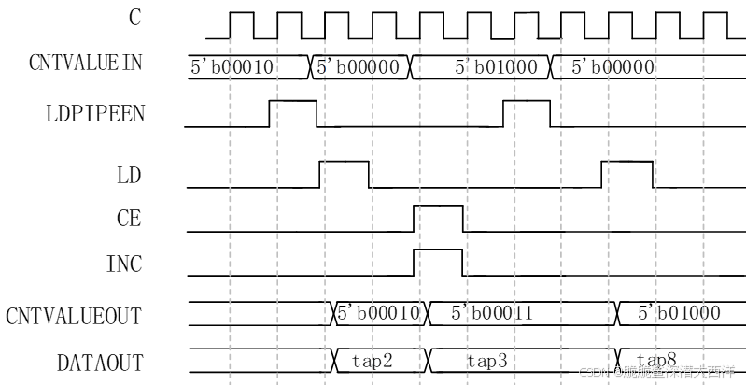

IDELAY_TYPE 中的 VARIABLE 和 VAR_LOAD 的区别是 VARIABLE 的延迟初始值由IDELAY_VALUE设置,它的可变是通过CE(Clock Enable)和INC(Increment)端口,在时钟信号的上升沿动态地递增或递减延迟值来实现的。而 VAR_LOAD 相比于 VARIABLE 多一个功能 :可以通过 CNTVALUEIN 端口加载新的延迟值。当 LD(Load)端口有效时,可以将 CNTVALUEIN 的值加载到控制模块,从而更新延迟值。VAR_LOAD_PIPE 则会将 CNTVALUEIN 端口的值先加载到流水线寄存器,以备更新。

DELAY_SRC 用于指定延迟的输入信号来源。它决定 IDELAY 原语是从哪个输入端口接收信号并进行延迟处理。IDATAIN 表示延迟的输入信号来自I/O引脚,即从外部输入到FPGA的信号。DATAIN 表示延迟的输入信号来自FPGA内部逻辑。

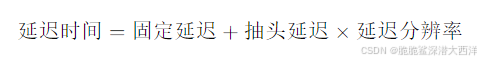

IDELAY_VALUE 表示延迟的抽头数,取值范围为 0 到 31。每个抽头数对应一个特定的延迟时间,延迟时间的大小取决于 IDelay 原语的配置和工作模式。延迟时间可以通过以下公式计算:

延迟分辨率是指每个抽头对应的延迟时间。它取决于 IDelay 原语的参考时钟频率(REFCLK_FREQUENCY)。延迟分辨率可以通过以下公式计算(f 是参考时钟频率,单位为 MHz。):

不同参考时钟频率下的延迟分辨率:

200MHz :延迟分辨率为 78ps。

300MHz :延迟分辨率为 52ps。

400MHz :延迟分辨率为 39ps。

HIGH_PERFORMANCE_MODE 是IDELAY原语中的一个参数,用于控制 IDELAY 原语的性能模式。它有两个可选值:TRUE 和 FALSE:当设置为TRUE时,IDELAY原语会减少输出抖动,从而提高信号的稳定性。这种模式下,IDELAY原语的功耗会略有增加;当设置为FALSE时,IDELAY原语会减少功耗,但可能会增加输出抖动。

SIGNAL_PATTERN 用于指定输入信号的类型。选择输入信号类型时 IDELAY 对其进行专门优化,保证不同数据的稳定性。

REFCLK_FREQUENCY 是参考时钟的输入。

| Attribute | Value | Description |

| IDELAY_TYPE | String:FIXED,VARIABL,VAR_LOAD,or VAR_LOAD_PIPE | 设置延迟值的类型: FIXED:固定模式,设置静态延迟值; VARIABLE:可变延迟模式,动态调整延迟值; VAR_LOAD:可加载可变延迟模式, 动态加载和调整延迟值; VAR_LOAD_PIPE:可加载可变延迟流水模式, 存储CNTVALUEIN的值以备将来更新。 |

| DELAY_SRC | String: IDATAIN, DATAIN | IDATAIN:IDELAY的输入为IDATAIN; DATAIN:IDELAY的输入为DATAIN; |

| IDELAY_VALUE | Integer: 0 to 31 | FIXED模式下的延迟值或者VARIABLE模式下 的初始延迟值。当模式为VAR_LOAD或者 VAR_LOAD_PIPE时,这个参数被忽略。 |

| HIGH_PERFORMANCE _MODE | Boolean:FALSE or TRUE | 当这个参数为TRUE时,器件会减少输出的抖动。 |

| SIGNAL_PATTERN | String:DATA,CLOCK | 使时序分析仪考虑数据或时钟路径中适当 数量的延迟链抖动。 |

| REFCLK_FREQUENCY | Real:190 to 210 ,290 to 310, or 390 to 410 | 设置时序分析仪用于静态时序分析的延迟值 (以MHz为单位)。 |

| CINVCTRL_SEL | Boolean:FALSE or TRUE | 启用CINVCTRL_SEL引脚以动态切换C引脚的极性。 |

| PIPE_SEL | Boolean: FALSE or TRUE | 选择PIPE_SEL模式。这个参数只在使用 VAR_LOAD_PIPE模式时设置为TRUE。 |

IDELAY_TYPE 的四种模式时序

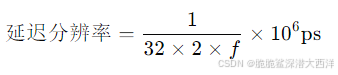

FIXED 模式

在固定延迟模式中,延迟值在配置时预设为属性 IDELAY_VALUE 确定的延迟值。 配置后,此值无法更改。注意当 IDELAY_VALUE 为0时,IDELAY 仍然会有600ps延迟,原因请看上述过的公式。FIXED模式时序:

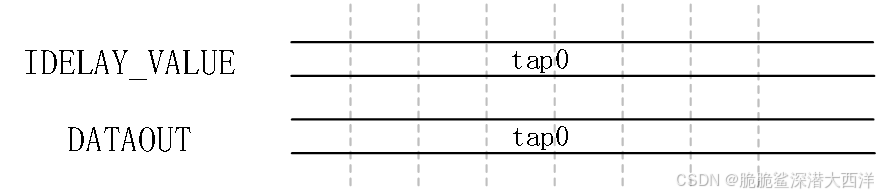

VARIABLE 模式

在该模式下,延迟值可以在配置后通过CE和INC端口进行动态配置。注意,当当前延迟值为31时,再次加1就会变为0。因为 IDELAY_VALUE 是5位数的二进制数。

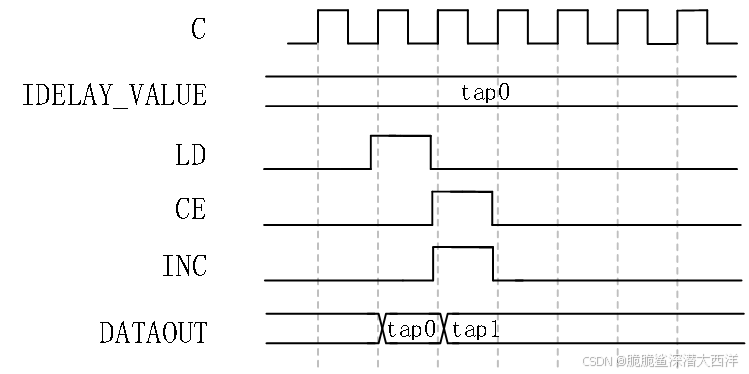

VARIABLE 模式时序

VAR_LOAD 模式

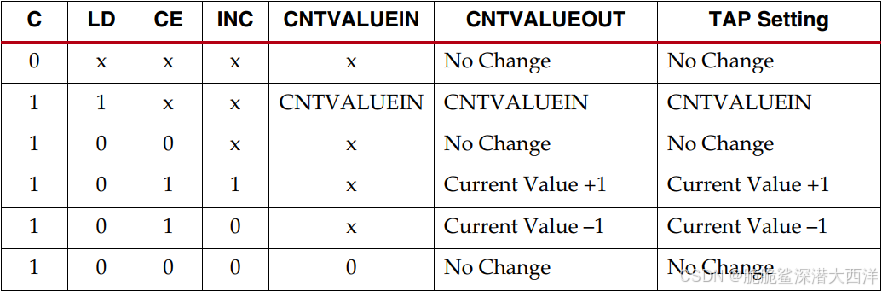

该模式下功能与 VARIABLE 模式下类似,只不过可以通过 CNTVALUEIN 加载延迟节拍数,多了一种延迟加载方法。当LD端口有效时可以加载新的延迟 CNTVALUE 值到控制模块。

VAR_LOAD 模式时序:

VAR_LOAD_PIPE 模式

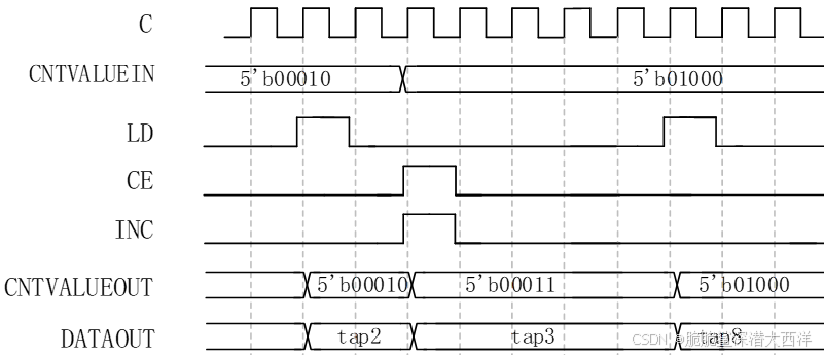

VAR_LOAD_PIPE 类似于 VAR_LOAD 模式,能够存储 CNTVALUEIN 值以备将来更新。VAR_LOAD_PIPE 和 VAR_LOAD 相比只是多了一个步骤:当 C 和 LDPIPEEN 为高时,将 CNTVALUEIN 的加载到流水线寄存器,当 C 和 LD 为高时加载流水线寄存器中的值来更新延迟。

VAR_LOAD_PIPE 模式时序 :

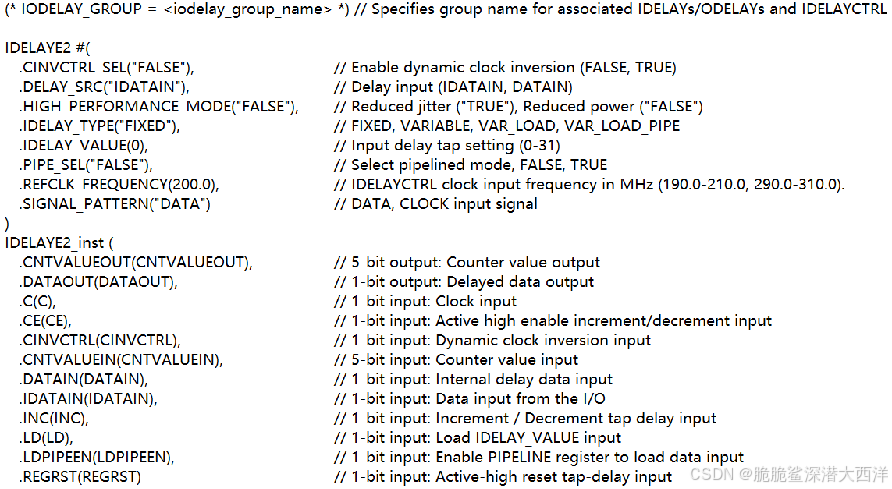

IDELAY原语模板

IODELAY_GROUP 用于将 IDELAY 原语和 IDELAYCTRL 原语分组。这个属性的作用是确保在同一个 IODELAY_GROUP 中的 IDELAY 原语和 IDELAYCTRL 原语共享相同的参考时钟和复位信号,并且在布局布线时将它们放置在物理上相邻的位置,以确保信号的完整性和性能。

其余部分均为上述的参数赋值和下一部分列出的端口,不做过多赘述。

IDELAY端口

| Port Name | Direction | Width | Function |

| C | Input | 1 | 在 VARIABLE、VAR_LOAD 或 VAR_LOAD_PIPE 模式 下使用的时钟输入 |

| REGRST | Input | 1 | 复位流水线寄存器。 仅用于 VAR_LOAD_PIPE 模式 |

| LD | Input | 1 | 将 IDELAYE2 原语加载到 VARIABLE 模式下的预编程值。 在 VAR_LOAD 模式下,它加载 CNTVALUEIN 的值。 在 VAR_LOAD_PIPE 模式下,它加载当前在流水线寄存器 中的值。 |

| CE | Input | 1 | 启用递增/递减功能。 |

| INC | Input | 1 | 增加/减少延迟值。 |

| CINVCTRL | Input | 1 | 动态反转时钟 C极性。为高时反转时钟。 |

| CNTVALUEIN | Input | 5 | 来自 FPGA 逻辑的计数器值,用于动态加载延迟值。 |

| IDATAIN | Input | 1 | 来自 IBUF 的 IDELAY 数据输入 |

| DATAIN | Input | 1 | 来自 FPGA 逻辑的 IDELAY 数据输入 |

| LDPIPEEN | Input | 1 | 使流水线寄存器能够加载CNTVALUEIN中的数据 |

| DATAOUT | Output | 1 | 来自两个数据输入端口(IDATAIN 或 DATAIN)之一 的延迟数据 |

| CNTVALUEOUT | Output | 5 | 计数器值进入 FPGA 逻辑以监控延迟值 |

这里解释一下 CNTVALUEOUT ,它用于输出当前IDELAY原语的实际延迟级数(taps)。以此来检查 IDELAY 是否正常进行了我们预期的延迟,它的输出值为0-31,对应 IDELAY_VALUE 的取值0-31。

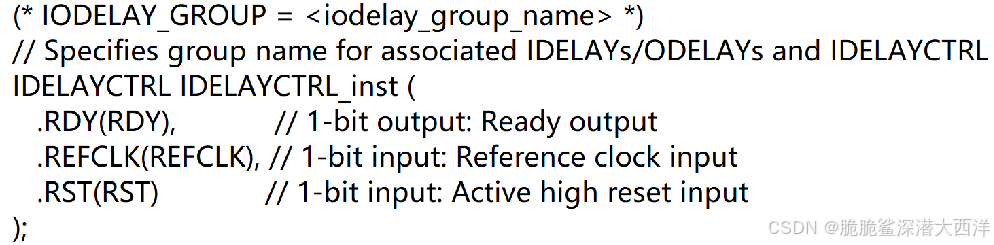

IDELAYCTRL 原语

IDELAYCTRL : IDELAYCTRL 模块连续校准其区域内的各个 IDELAY/ODELAY,以减少工艺、电压和温度变化的影响。 IDELAYCTRL 模块使用用户提供的 REFCLK(参考时钟)校准 IDELAY 和 ODELAY 。

IDELAYCTRL原语模板:

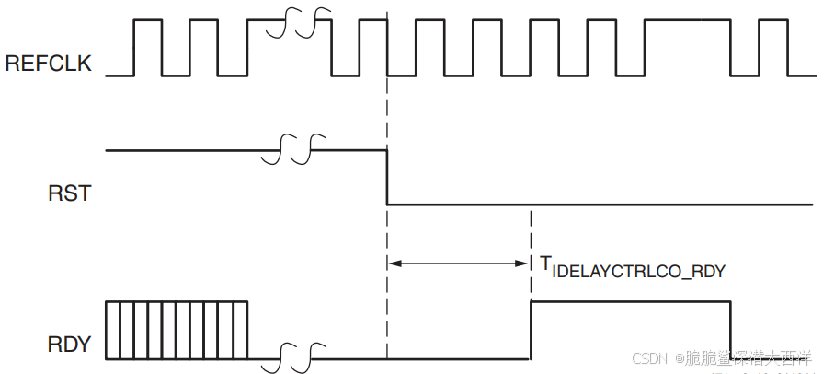

其中 RST 是复位,高电平有效。

RDY 信号是 IDELAYCTRL 模块的一个输出信号,用于指示 IDELAY 和 ODELAY 模块是否已经完成校准。RDY为高电平时:表示IDELAYCTRL已经完成初始化和校准,IDELAY和ODELAY模块可以正常工作,延时功能有效。 RDY为低电平时:表示IDELAYCTRL尚未完成初始化和校准,IDELAY和ODELAY模块的延时功能可能不可靠。

IDELAYCTRL 时序:

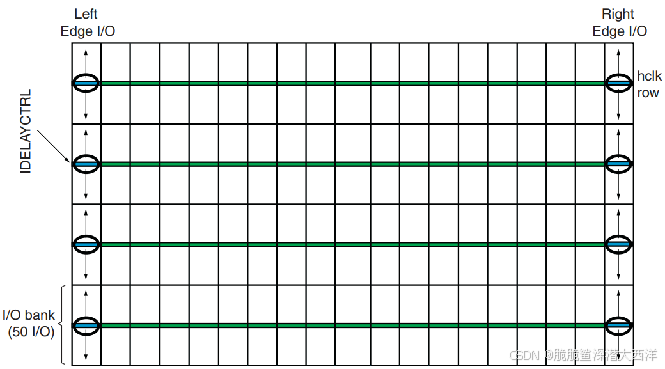

IDELAYCTRL 位置分布

IDELAYCTRL 模块存在于每个时钟区域的每个 I/O 列中。 IDELAYCTRL 模块只能校准其时钟区域内的所有 IDELAYE2 和 ODELAYE2 模块。

827

827

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?