一.基本知识

千兆以太网通过MAC和PHY芯片通信,MAC端可由FPGA实现,而PHY是物理芯片,只需要配置其工作模式,速率等等参数,便可正常运行。在前面的千兆以太网收发模块中我们并没有考虑配置PHY芯片,因为它在默认状态下也可以正常工作。本次设计主要学习如何配置PHY芯片。

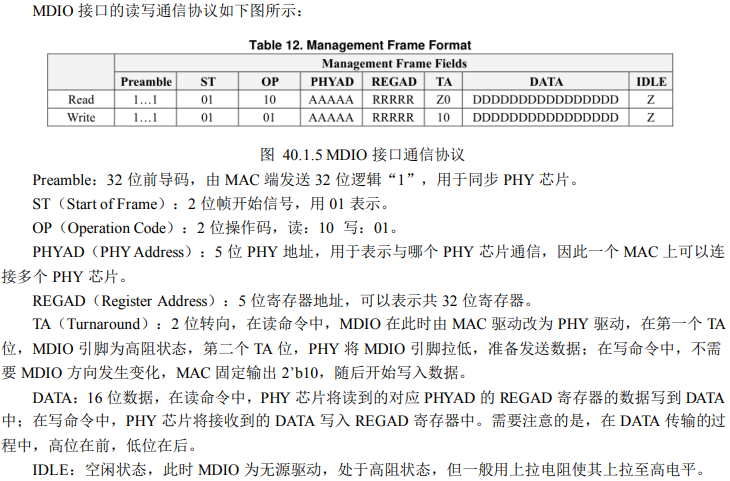

①通信协议

理解:协议分为读和写两种情况。可以看到两种情况都会有前导码等内容,一开始我的疑惑是写的时候为什么还要由mac端来发送前导码,不是应该由phy发送整个帧让mac端来接收并提取出data吗?(这是学了千兆以太网的惯性思维,千兆以太网就是一端发一端收),理清疑惑:mdio区别于千兆以太网这种两个端都能封装发送帧的通信模式,phy端只能读取或者写入phy内部寄存器,不能封装发送帧。

通信过程:

Ⅰ.写阶段:mac端依次发送前导码,开始位,读写标志位,phy芯片地址,寄存器地址,TA转向位(固定),要写入寄存器的数据等通信协议的内容,把数据写入phy内部寄存器。

Ⅱ.读阶段:mac端仍然发送前导码,开始位,读写标志位,phy芯片地址,寄存器地址,TA转向位(转向),此时mac输出变为高阻态,由phy芯片读取寄存器数据并输出。

可以看到,mdio数据信道在读阶段,可由mac端驱动,也可由phy芯片端驱动,之前的想法是这需要两条数据线,但其实一条就够了,在两端把数据接口设置为inout类型,就可以实现一个接口分时实现输入输出数据,便可实现本次通信协议的要求。(前面不理解是不知道或者忘了有inout口)。

②接口读写时序

本文详细介绍了MAC与PHY芯片在千兆以太网中的通信协议,包括读写阶段的过程。重点讨论了MDIO协议的时序设计,特别是inout端口在通信中的作用和实现。通过理解MDC时钟的上升沿与下降沿数据传输的原理,以及inout端口的状态控制,能够成功配置PHY芯片。同时,文中还提到了三段式状态机在设计中的应用,并展示了仿真模型及结果。

本文详细介绍了MAC与PHY芯片在千兆以太网中的通信协议,包括读写阶段的过程。重点讨论了MDIO协议的时序设计,特别是inout端口在通信中的作用和实现。通过理解MDC时钟的上升沿与下降沿数据传输的原理,以及inout端口的状态控制,能够成功配置PHY芯片。同时,文中还提到了三段式状态机在设计中的应用,并展示了仿真模型及结果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

522

522

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?