一、SV中的interface

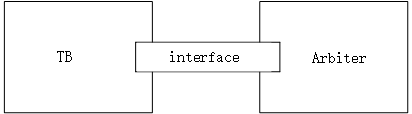

interface在SV中是唯一一个连接软硬件的桥梁。interface与module的使用性质很像。它可以定义端口,也可以定义双向信号,它还能使用always与initial语句,也可以定义task与function。其可以作为module的端口列表,也可以作为方法中的形式参数。

二、interface

- interface的定义与module类似

- 在interface的端口,一般只需要定义clk,rstn等公共信号,在变量列表中定义各个需要跟DUT和TB连接的logic变量。

- 接口也可以以来参数化方式提高复用性

- interface的例化与

注意!!!!!!

- 接口不能例化模块

- 接口可以例化接口

- 模块可以例化接口

- 模块可以例化模块

三、采样和数据驱动

竞争问题

为了避免在RTL仿真行为中发生的信号竞争问题,一般通过非阻塞赋值或者特定的信号延迟来解决同步问题。

- 在仿真中,为了尽量避免时序电路中时钟和驱动信号的时序竞争问题,我们需要给出尽量明确的驱动时序和采样时序。

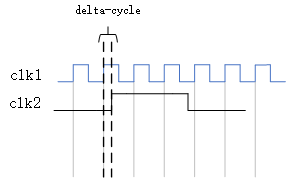

- 在组合电路中,时钟驱动会添加一个delta-cycle的延迟,delta-cycle如下

为了避免这种问题的产生,我们可以通过interface中生命clocking(时序块)和采样的时钟信号,用来做信号的同步核采样。clocking一般的方式如下

clocking bus @ (posedge clock1);

default input #10ns output #2ns;

input data, ready, enable;

output negedge ack;

input #1step addr;

endclocking

在这段代码中,采样变量data,ready,enable都是在clock1上升沿到来的前10ns进行采样的。ack是等时钟上升沿到来后的2ns进行驱动的。而addr信号是自定义采样信号,是在时钟上升沿到来的前1step进行采样。这里的1step也会使得采样发生在clock1上升沿的上一个时间片采样区域,既可以保证采样到的数据是上一个时钟周期的数据。clocking也可以在module与program中被定义。

四、Program

在SV中,一般用来结束仿真的方法是$stop() 和 $finshn(),但是在软件层面,program也可以隐式的来结束仿真。在program中最后一个initial过程块执行完成之后,就自动的结束仿真了。也可以使用 $exit() 来强制结束仿真。

注意!!!!!

在program中,不能使用always!!!!

3235

3235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?