目录

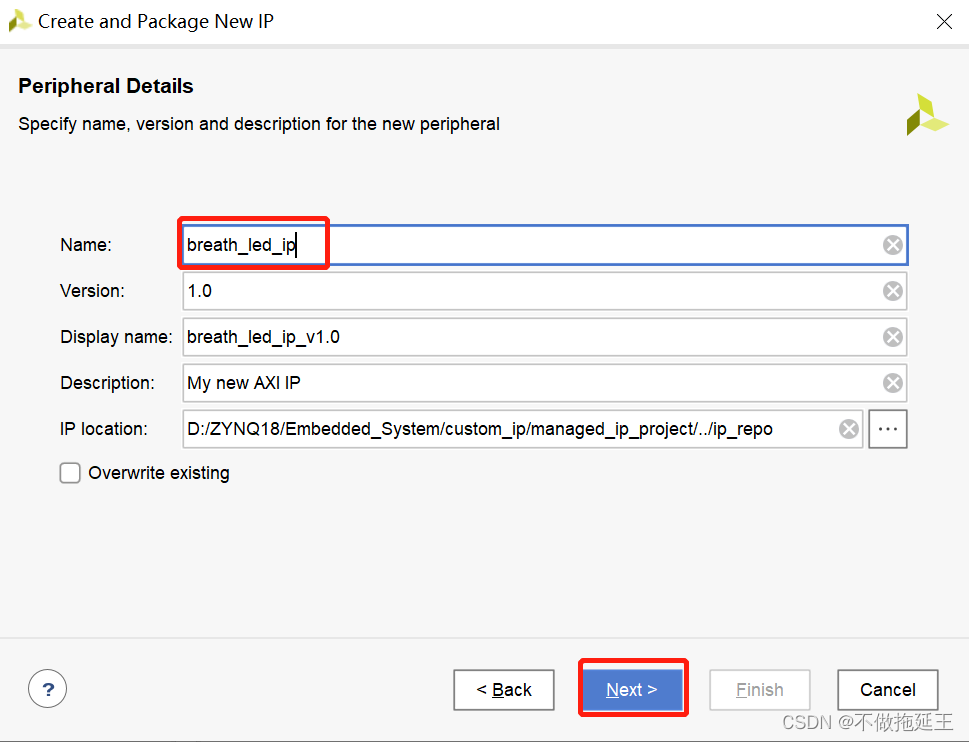

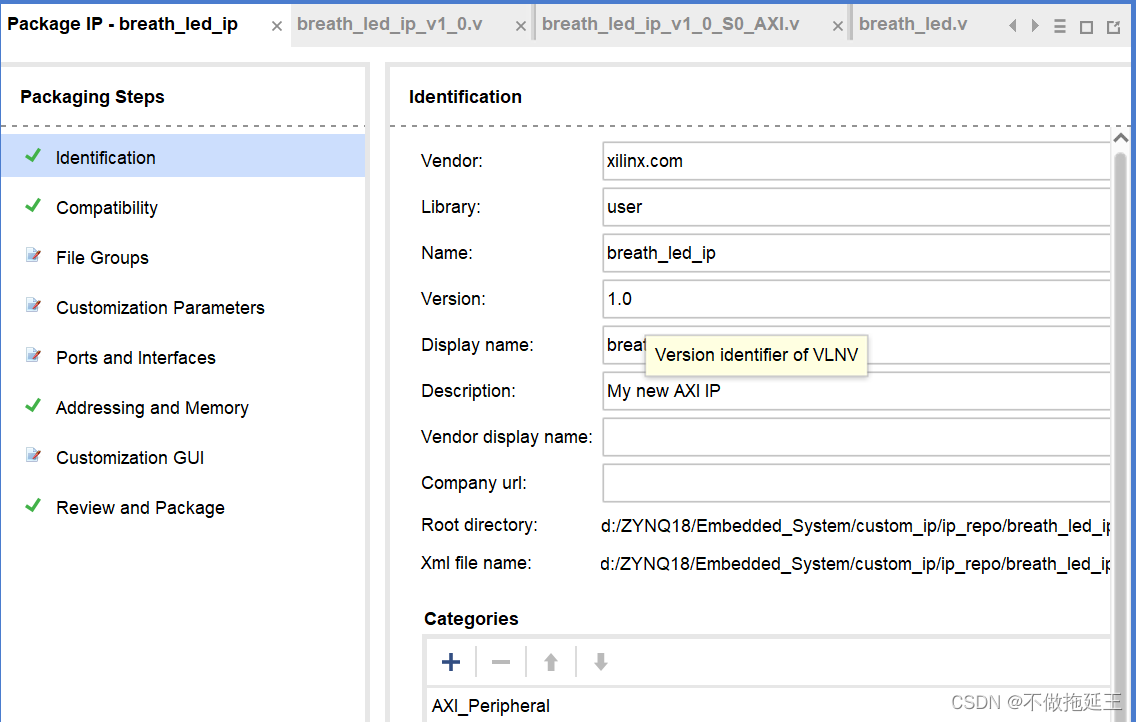

1-5 分别设置 IP 核名称(Name)、版本号(Version)、显示名(Display name)、描述(Description) 和路径(IP location)。

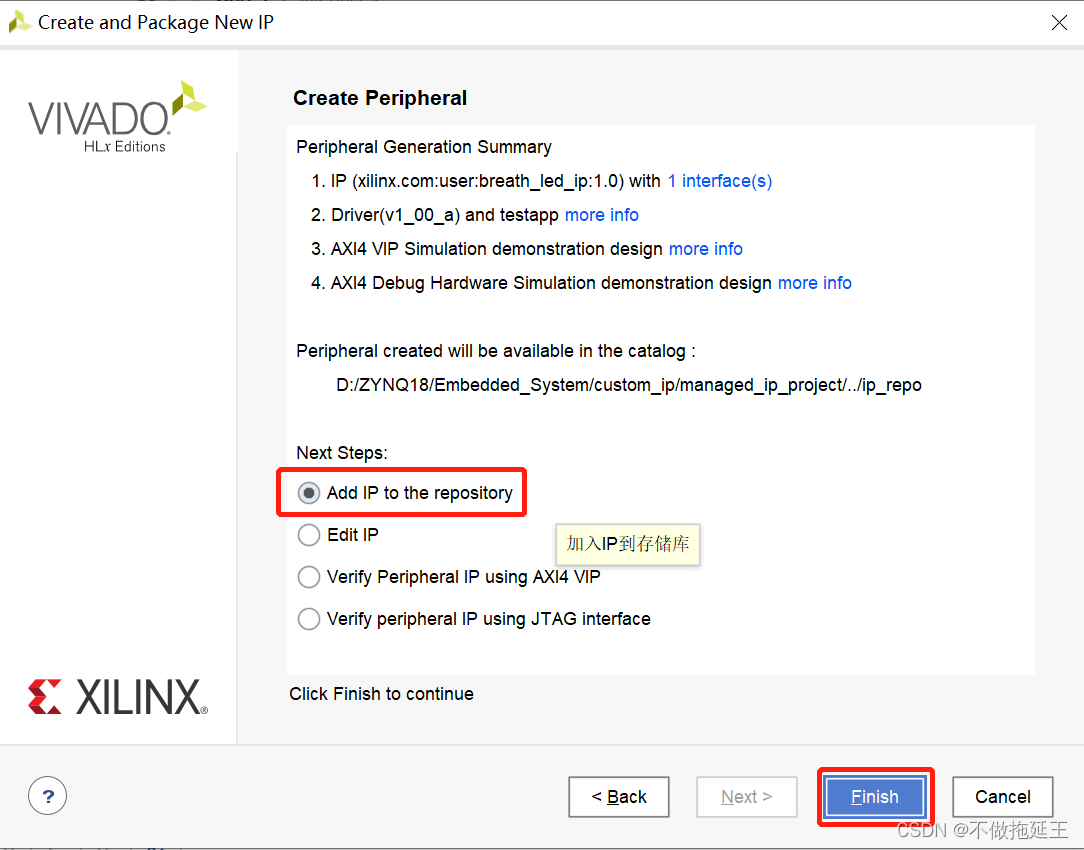

1-7 将 IP 添加至 IP 库中,完成 IP 核的创建和封装。

1-8 对 breath_led_ip_v1.0 IP 核进行编辑

1-11 Add or Create design source

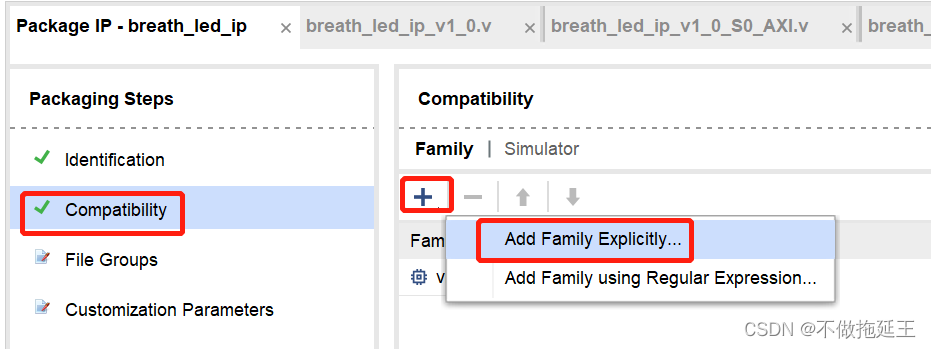

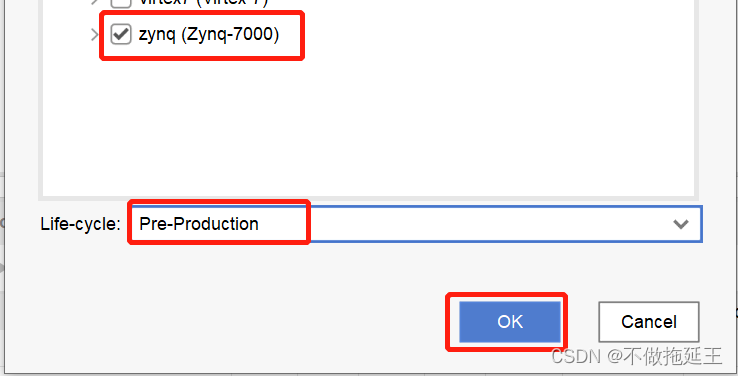

1-15 点击 Compatibility,修改该 IP 核支持的器件。

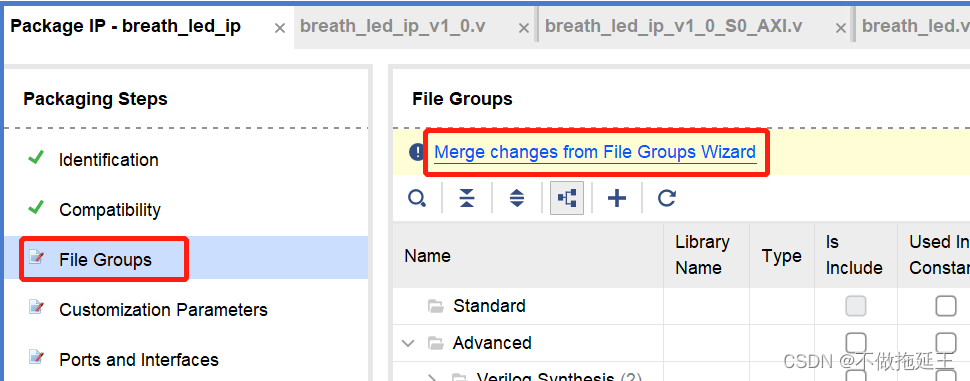

1-16 点击 File Groups,然后点击界面上的“Merge Changes from Gile Groups Wizard”

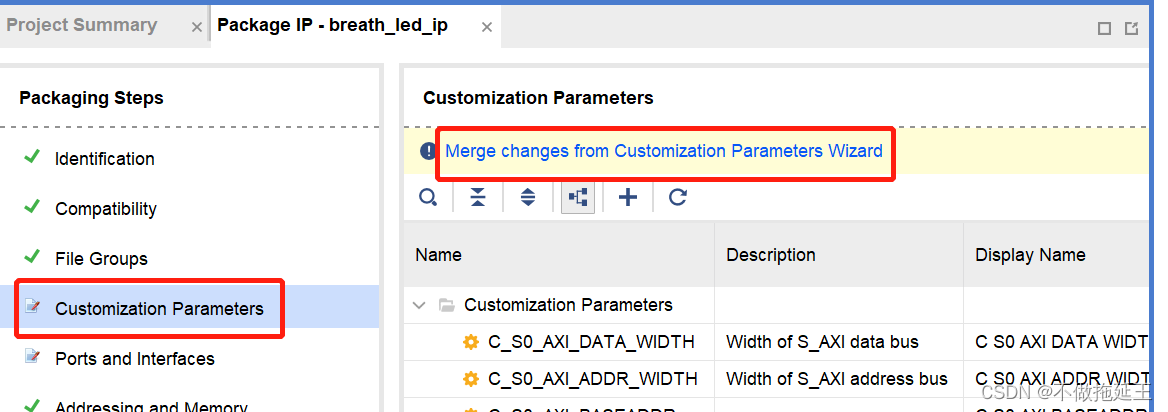

1-17 点击 Customization Parameters,点击界面上的“Merge Changes from Customization Parameters Wizard”

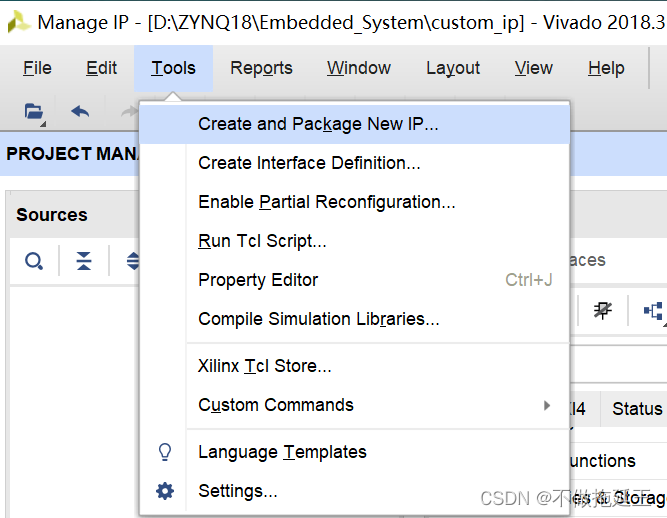

step2:创建 Vivado 工程,将自定义的IP核添加至本工程的IP库中

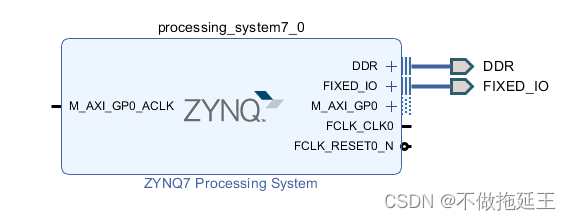

step3:使用 IP Integrator 创建 Processing System

3-2 添加“ZYNQ7 Processing System”IP

3-3 添加 UART 控制器,修改 DDR3 的存储器类型型号,其它保持默认。

3-5 Make External Regenerate Layout

在 Vivado 软件中,我们可以很方便的通过创建和封装 IP 向导的方式来自定义 IP 核。自定义 IP 核可以定制化系统设计,以达到设计重用的目的,可以很大程度上简化系统设计和缩短产品上市的时间。本章我们将向大家介绍自定义 IP 核的方法。

1 简介

2 实验任务

3 硬件设计

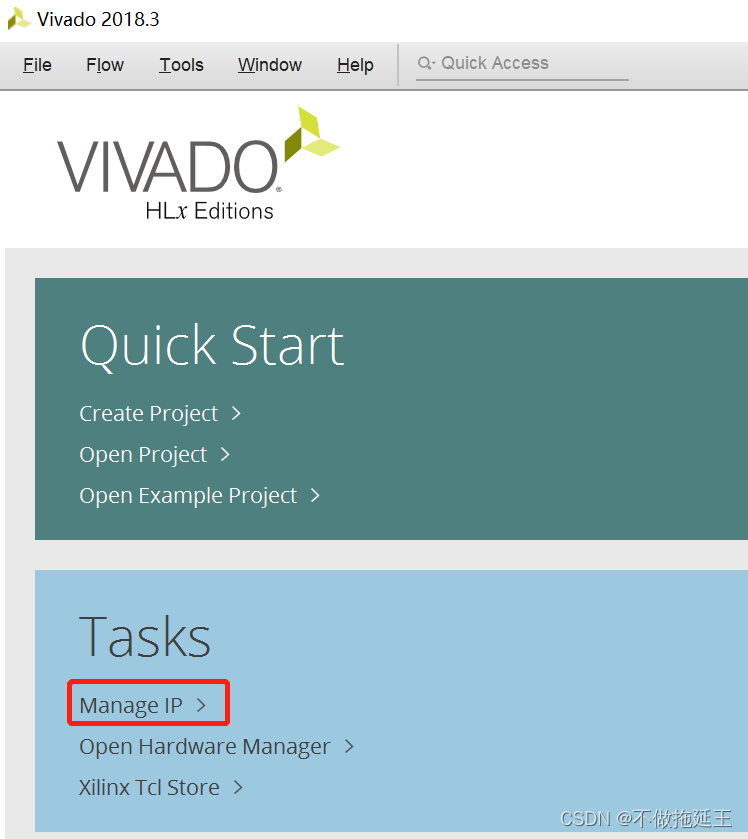

step1:创建一个新的 IP 核

1-1 New IP Location

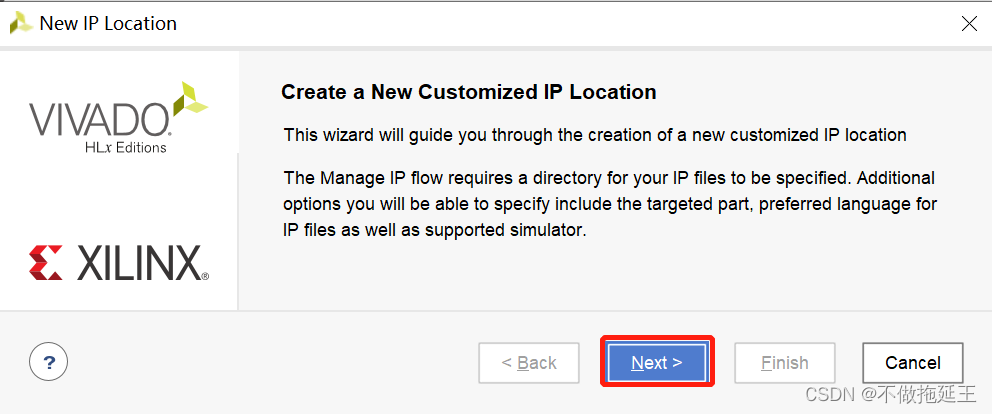

1-2 完成 Manage IP工程的创建

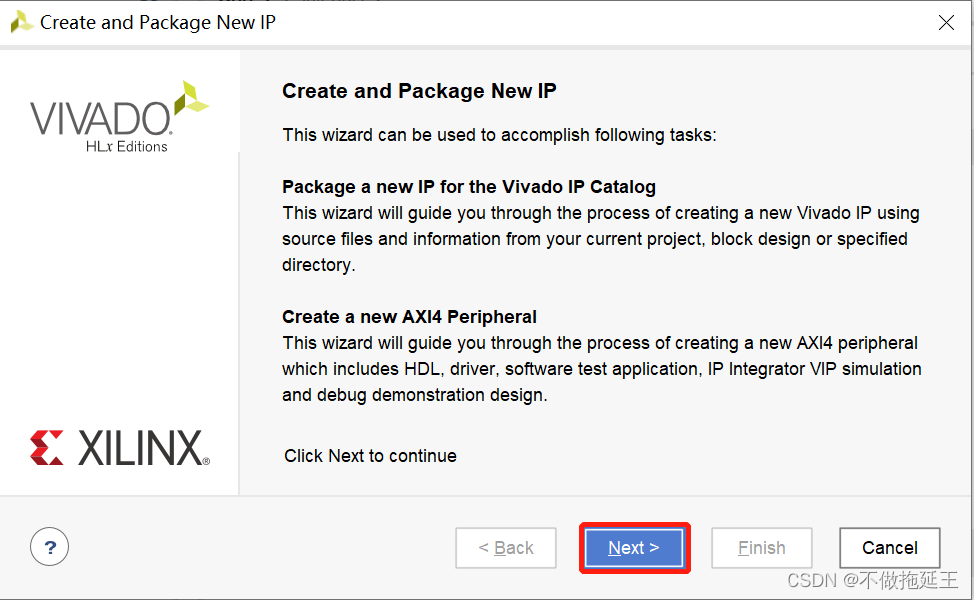

在弹出的界面中选择“Next”

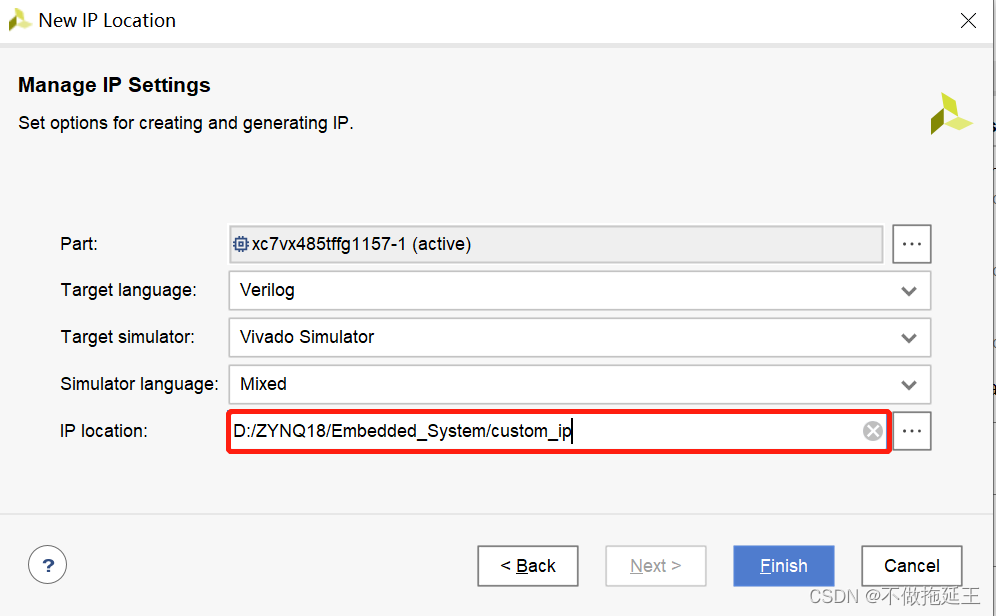

1-3 工程创建完成后,运行创建和封装 IP 向导。

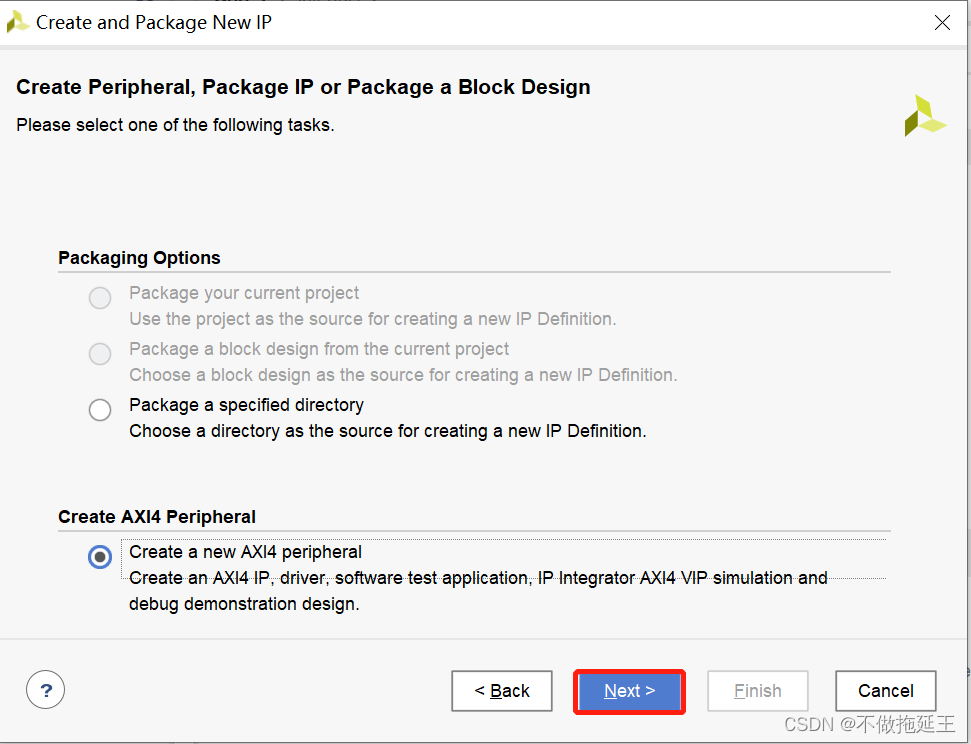

1-4 选择创建一个带 AXI 接口的 IP 核

1-5 分别设置 IP 核名称(Name)、版本号(Version)、显示名(Display name)、描述(Description) 和路径(IP location)。

1-6 对 AXI 接口进行设置

Name(名称):这里修改成 S0_AXI。

1-7 将 IP 添加至 IP 库中,完成 IP 核的创建和封装。

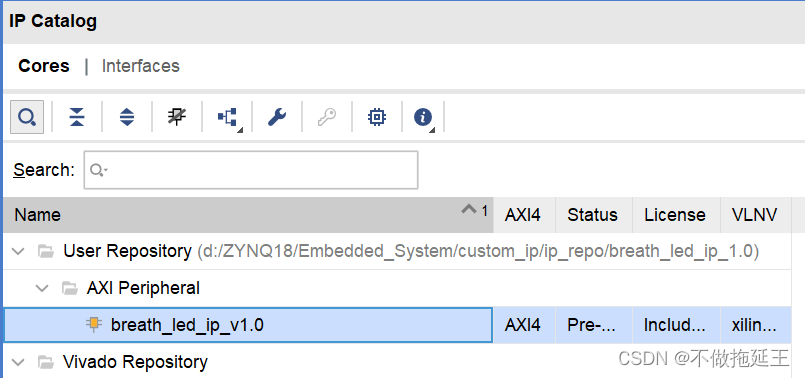

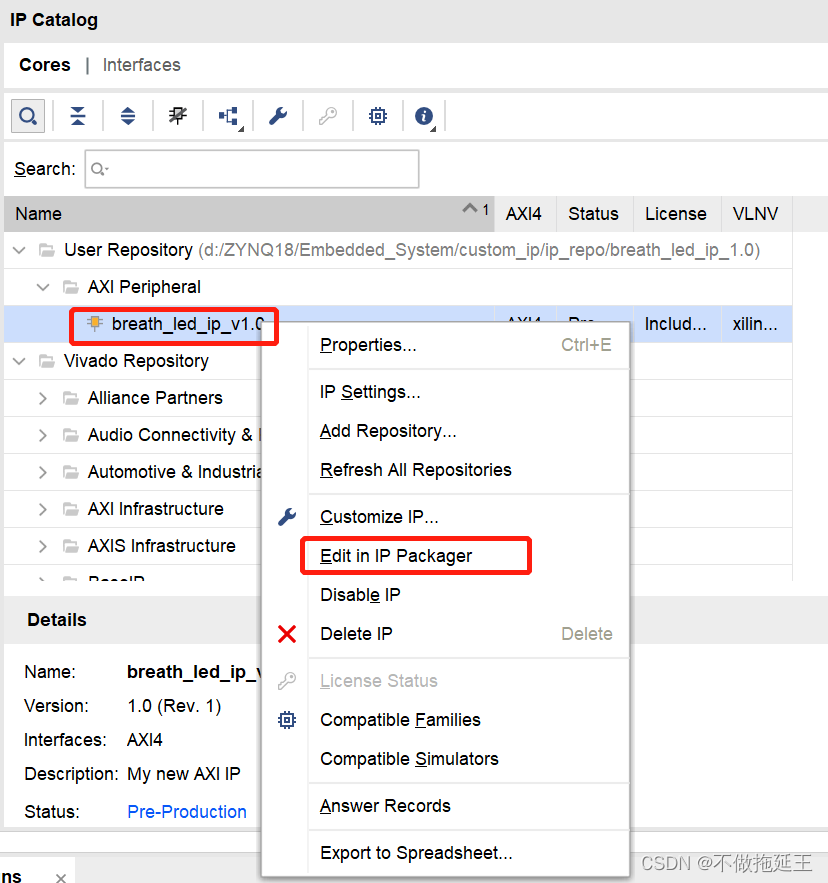

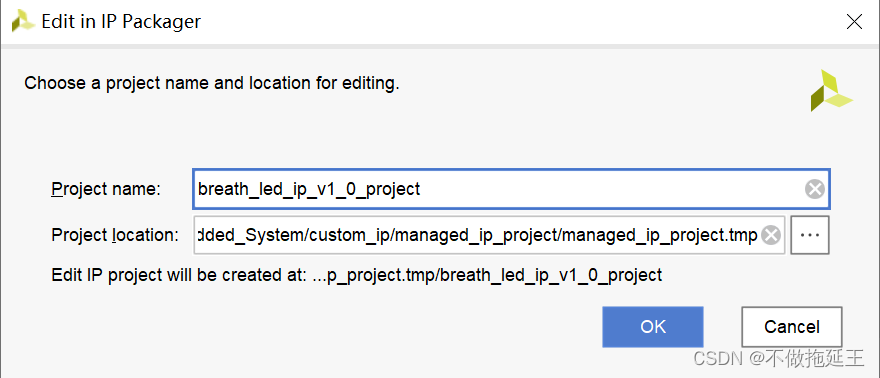

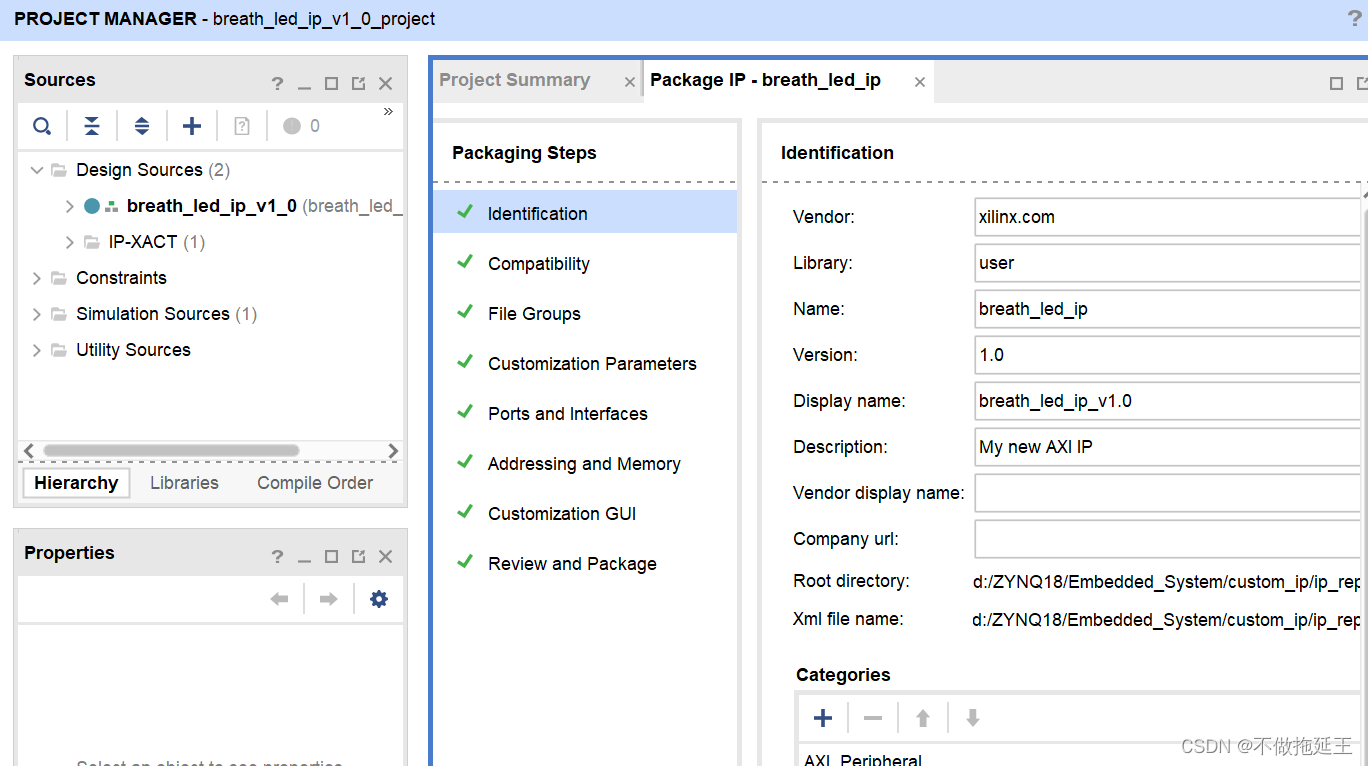

1-8 对 breath_led_ip_v1.0 IP 核进行编辑

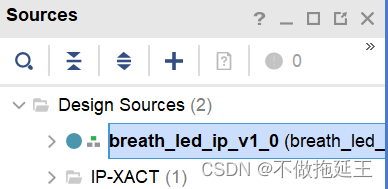

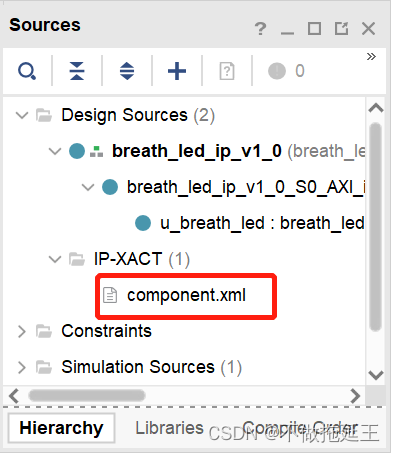

此时会打开一个新的工程,如下图所示:

1-9 添加代码

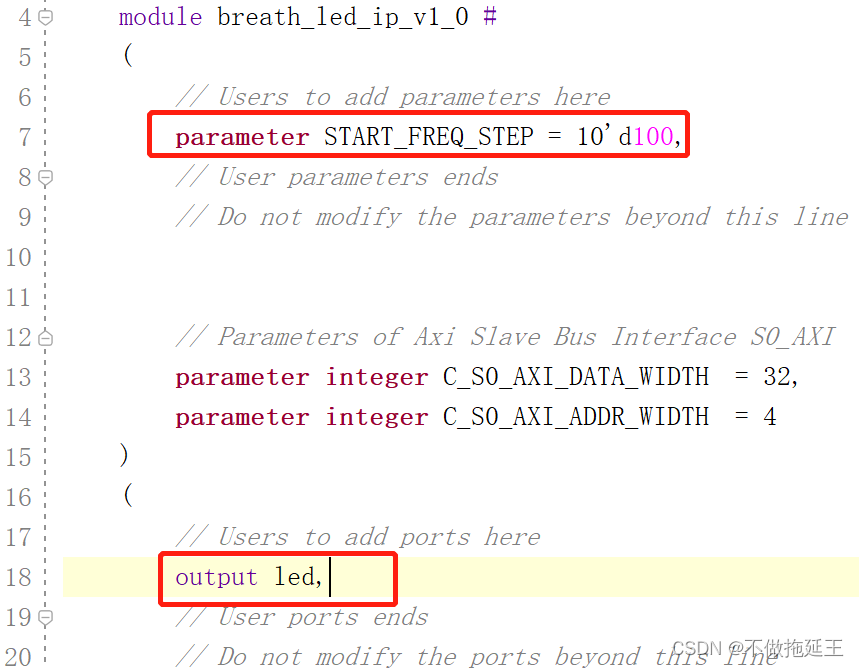

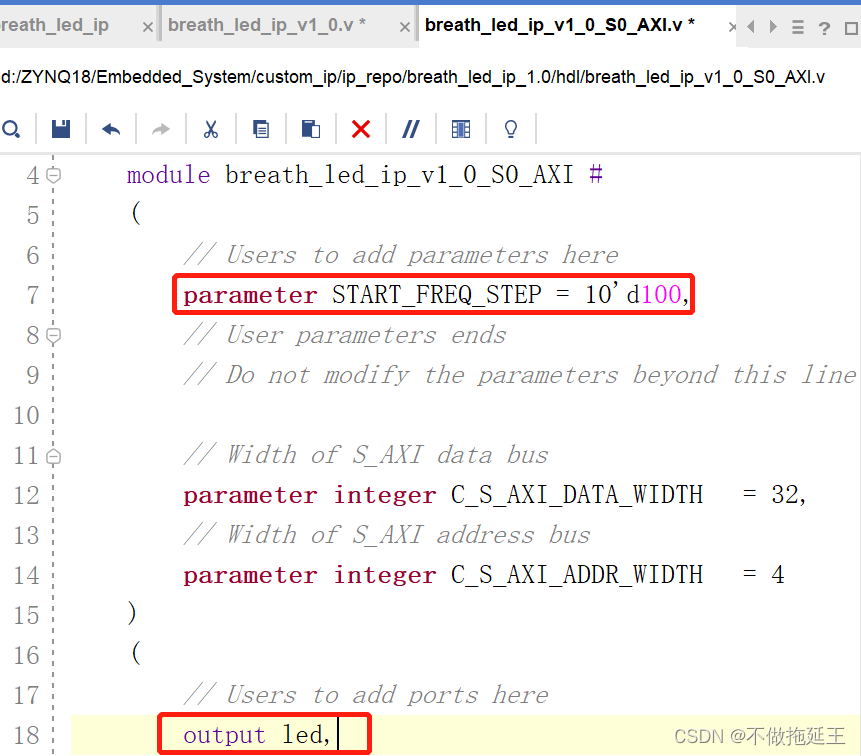

双击 breath_led_ip_v1_0

parameter START_FREQ_STEP = 10'd100 ,

这个参数用于设置呼吸灯默认的呼吸频率,然后在代码的第 18 行添加如下代码:

output led ,

.START_FREQ_STEP(START_FREQ_STEP),

. led ( led ),

代码添加后,按下键盘键 Ctrl+S 保存。如下图所示:

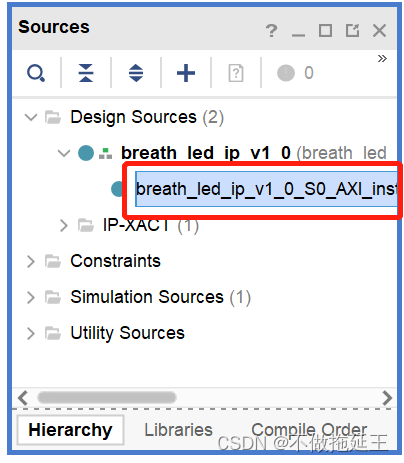

1-10 添加代码

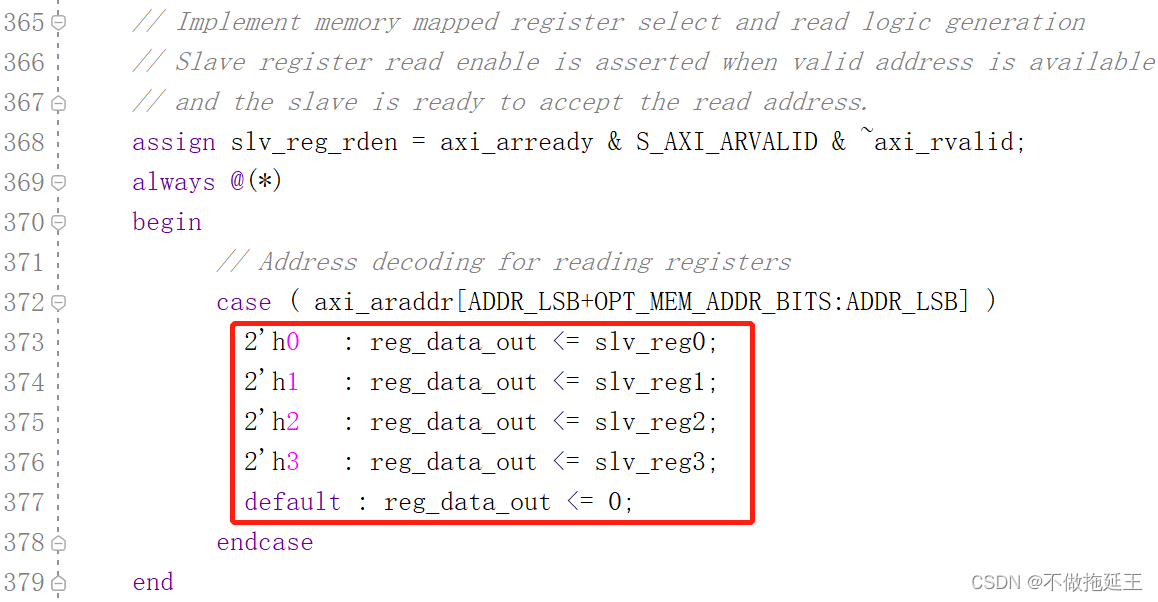

双击 breath_led_ip_v1_0 下的 breath_led_ip_v1_0_S0_AXI_inst,如下图所示:

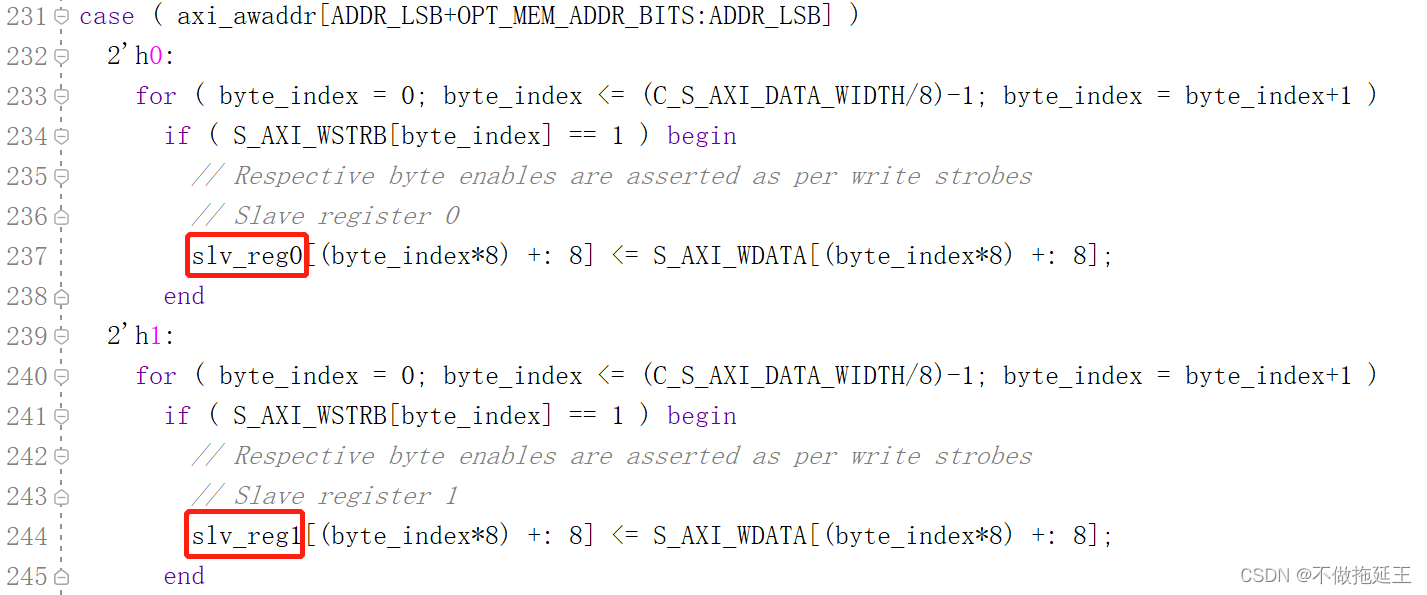

parameter START_FREQ_STEP = 10'd100 ,

output led ,

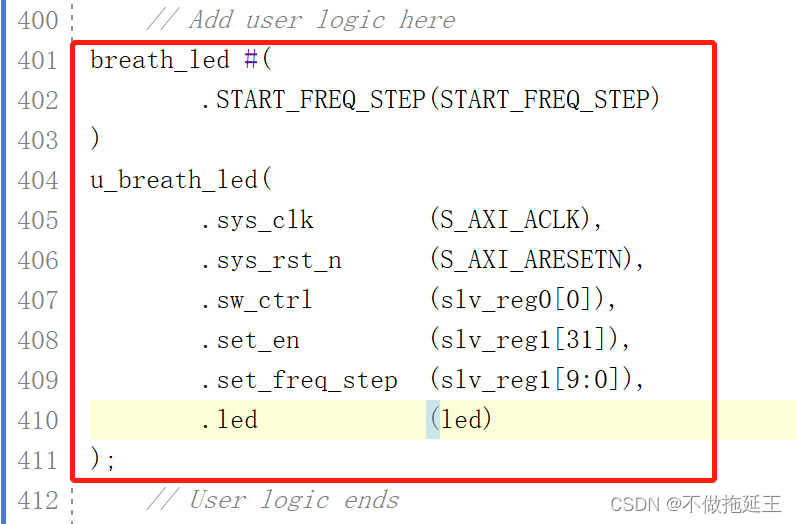

同时我们还需要在代码的第 401 行例化 breath_led.v 文件,代码如下:

breath_led #(. START_FREQ_STEP ( START_FREQ_STEP ))u_breath_led (. sys_clk ( S_AXI_ACLK ),. sys_rst_n ( S_AXI_ARESETN ),. sw_ctrl ( slv_reg0 [ 0 ]),. set_en ( slv_reg1 [ 31 ]),. set_freq_step ( slv_reg1 [ 9 : 0 ]),. led ( led ));

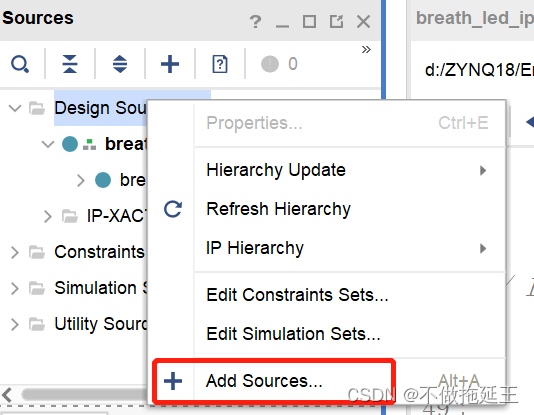

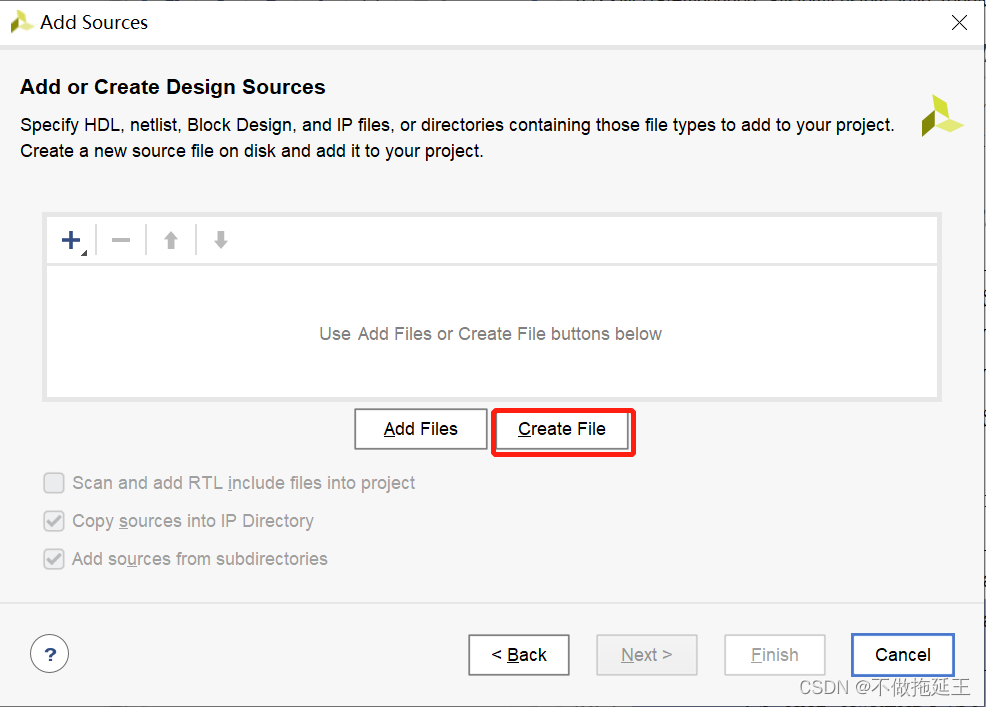

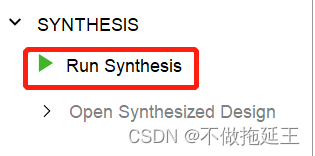

1-11 Add or Create design source

在弹出的模块定义界面中点击“OK”按钮,接下来在弹出的确认按钮中点击“YES”。

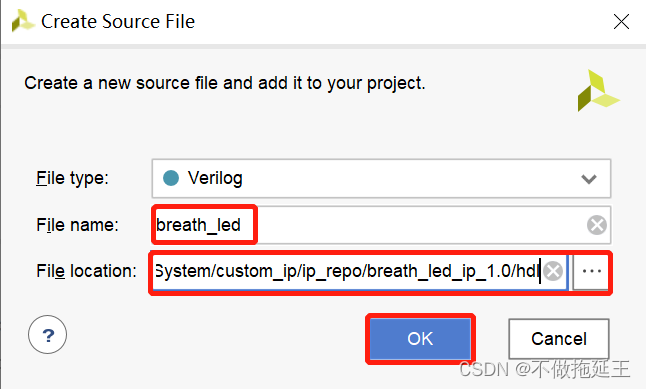

1-12 编辑breath_led.v

双击 u_breath_led(breath_led.v)文件,如下图所示:

打开 breath_led.v 文件后,开始编辑代码,代码如下:

module breath_led(

input sys_clk , //时钟信号

input sys_rst_n , //复位信号

input sw_ctrl , //呼吸灯开关控制信号 1:亮 0:灭

input set_en , //设置呼吸灯频率设置使能信号

input [9:0] set_freq_step , //设置呼吸灯频率变化步长

output led //LED

);

//*****************************************************

//** main code

//*****************************************************

//parameter define

parameter START_FREQ_STEP = 10'd100; //设置频率步长初始值

//reg define

reg [15:0] period_cnt ; //周期计数器

reg [9:0] freq_step ; //呼吸灯频率间隔步长

reg [15:0] duty_cycle ; //设置高电平占空比的计数点

reg inc_dec_flag; //用于表示高电平占空比的计数值,是递增还是递减

//为 1 时表示占空比递减,为 0 时表示占空比递增

//wire define

wire led_t ;

//将周期信号计数值与占空比计数值进行比较,以输出驱动 led 的 PWM 信号

assign led_t = ( period_cnt <= duty_cycle ) ? 1'b1 : 1'b0 ;

assign led = led_t & sw_ctrl;

//周期信号计数器在 0-50_000 之间计数

always @ (posedge sys_clk) begin

if (!sys_rst_n)

period_cnt <= 16'd0;

else if(!sw_ctrl)

period_cnt <= 16'd0;

else if( period_cnt == 16'd50_000 )

period_cnt <= 16'd0;

else

period_cnt <= period_cnt + 16'd1;

end

//设置频率间隔

always @(posedge sys_clk) begin

if(!sys_rst_n)

freq_step <= START_FREQ_STEP;

else if(set_en) begin

if(set_freq_step == 0)

freq_step <= 10'd1;

else if(set_freq_step >= 10'd1_000)

freq_step <= 10'd1_000;

else

freq_step <= set_freq_step;

end

end

//设定高电平占空比的计数值

always @(posedge sys_clk) begin

if (sys_rst_n == 1'b0) begin

duty_cycle <= 16'd0;

inc_dec_flag <= 1'b0;

end

else if(!sw_ctrl) begin //呼吸灯开关关闭时,信号清零

duty_cycle <= 16'd0;

inc_dec_flag <= 1'b0;

end

//每次计数完了一个周期,就调节占空比计数值

else if( period_cnt == 16'd50_000 ) begin

if( inc_dec_flag ) begin //占空比递减

if( duty_cycle == 16'd0 )

inc_dec_flag <= 1'b0;

else if(duty_cycle < freq_step)

duty_cycle <= 16'd0;

else

duty_cycle <= duty_cycle - freq_step;

end

else begin //占空比递增

if( duty_cycle >= 16'd50_000 )

inc_dec_flag <= 1'b1;

else

duty_cycle <= duty_cycle + freq_step;

end

end

else //未计数完一个周期时,占空比保持不变

duty_cycle <= duty_cycle ;

end

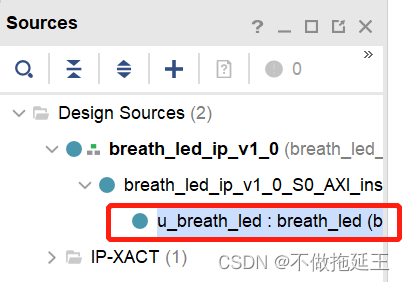

endmodule1-13 Run Synthesis

1-14 设置 IP 封装

1-15 点击 Compatibility,修改该 IP 核支持的器件。

1-16 点击 File Groups,然后点击界面上的“Merge Changes from Gile Groups Wizard”

如下图所示:

1-17 点击 Customization Parameters,点击界面上的“Merge Changes from Customization Parameters Wizard”

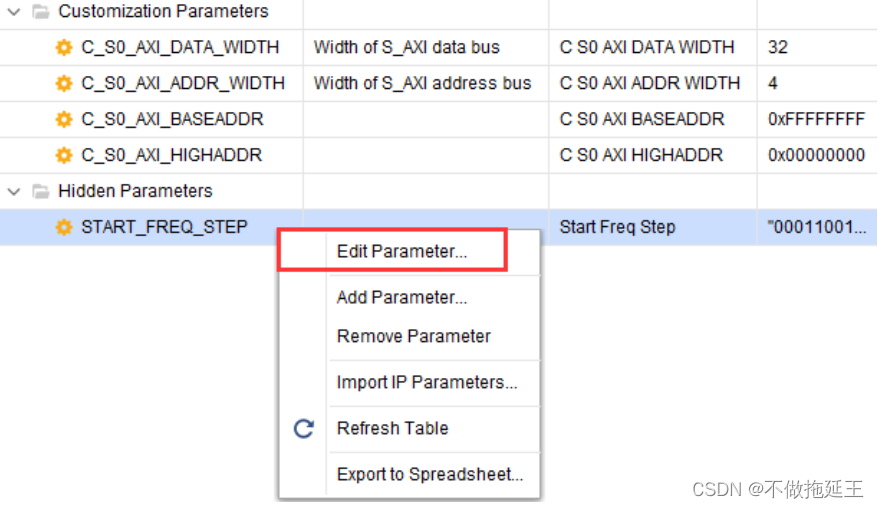

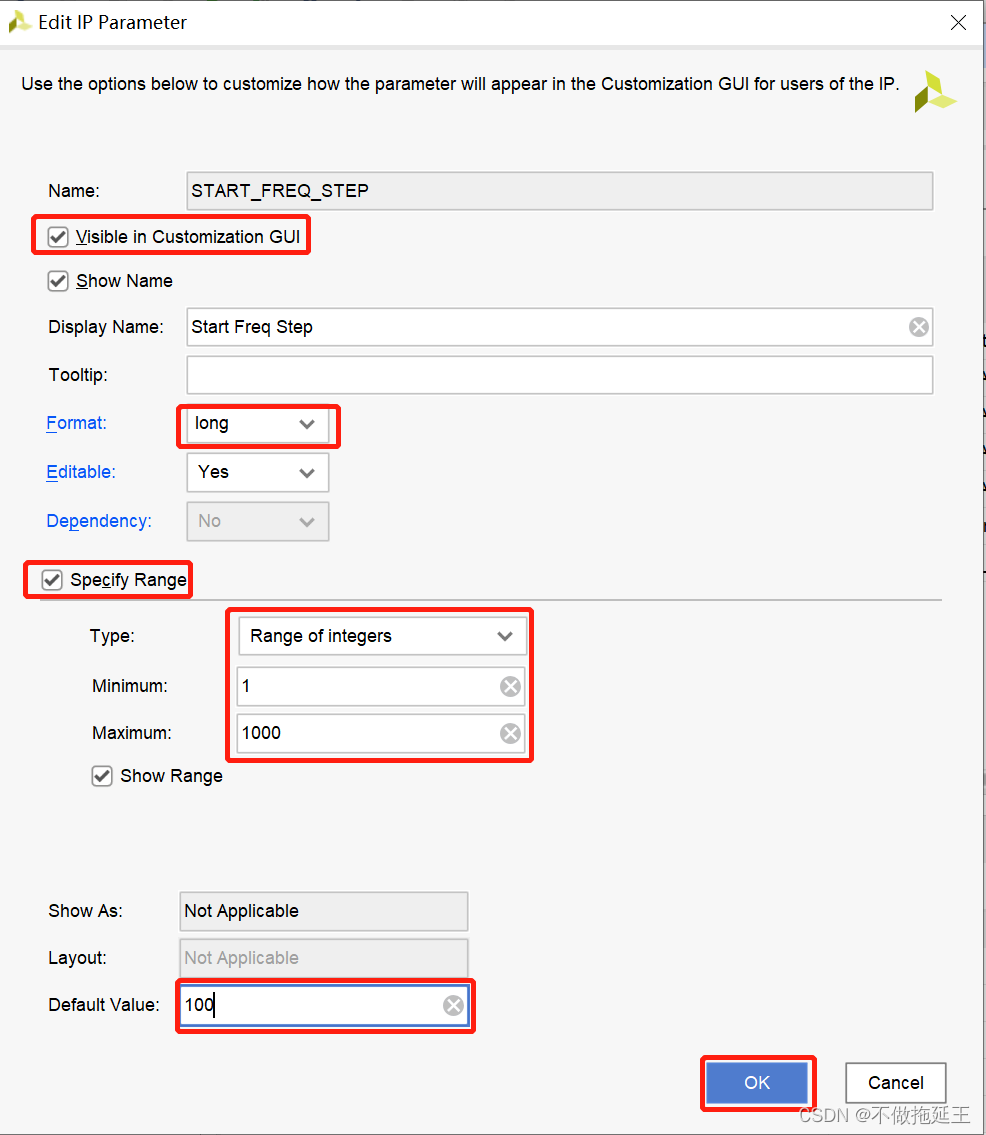

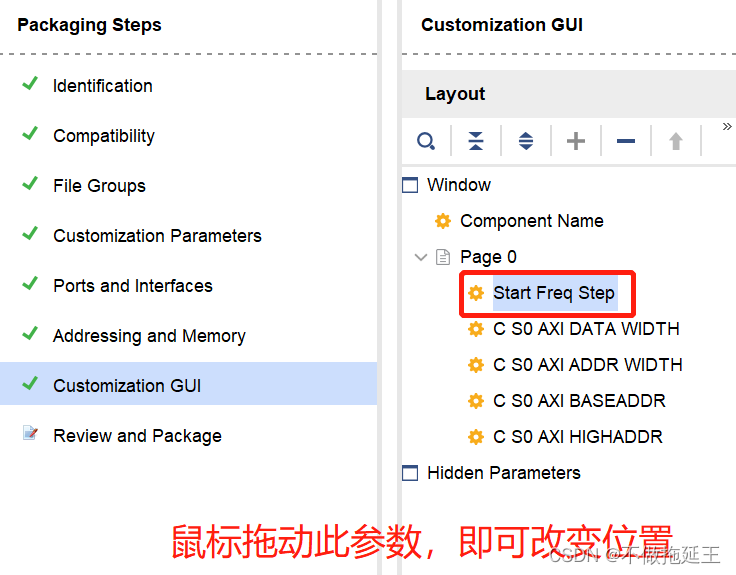

1-18 调整参数在 GUI 显示的位置

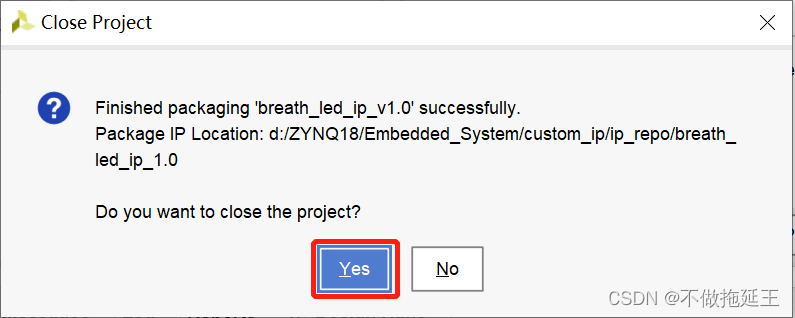

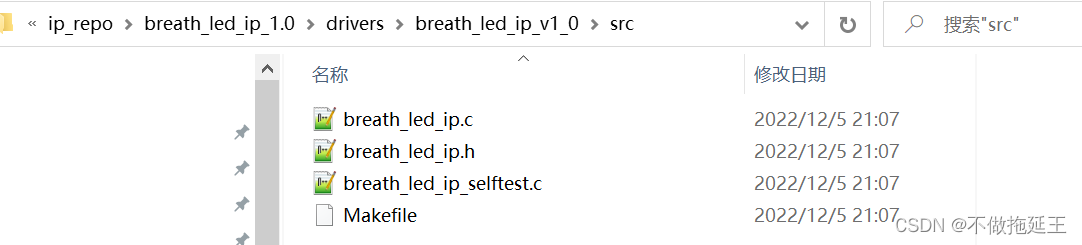

1-19 更新总结界面,封装IP

点击“Review and Package”,然后点击“IP has been modified”更新总结界面,最后点击“Re-Package IP”,如下图所示:

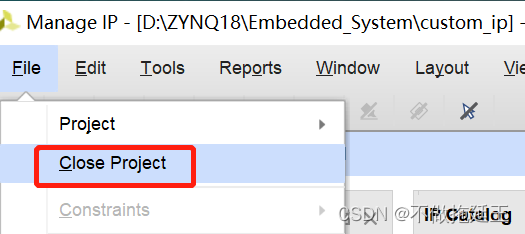

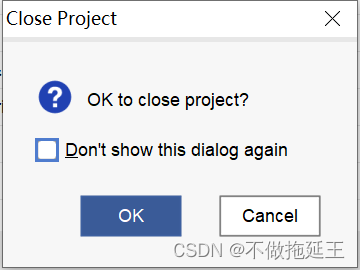

在 Manage IP 工程界面下,点击菜单栏的“File”,选择“Close Project”关闭工程,如下图所示:

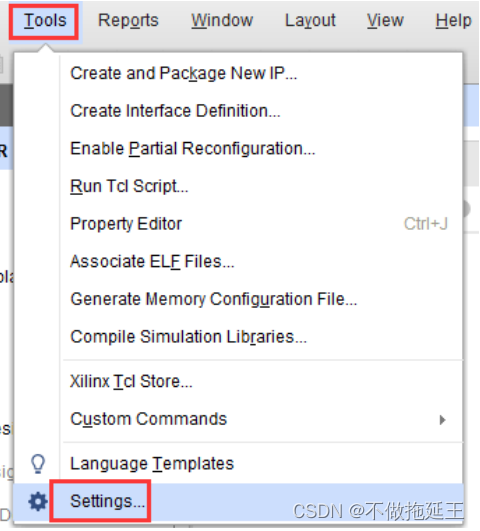

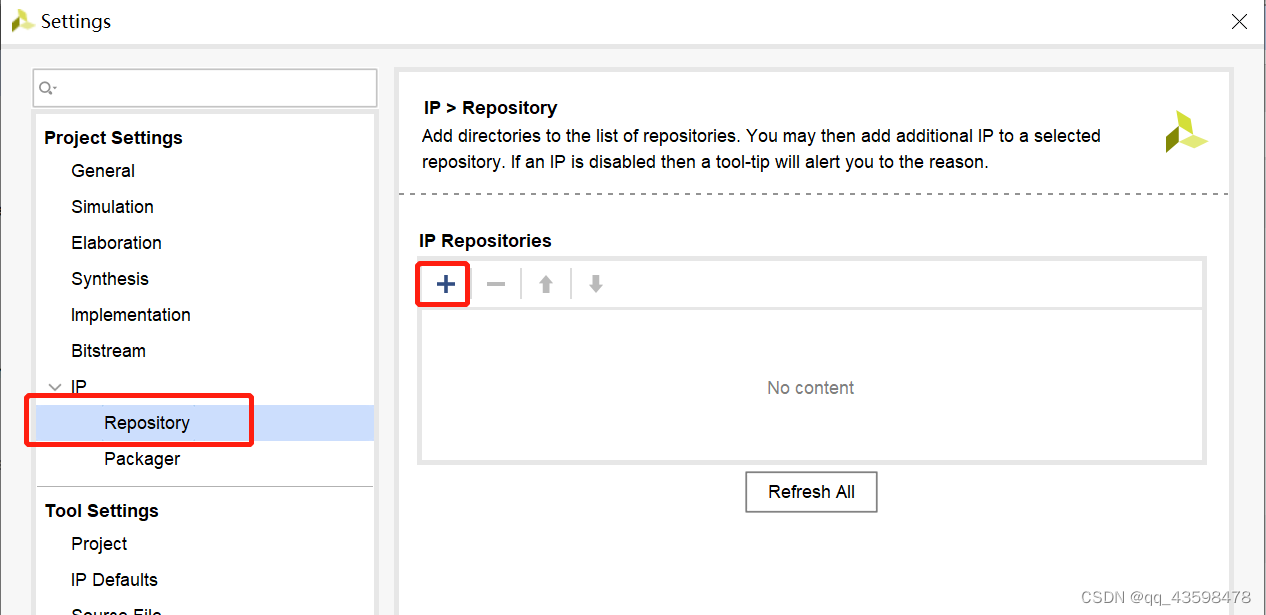

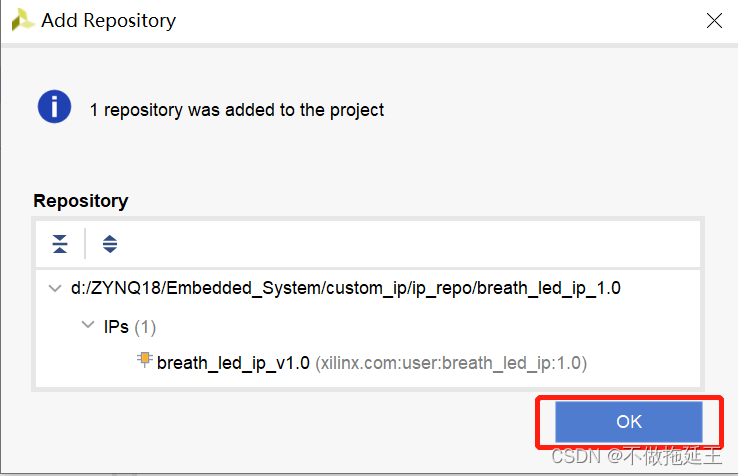

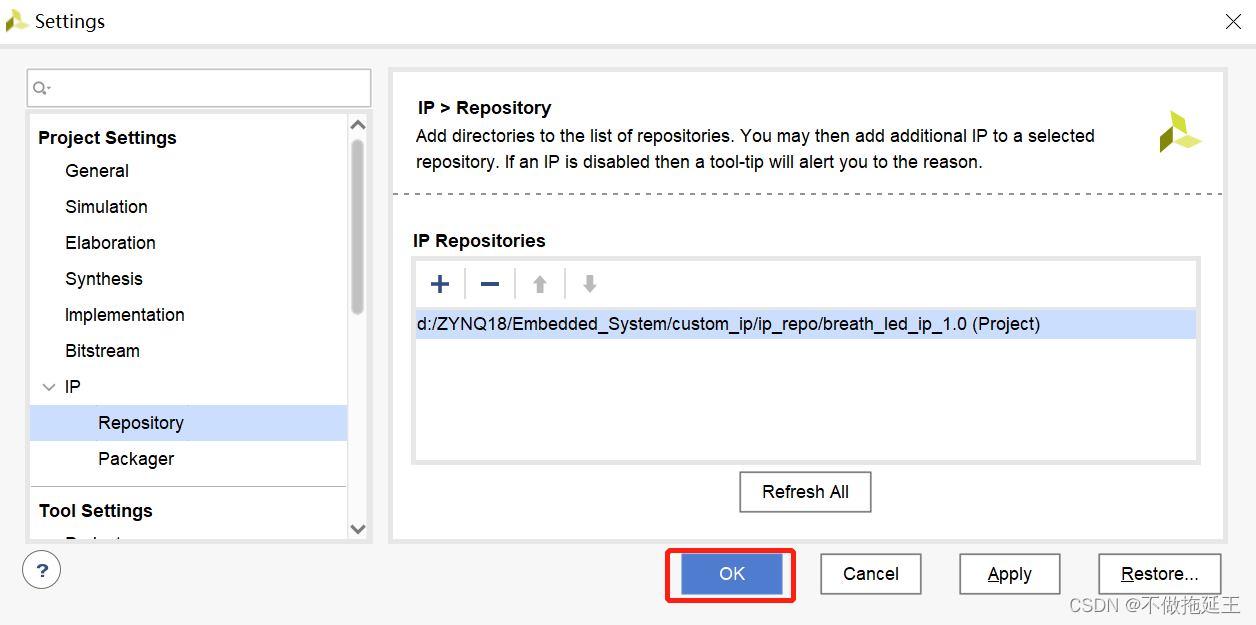

step2:创建 Vivado 工程,将自定义的IP核添加至本工程的IP库中

step3:使用 IP Integrator 创建 Processing System

3-1 Create Block Design

3-2 添加“ZYNQ7 Processing System”IP

3-3 添加 UART 控制器,修改 DDR3 的存储器类型型号,其它保持默认。

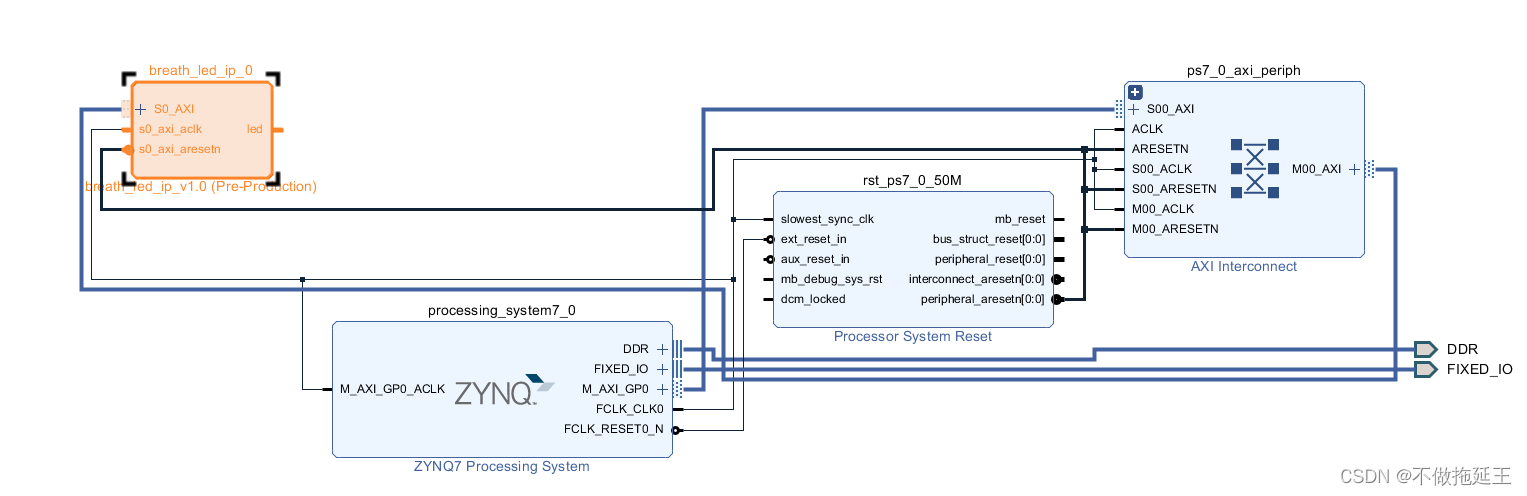

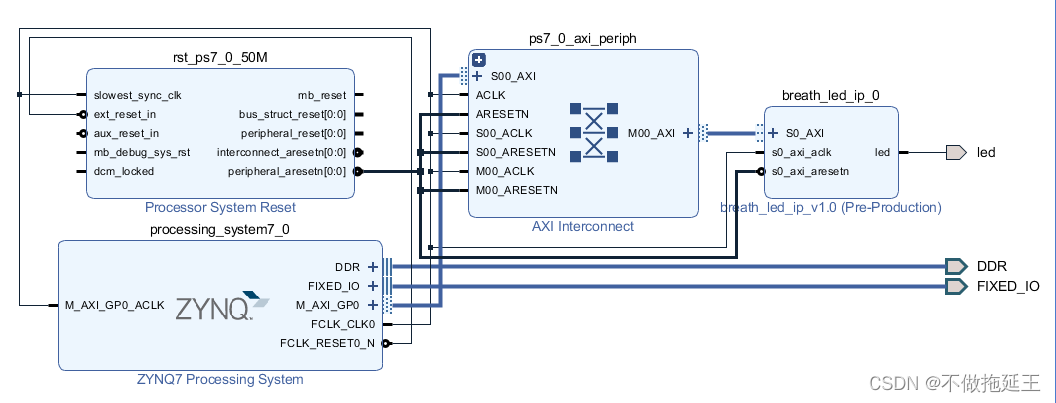

3-4 添加 Breath LED IP 核

添加完成后,可以双击 led IP 核来设置参数。这里不作修改。

3-5 Make External Regenerate Layout

step4:生成顶层 HDL 模块

4-1 Generate Output Products

4-2 Create HDL Wrapper

step5:生成 Bitstream 文件并导出到 SDK

5-1 Open Elaborated Design

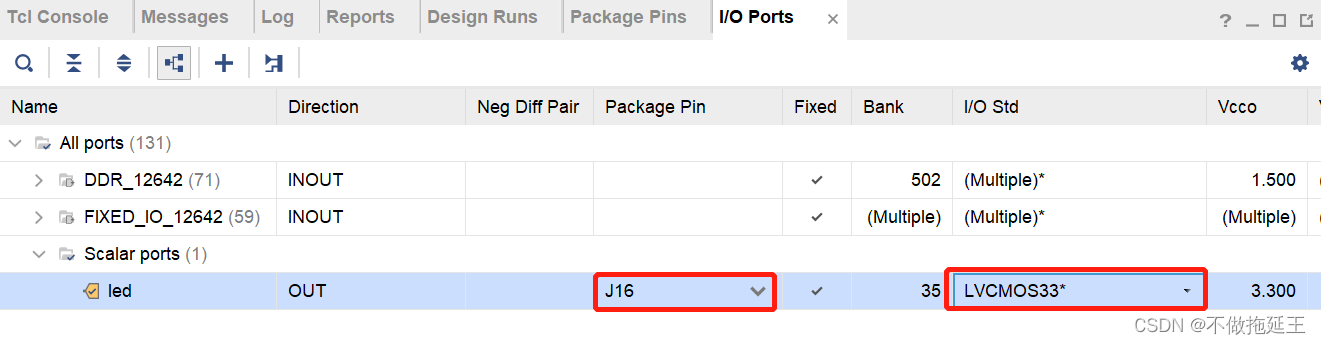

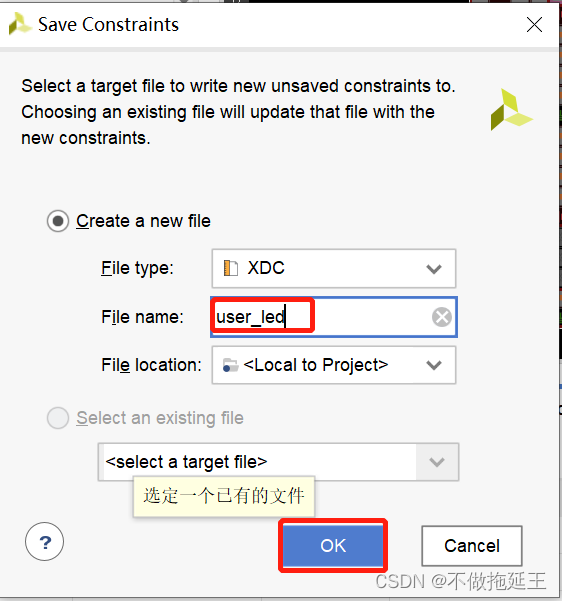

5-2 保存管脚约束

1208

1208

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?