procise纯PL流程点灯记录

一、概述

此篇记录使用procise工具构造JFMQL15T 纯PL工程,显示PL_LED闪烁;

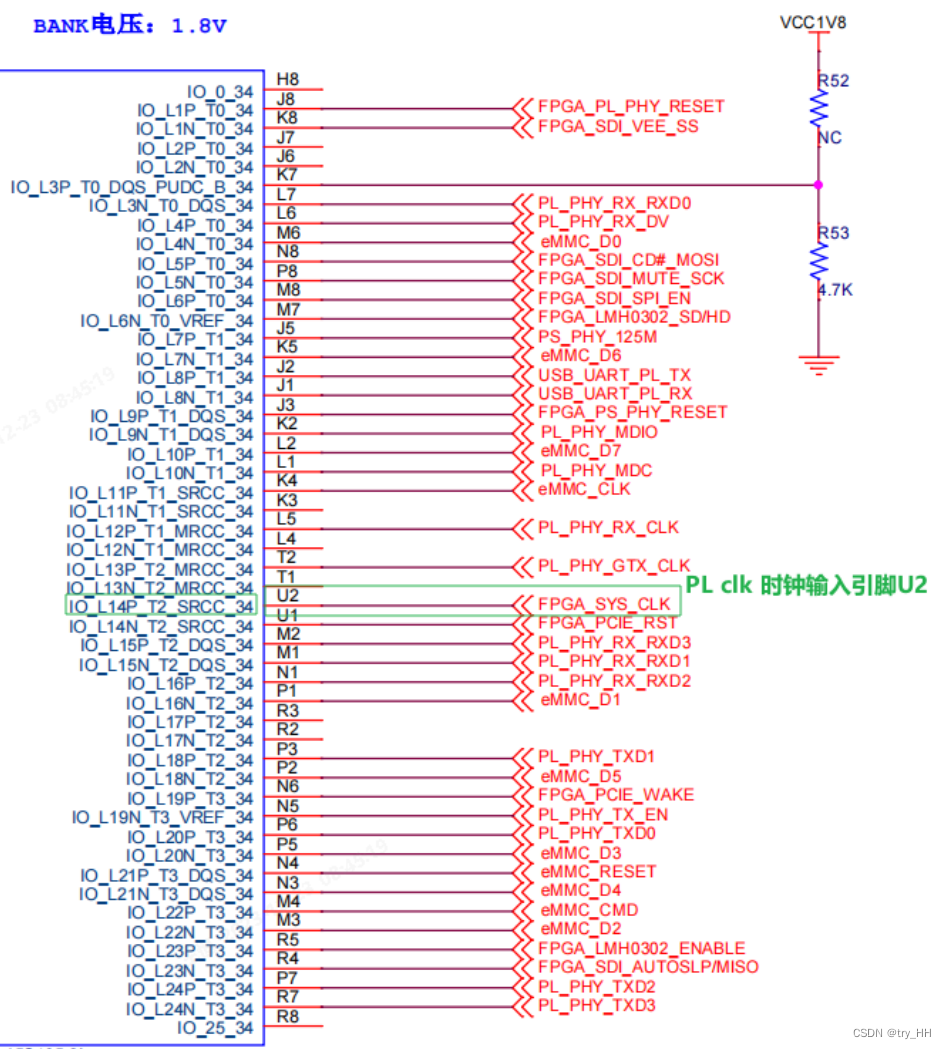

硬件说明如下:

时钟引脚 Pl_CLK: U2 ,IO_L14P_T2_SRCC_34

PL_LED1 : E2, IO_L17P_T2_AD5P_35 PL_LED2: D6, IO_L2N_T0_AD8N_35

PL_LED3 : F5, IO_L5P_T0_AD9P_35 PL_LED4: E3, IO_L21N_T3_DQS_AD14N_35

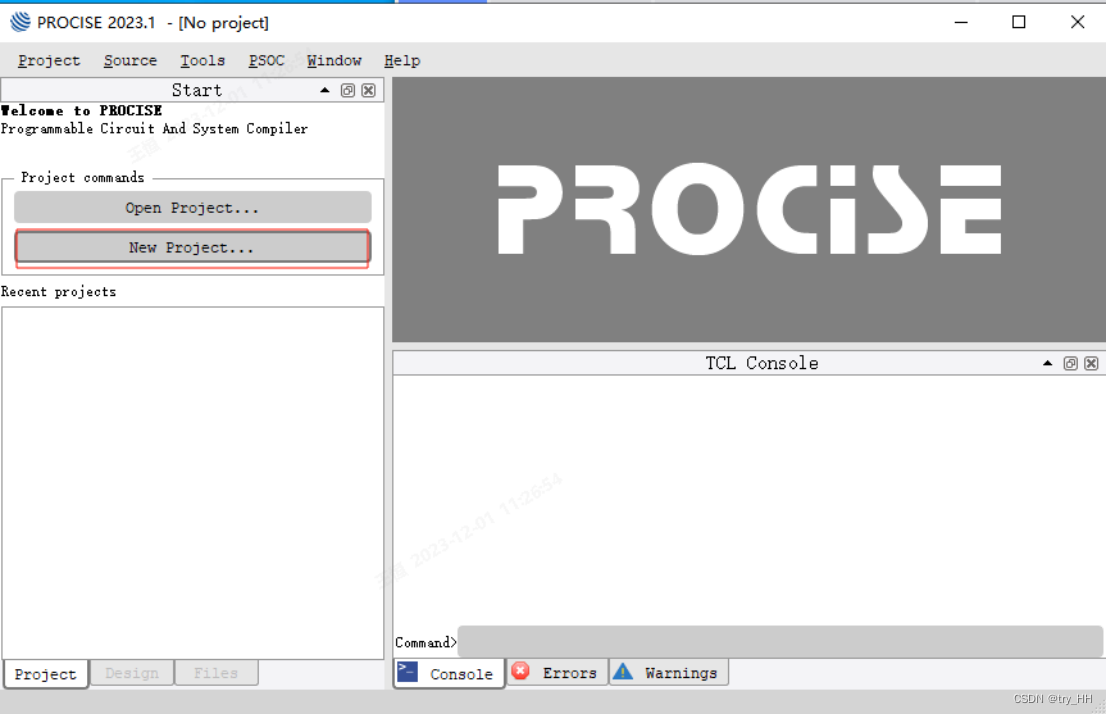

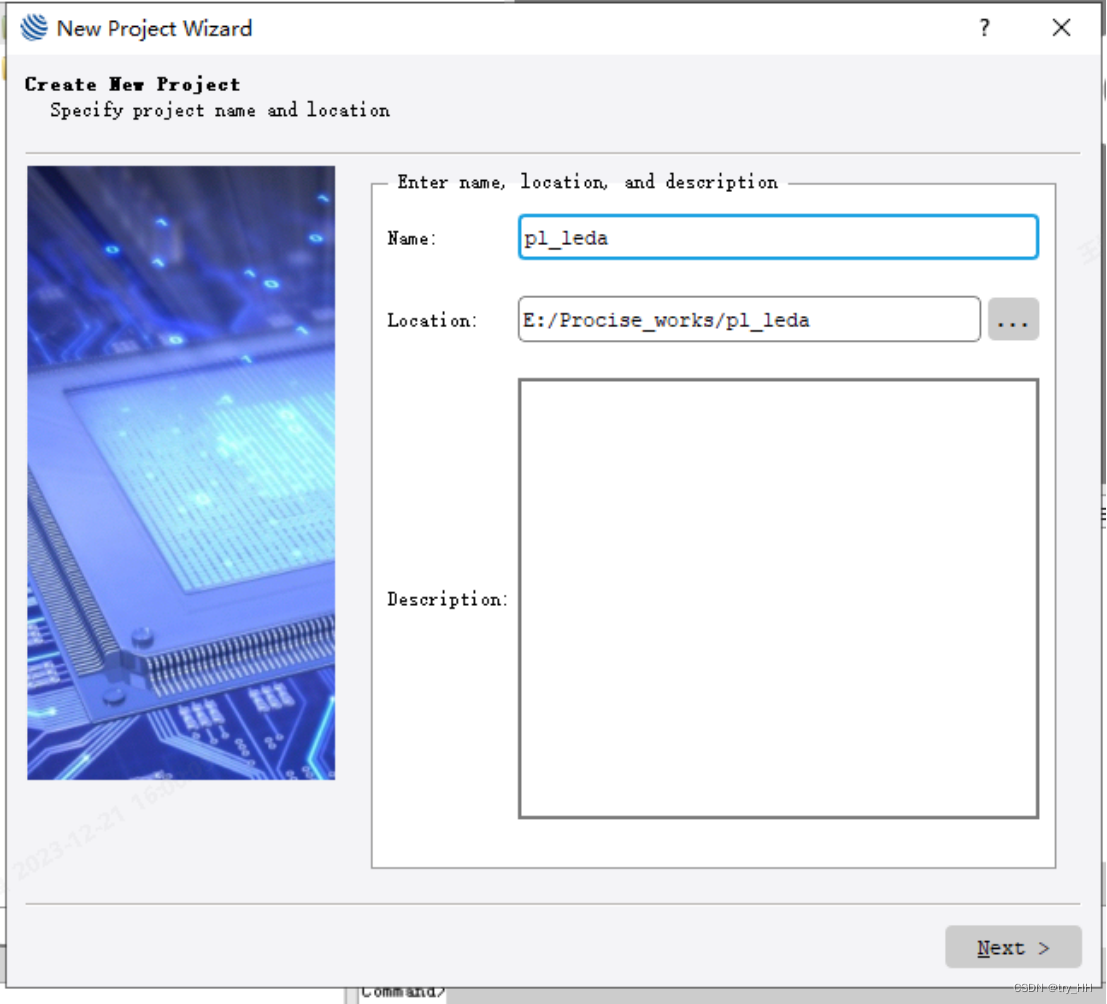

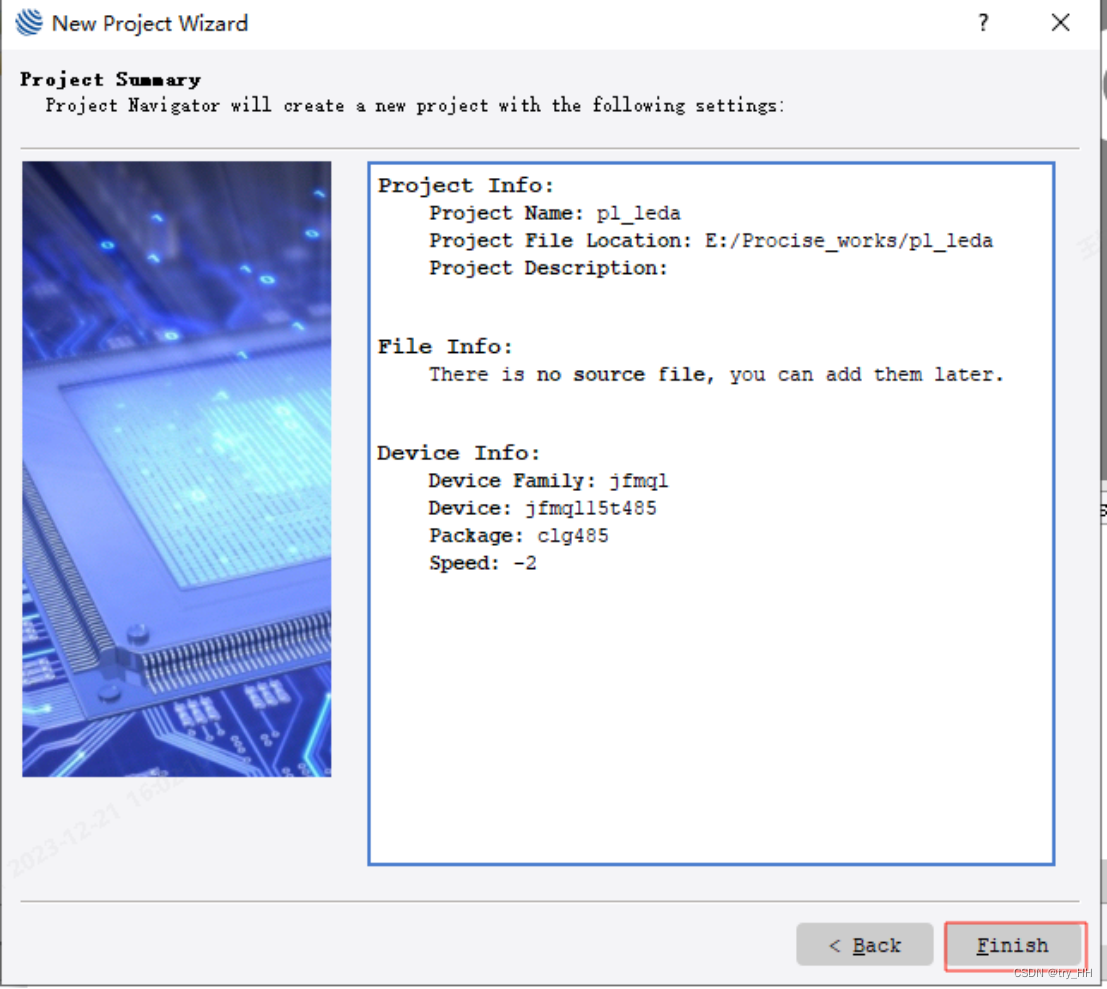

二、新建procise工程

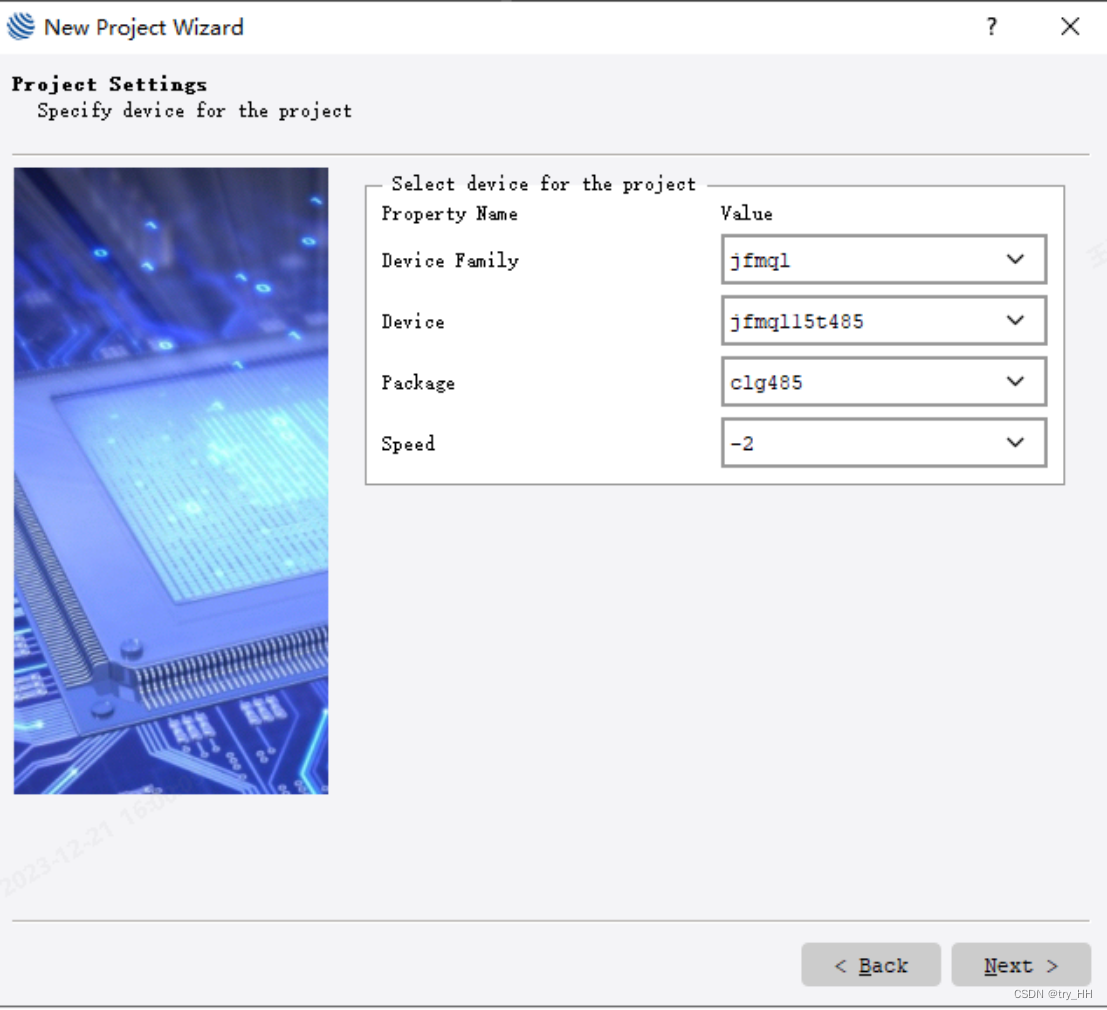

三、选择对应的Device

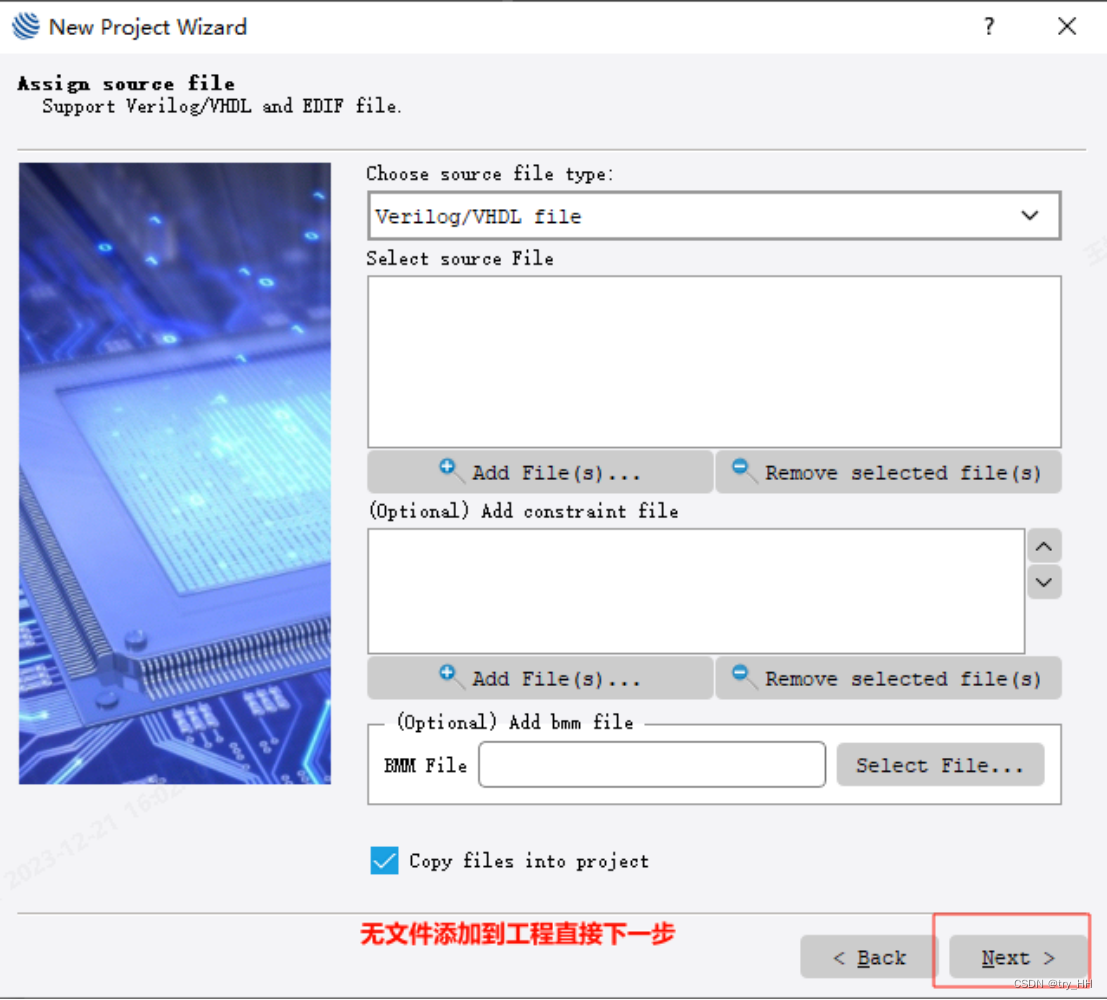

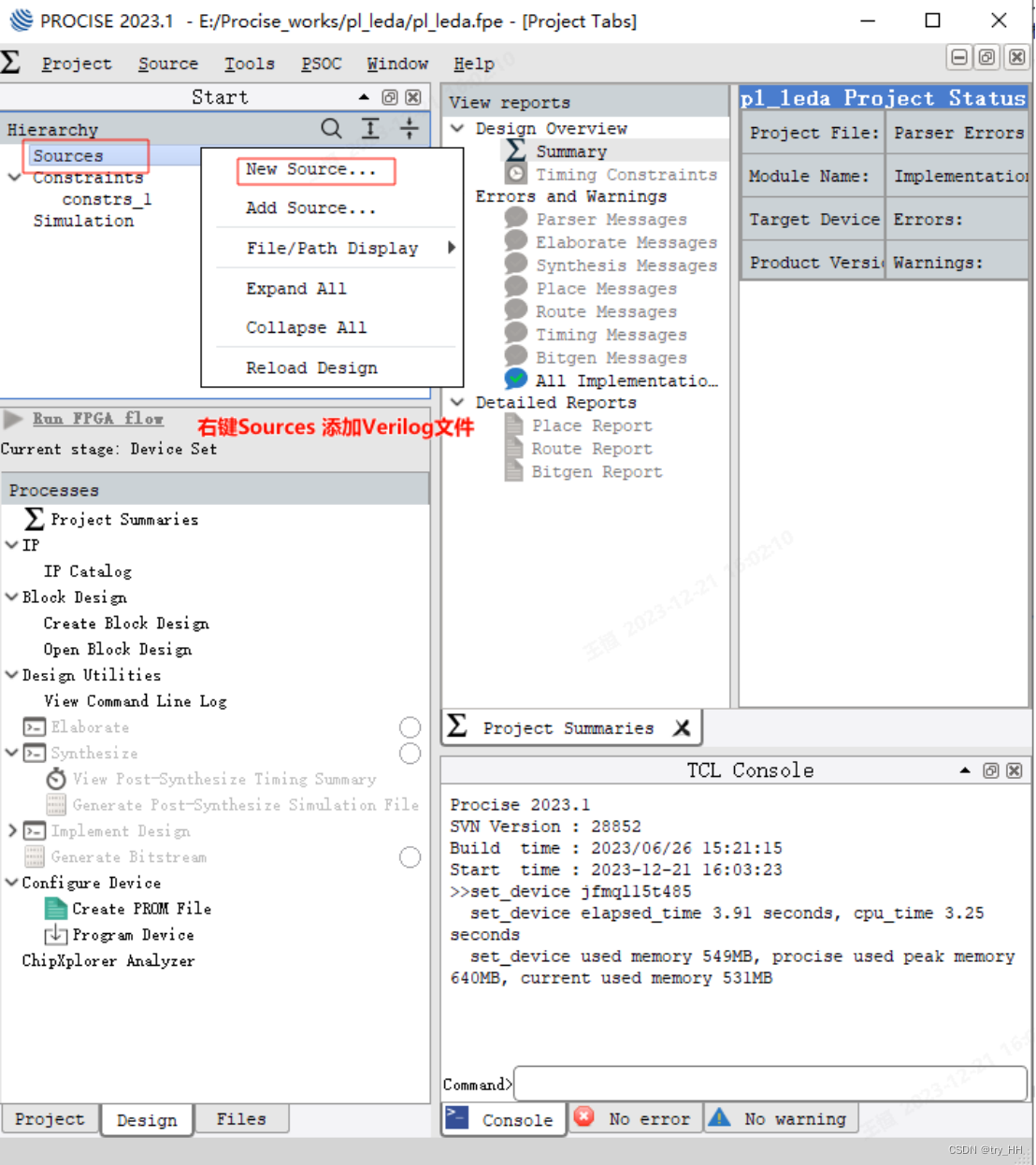

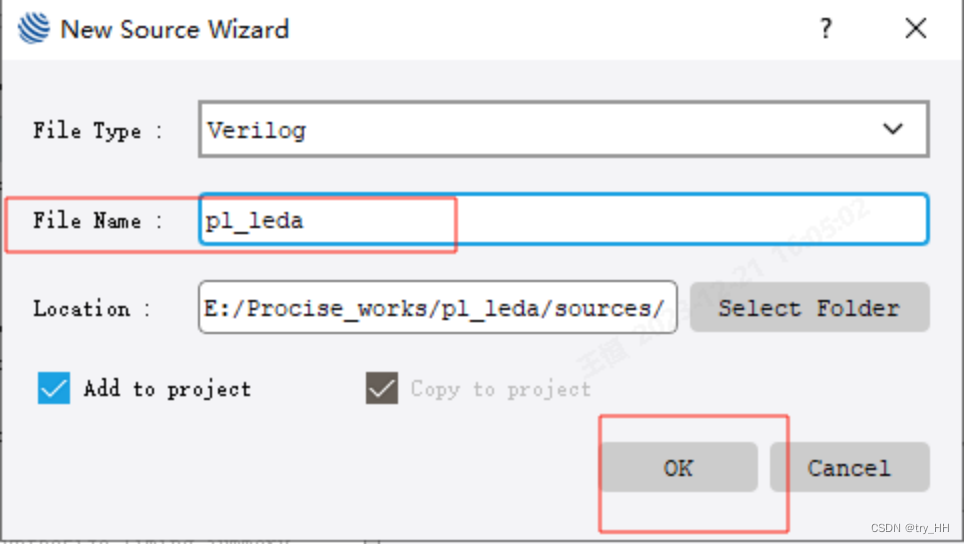

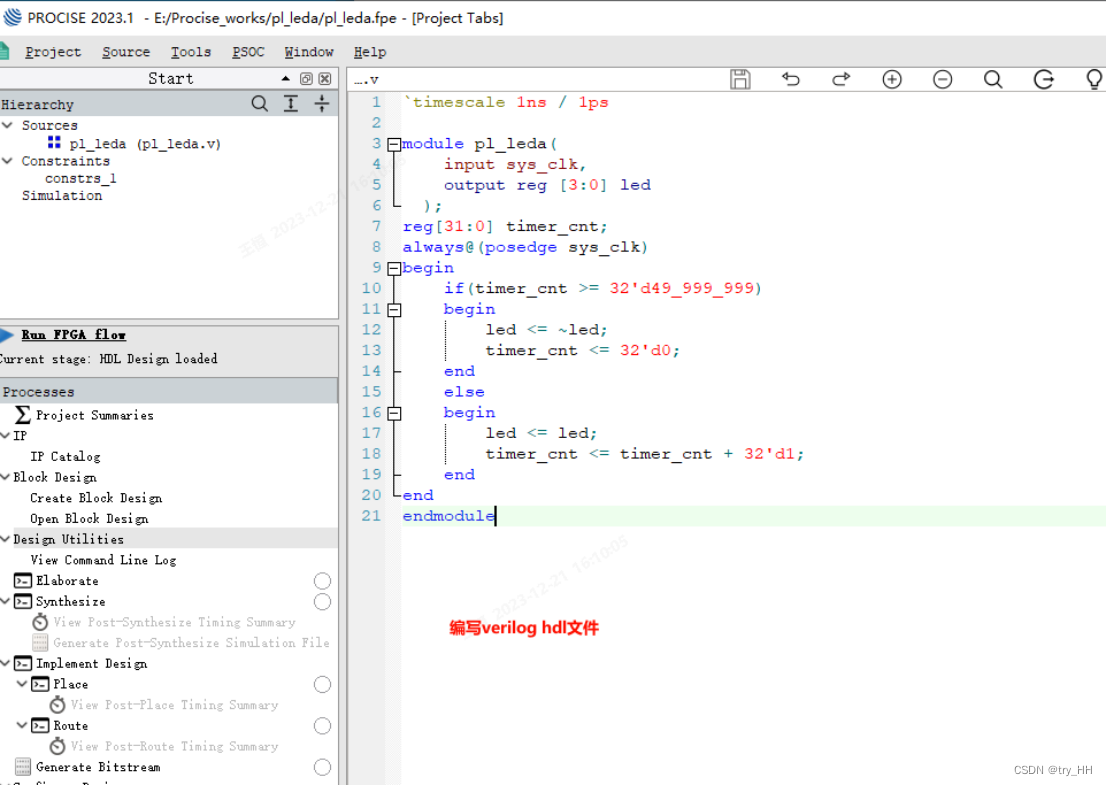

四、添加source Verilog文件

`timescale 1ns / 1ps

module pl_leda(

input sys_clk,

output reg [3:0] led

);

reg[31:0] timer_cnt;

always@(posedge sys_clk)

begin

if(timer_cnt >= 32’d49_999_999)

begin

led <= ~led;

timer_cnt <= 32’d0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32’d1;

end

end

endmodule

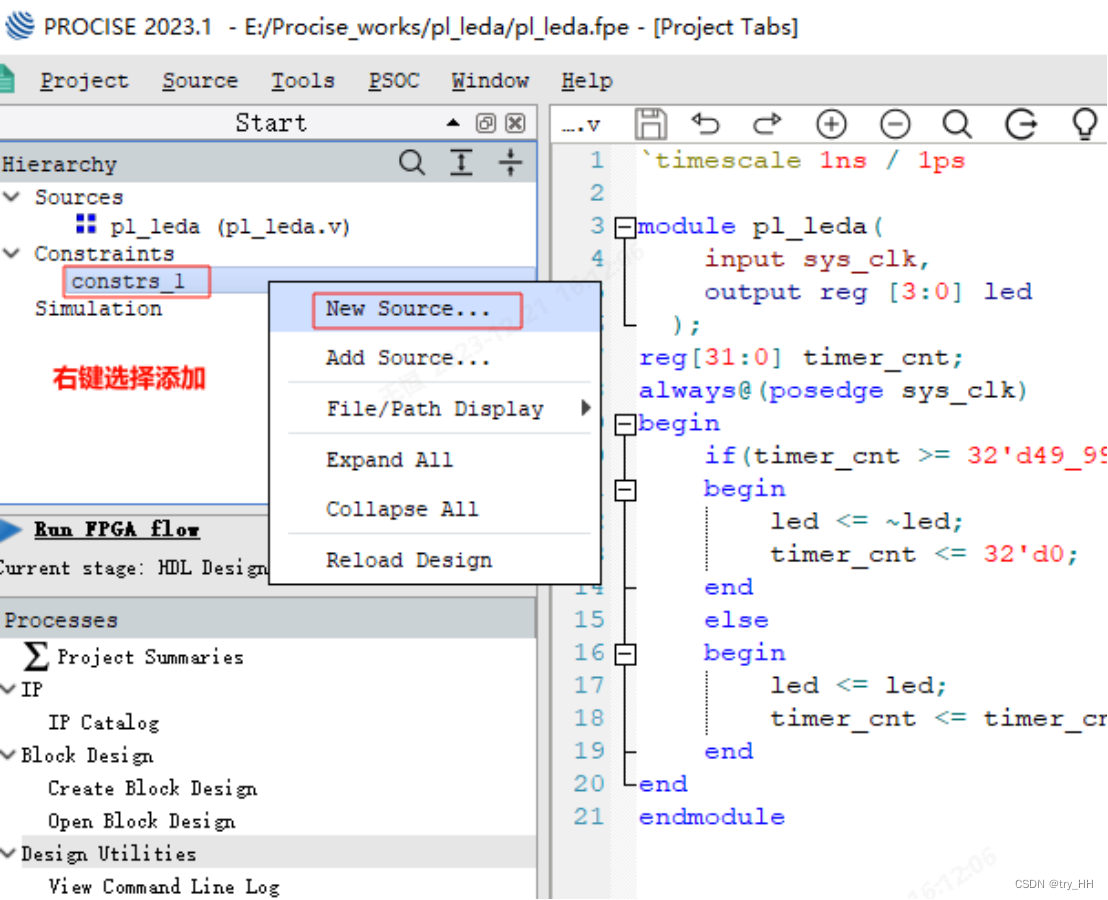

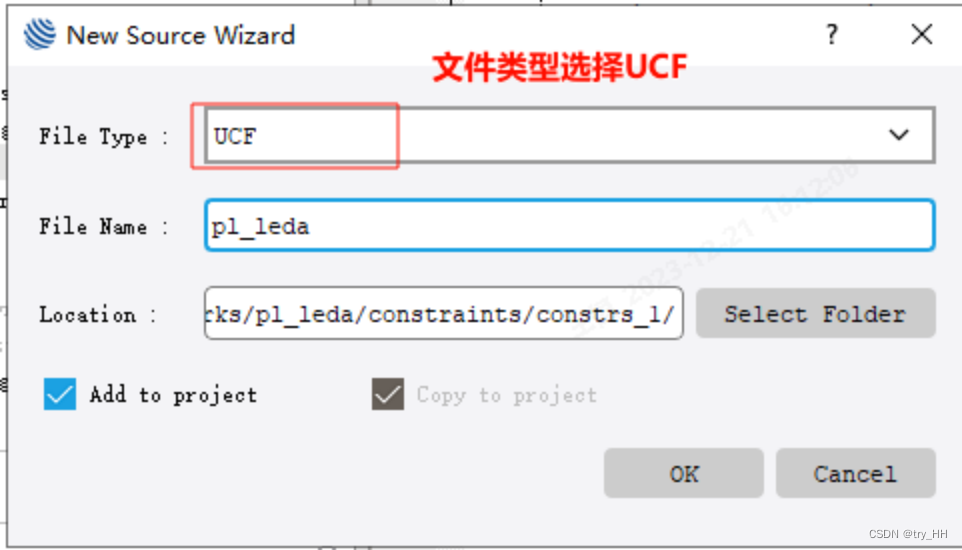

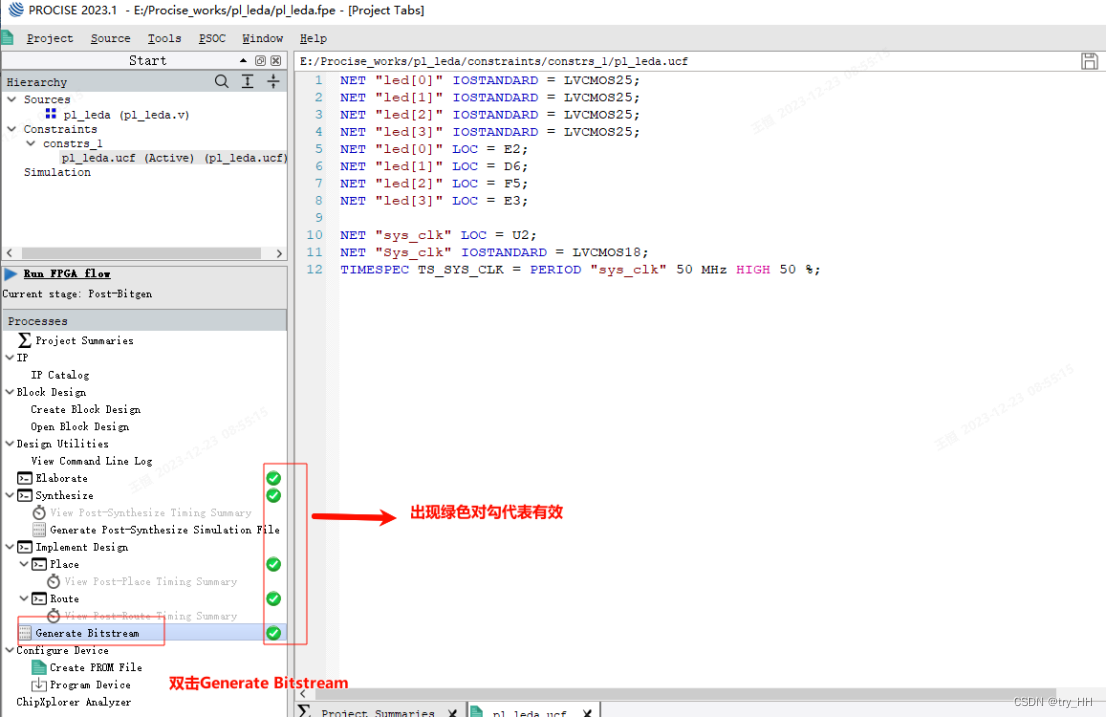

五、添加约束文件

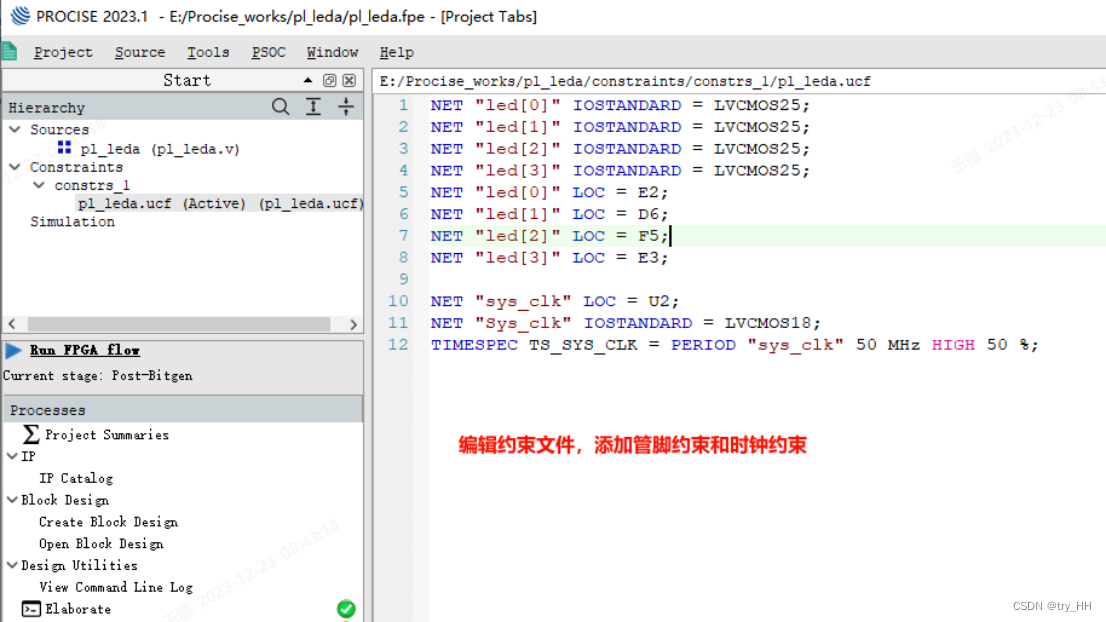

编辑约束文件,添加管脚约束和时钟约束

NET “led[0]” IOSTANDARD = LVCMOS25;

NET “led[1]” IOSTANDARD = LVCMOS25;

NET “led[2]” IOSTANDARD = LVCMOS25;

NET “led[3]” IOSTANDARD = LVCMOS25;

NET “led[0]” LOC = E2;

NET “led[1]” LOC = D6;

NET “led[2]” LOC = F5;

NET “led[3]” LOC = E3;

NET “sys_clk” LOC = U2;

NET “Sys_clk” IOSTANDARD = LVCMOS18;

TIMESPEC TS_SYS_CLK = PERIOD “sys_clk” 50 MHz HIGH 50 %;

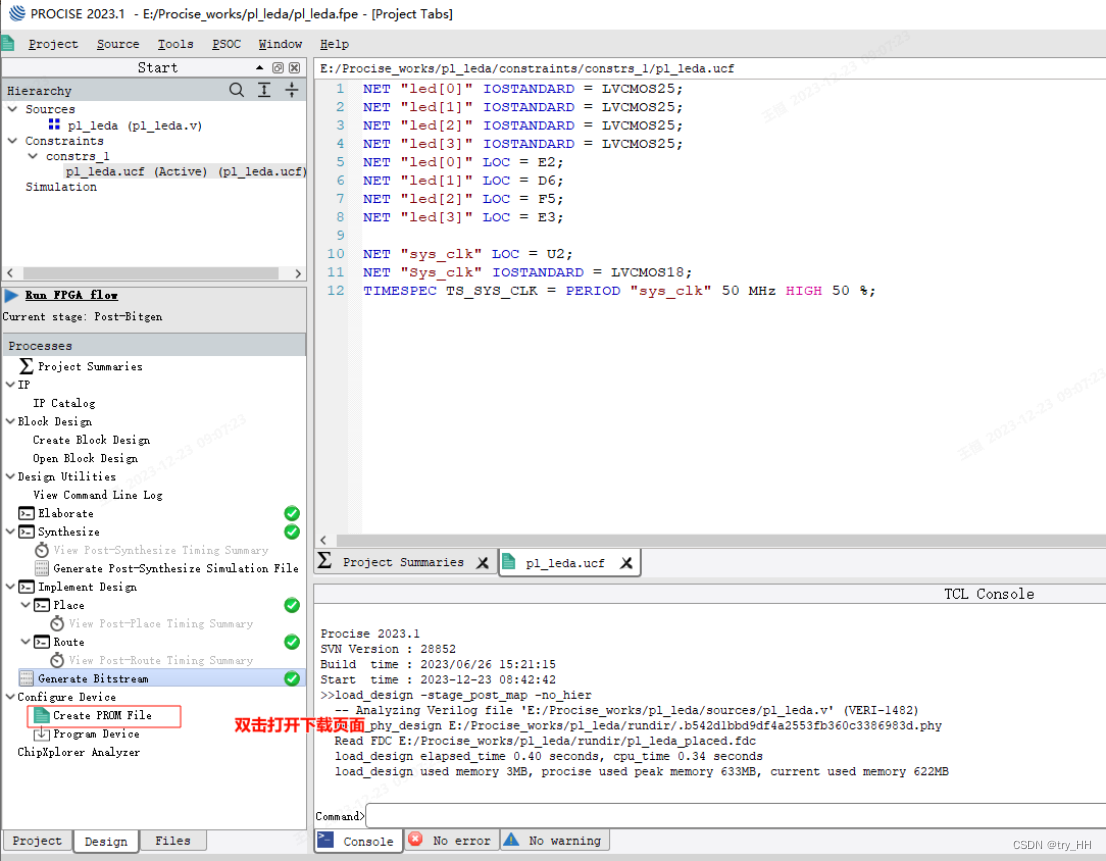

六、生成bitstream文件

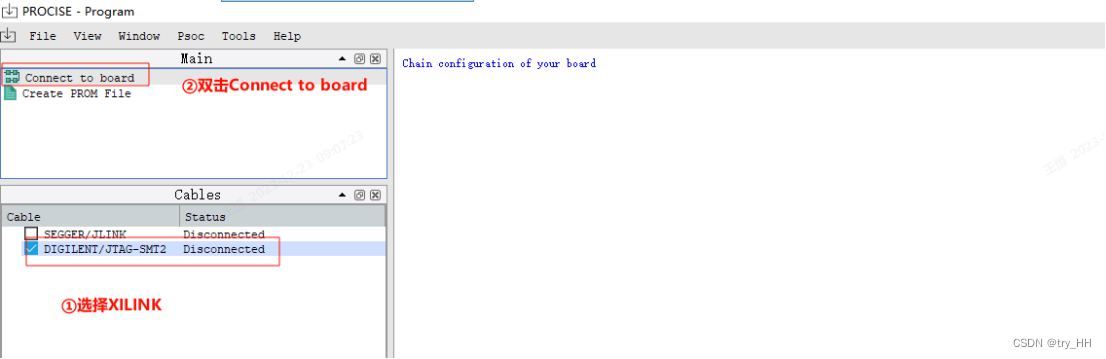

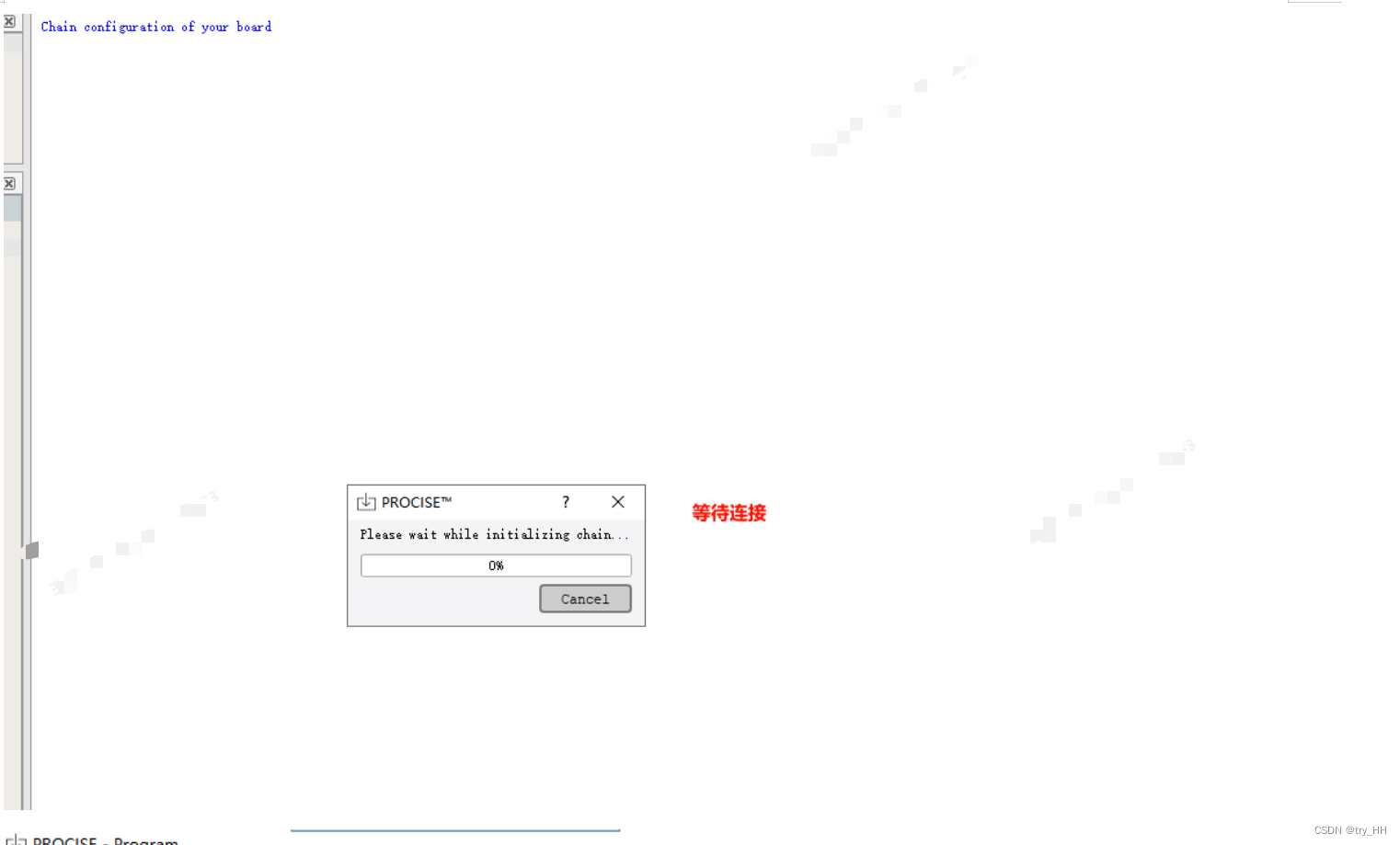

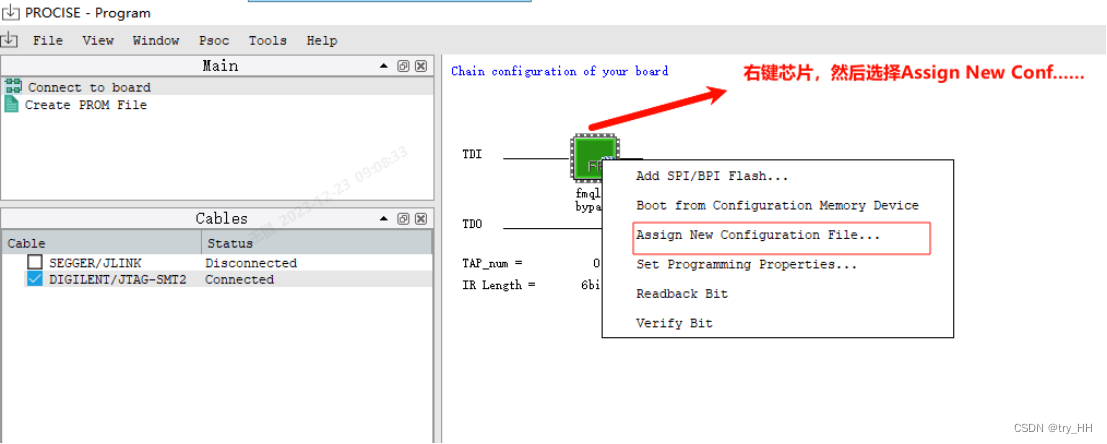

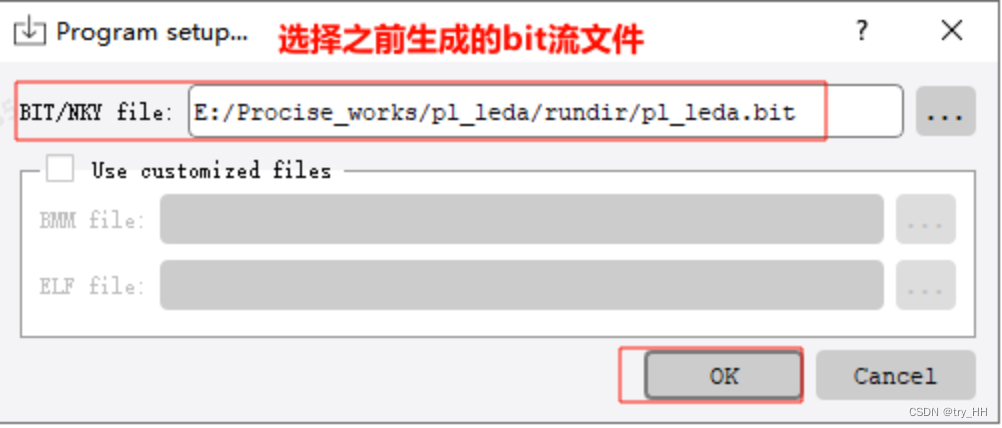

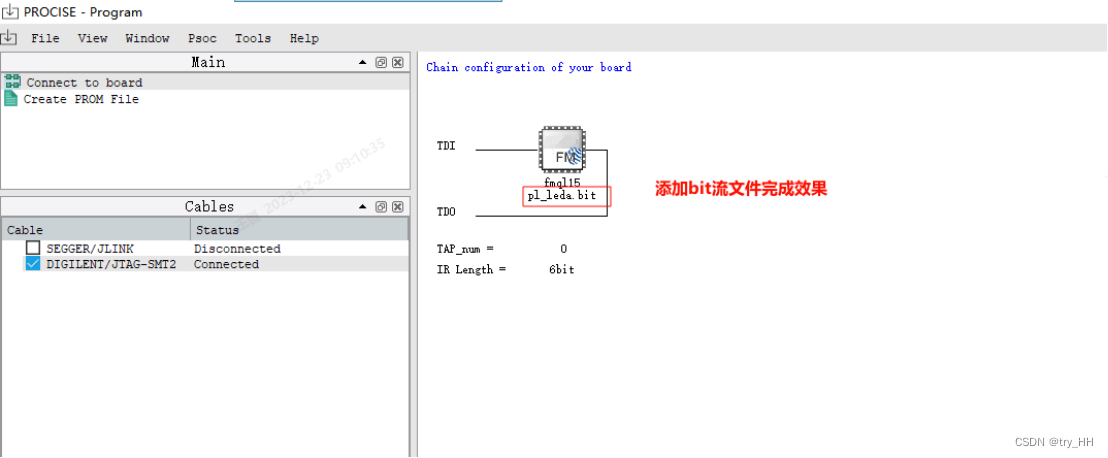

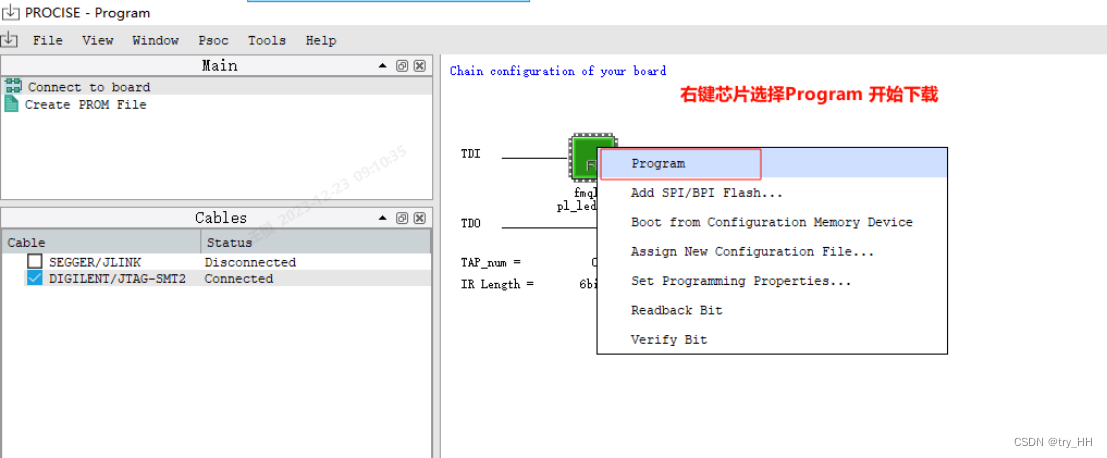

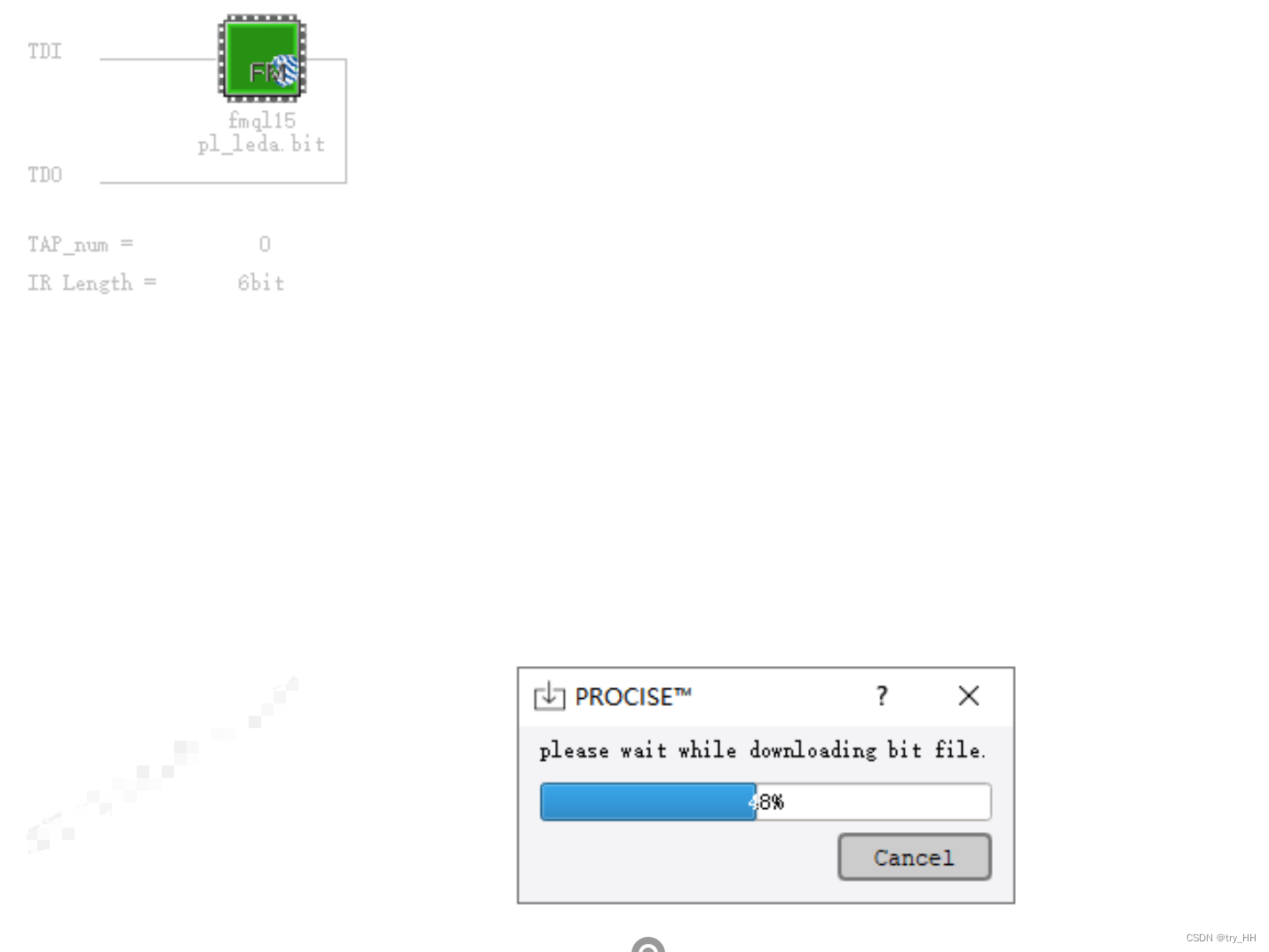

七、下载调试

本文详细介绍了如何使用Procise工具创建一个JFMQL15T纯PL工程,涉及添加sourceVerilog文件、配置时钟和LED管脚、编写约束文件以及生成并下载bitstream进行LED闪烁的调试过程。

本文详细介绍了如何使用Procise工具创建一个JFMQL15T纯PL工程,涉及添加sourceVerilog文件、配置时钟和LED管脚、编写约束文件以及生成并下载bitstream进行LED闪烁的调试过程。

8863

8863

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?