平台有很多的代码,如基本配置的代码、实例化对象的代码、端口链接的代码。显然,我们需要先实例化对象,在连接端口实现平台可以正常的工作,因此UVM引出phase机制,实现平台各个phase有序进行。那么各个phase的执行顺序是怎么样的呢?

本文主要解决2个问题:

1.Phase机制的作用,以及各个phase 机制之间的运行关系:

2. 如何确保不同组件之间相同phase 的开启和关闭

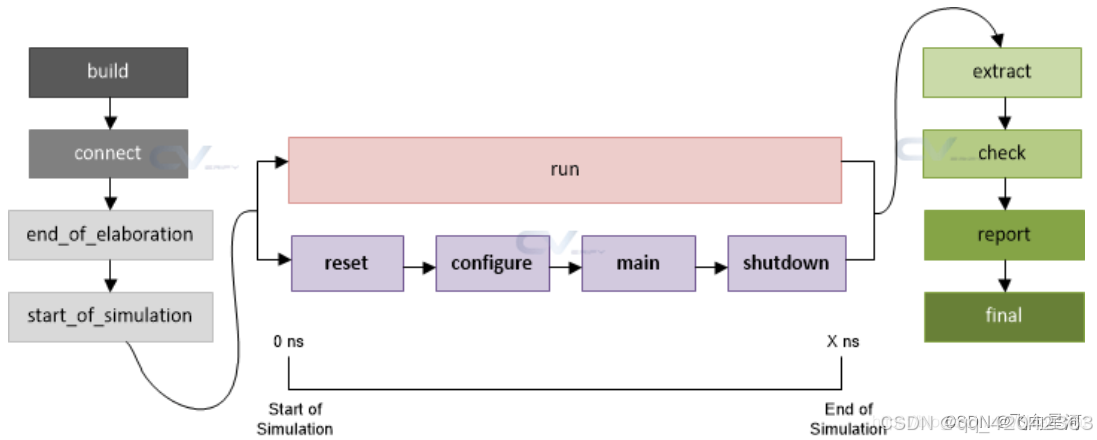

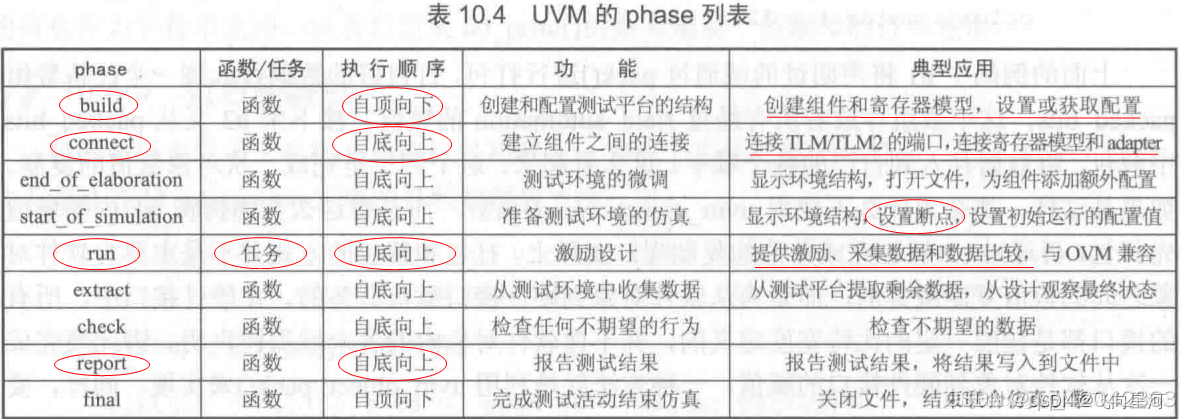

phase机制存在的意义在于:传统的硬件设计模型在仿真开始之前就已经完成了例化和连接,而SV的软件部分对象例化则在仿真开始之后执行。在SV中对象例化通过new()来实现,但是简单的new无法解决的一个重要问题就是验证环境在实现层次化时如何保证例化的先后关系,以及各个组件在例化之后的连接。此外,如果要实现高级功能,例如在顶层到底层的配置时,SV也无法在底层组件例化之前完成对底层的配置。所以,UVM在验证环境构建时引入了phase机制,通过该机制我们可以很清晰的将UVM仿真阶段层次化。这里的层次化,不仅仅是指各个phase的先后执行顺序,处于同一phase中的层次化组件之间的phase也有先后关系。

在定义了各个phase虚方法后,UVM环境会按照phase的顺序分别调用这些方法。首先来看phase主要分为哪些:

UVM利用objection机制来结束仿真

uvm中通过objection机制来控制phase的运行与结束,objection机制一般用于run_phase和sequence的控制,uvm会检查该phase中是否有objection被提起(raise_objection),如果有,那么等待这个objection被撤销(drop_objection)后结束该phase的运行

raise_phase和drop_phase都是成对出现的,raise_phase语句必须出现在run_phase中第一条消耗时间的语句之前,否则无法起作用

1812

1812

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?