表达式位宽规则

表达式位宽规则:包括自决定表达式和上下文决定表达式。

1、自决定表达式——所有操作数的位宽由自己决定;

2、上下文决定表达式——所有操作数的位宽由整个表达式上下文环境中最大的位宽决定。

仿真实例

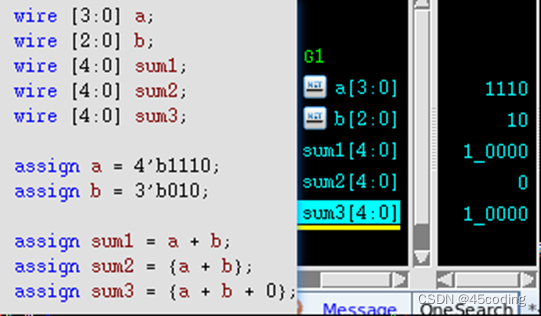

例1

①赋值(=、<=)和算数运算(+、-、*、/、%)操作符为上下文决定表达式,因此sum1 = a+b表达式中,由最大位宽的操作数即sum1的位宽来决定表达式位宽,a和b都零扩展为5bit(只有a和b均为有符号数时才会进行符号扩展),再进行运算和赋值.

②位拼接({}、{{}})操作符为自决定表达式,因此{}内部表达式的位宽由内部自决定,而{}内部的+运算是上下文决定表达式,那么b会零扩展至4bit与a进行相加,溢出的bit直接截断,再零扩展赋值给sum2.

③{}内部的+运算是上下文决定表达式,那么a、b都会零扩展至32bit(没有声明位宽的0默认为32位)与a进行相加,结果不会溢出,最终截断赋值给sum2.

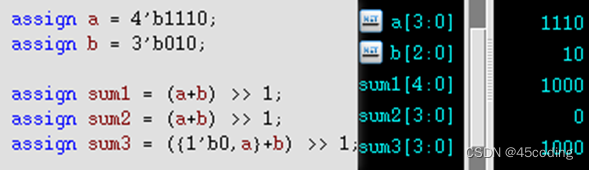

例2

移位操作符为混合决定表达式,左侧操作数为上下文决定,右侧操作数(移位因子)为自决定。

①sum1定义为5bit,移位因子1为自决定,不会加入上下文环境中, a、b以5bit进行相加运算,不会溢出,移位之后得到结果5’b01000;

②sum2定义为4bit,a、b以4bit进行相加运算,溢出的bit位直接截断,加法结果为0,移位之后结果仍然是0;

③sum3虽然也定义为4bit,但自决定式的位拼接{}操作符内部为5bit,位拼接后的结果就会以5bit与b进行相加运算,不会溢出,移位之后得到结果5’b01000。

结论

1、 Verilog 编码规范:

① 不同位宽进行运算时,应先将低位宽的变量扩展为相同位宽;

② 表达式中的常数前应加上位宽,避免warning和资源浪费。

2、 总结操作符的表达式位宽规则如下:

| 操作符 | 位宽决定于 | 备注 |

|---|---|---|

| 赋值=、<= | 上下文决定 | 赋值操作符右边均为有符号数才会做符号扩展 |

| 算术运算+、-、*、/、% | 上下文决定 | |

| 条件运算?: | 混合决定 | 第一个操作数(条件)为自决定,第二、三个操作数为上下文决定 |

| 算数幂运算** | 混合决定 | 第一个操作数(底)由上下文决定,第二个操作数(指数)为自决定 |

| 一元运算&、|、^ | 自决定 | 结果是一个自决定的、无符号数的、1bit值 |

| 位运算~、&、|、^ | 上下文决定 | |

| 移位运算<<、>>、<<<、>>> | 混合决定 | 左侧操作数为上下文决定,右侧操作数(移位因子)为自决定 |

| 一元逻辑运算!、二元逻辑运算&&、|| | 自决定 | 结果是一个自决定的、无符号数的、1bit值 |

| 比较运算 ==、!=、<=、…… | 自决定 | 结果是一个自决定的、无符号数的、1bit值 |

| 位拼接{}、{{}} | 自决定 | 结果为无符号数 |

| 位选择[]、[:]、[+:]、[-:] | 自决定 | 结果为无符号数 |

5269

5269

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?