FPGA时序分析与约束(1)

本文中时序分析使用的平台: quartusⅡ13.0

芯片厂家:Inter

1、什么是时序分析?

在FPGA中,数据和时钟传输路径是由相应的EDA软件通过针对特定器件的布局布线得到的,因此,时序分析即是通过分析FPGA设计中各个寄存器之间的数据和时钟传输路径,来分析数据和时钟延迟之间的关系。一个设计稳定的系统,必然能够保证整个系统中所有的寄存器都能够正确的寄存数据。

2、时序约束的作用?

时序分析即是通过相应的EDA软件告知EDA软件在对数据和时钟进行时设计应该达到怎样的时序指标,然后EDA软件会根据时序约束的各个参数,尽力优化布局布线,以达到该约束指标。协助EDA软件分析设计的时序路径,以产生相应的时序报告。

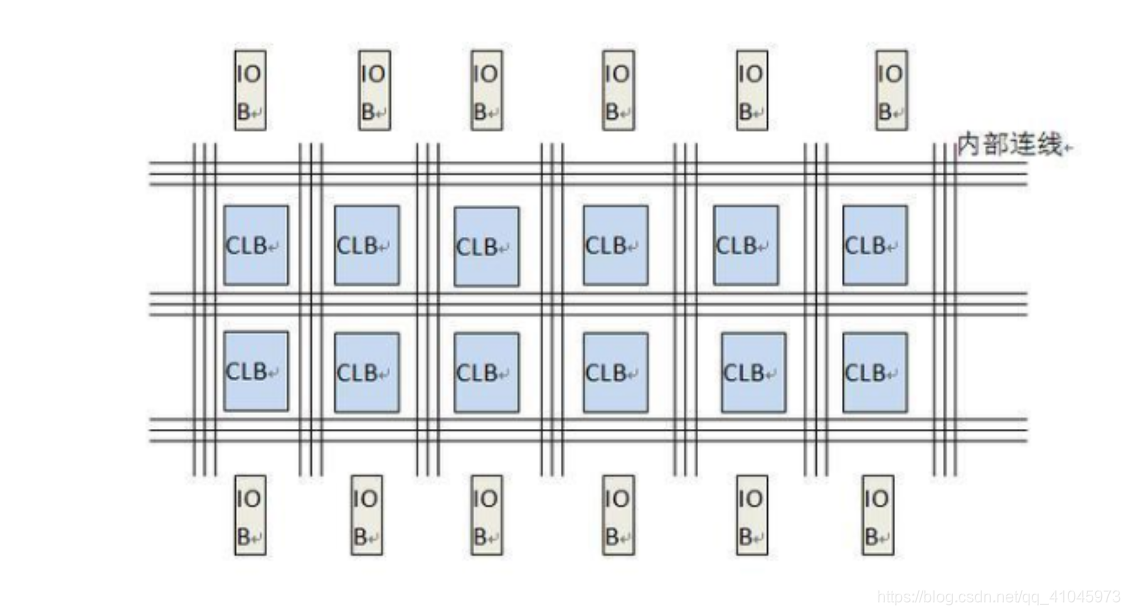

3、FPGA组成三要素?

可编程逻辑功能块(LogicElement)、片内互连线、输入输出块(IOBs,I/O blocks)。

可编程逻辑块(LE)的组成:由LUT(查找表)和DFF(D触发器)组成,LUT实现逻辑功能,DFF实现纯粹的打拍。若查找表和D触发器都使用,则可以实现时序逻辑。

LE的单元内部结构:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?