点击蓝字关注我们

关注、星标公众号,精彩内容每日送达

来源:网络素材一、为什么要进行时序分析和时序约束

PCB通过导线将具有相关电气特性的信号相连接,这些电气信号在PCB上进行走线传输时会产生一定的传播延时。

而FPGA内部也有着非常丰富的可配置的布线资源,能够让位于不同位置的逻辑资源块、时钟处理单元、BLOCK RAM、DSP和接口模块等资源能够相互通信,完成所需功能。

FPGA的布线同PCB的走线一样,也会由于走线的长短不同而产生或大或小的传输延时(走线延时)。FPGA信号经过逻辑门电路进行各种运算也会产生延时(逻辑延时)。那么多个信号从FPGA的一端输入,经过一定的逻辑门电路处理后从FPGA的另一端输出,如何保证各个信号的延时一致呢?这个时候就需要进行时序分析,从而进行时序约束,从而保证FPGA的信号能够相互协同正常工作。

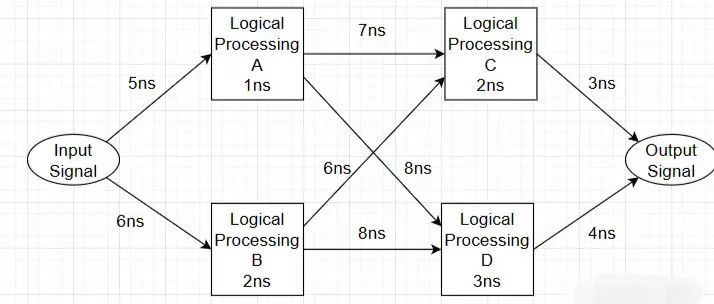

假设有一个信号输入FPGA中,在FPGA内部经过一些逻辑处理,最后进行输出,那么这些走线和处理都需要时间(走线延时和逻辑延时)。例如下图,输入信号到达逻辑处理A需要5ns,进行处理需要1ns,然后到逻辑处理C需要7ns,进行处理需要2ns,最后达到输出需要3ns,这条路径是所有路径中耗时最短的。但是FPGA不知道这条路径耗时最短,如果不对其进行时序约束,很可能会随便选一条路径进行布线,此时如果对系统的延时有要求,就可能出现信号错乱的情况。

二、什么是时序分析和时序约束

FPGA的时序分析与约束需要设计者根据实际的系统功能,通过时序约束的方式提出时序要求;FPGA编译工具根据设计者的时序要求,进行布局布线;编译完成后,FPGA编译工具还需要针对布局布线的结果,套用特定的时序模型,给出最终的时序分析和报告;设计者通过查看时序报告,确认布局布线后的时序结果是否满足设计要求。

因此时序分析就是遍历电路存在的所有时序路径,计算信号在这些路径上的传播延时,使用特定的时序模型,针对特定的电路进行分析系统时序是否满足要求。

时序约束就是对设计的电路提出时序上的要求,一般来说其可以细分为内部时钟约束 、IO口时序约束、偏移约束、静态路径约束和例外路径约束等。

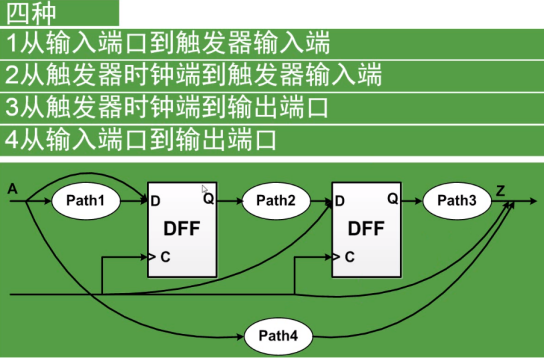

三、时序约束的基本路径

FPGA 时序约束所覆盖的时序路径主要有4种:

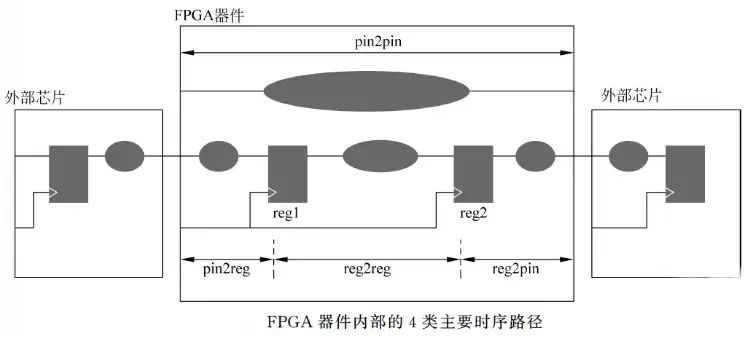

1.FPGA内部寄存器之间的时序路径,即reg2reg;

2.输人引脚到FPGA内部寄存器的时序路径,即pin2reg;

3.FPGA内部寄存器到输出引脚的时序路径,即reg2pin;

4.输入引脚到输出引脚之间的时序路径(不通过寄存器),即pin2pin。

其中reg2reg、pin2reg、reg2pin都和寄存器有关,需要进行时序约束,因为要确保数据信号在时钟锁存沿的建立时间和保持时间内稳定;但pin2pin本质就是纯组合逻辑电路,一般直接约束延时范围,因为pin2pin路径的信号传输通常不通过时钟。

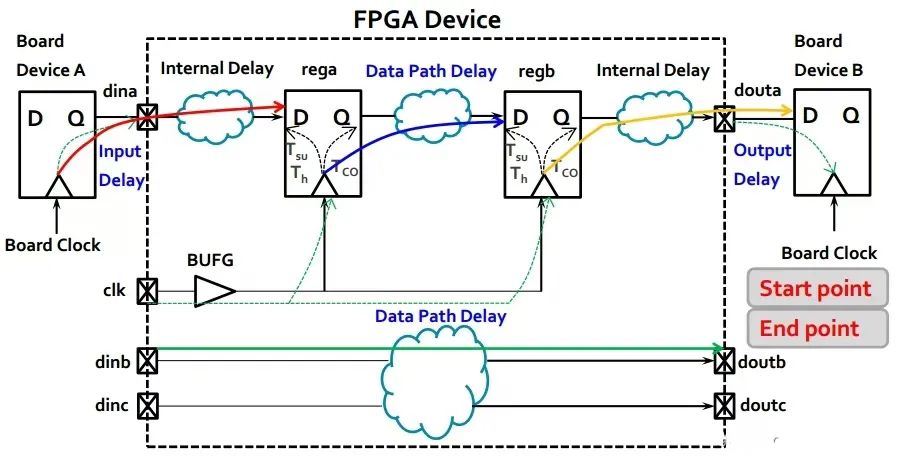

在4种时序路径中,

pin2reg需要经过3个延迟,例如Device A到rega需要经过Tco(寄存器输出延时,即寄存器内部的传输时间)、Input Delay(输入走线延迟)、Internal Delay(FPGA内部走线延迟);

reg2reg需要经过2个延迟,例如rega到regb需要经过Tco、Data Path Delay(数据路径延时);

reg2pin需要经过3个延迟,例如regb到Device B需要经过Tco、Internal Delay、Output Delay(输出走线延迟);

pin2pin需要经过1个延迟,例如dinb到doutb需要经过Data Path Delay。

四、时序分析与约束相关面试题

1、什么是建立时间和保持时间?

建立时间:指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间。如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器

保持时间:是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间。如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。

(setup time不受系统时钟频率影响)

2、为什么D触发器要满足建立时间和保持时间?

因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,D触发器将进入亚稳态,亚稳态的值也并不一定是你的输入值,亚稳态传播到后面逻辑中,可能导致整个系统奔溃。

3、如何修复建立时间和保持时间

修复Tsetup

(1)降低时钟频率;

(2)增大时钟正偏斜;

(3)减小时钟负偏斜;

(4)减少组合逻辑延迟;

(5)减少多扇出网络;

(6)选用延时少的cell

修复Thold

(1)减小时钟正偏斜;

(2)增大时钟负偏斜;

(3)增加组合逻辑延迟

4、什么是流水线?

流水线使用存储器件将时钟周期内关键路径(最大组合延迟的路径)分割开来,从而减少关键路径上各个阶段延迟并使电路能以更高的频率工作。

5、什么是流水线冒险?

冒险有结构冒险、数据冒险和控制冒险三种。解决通用办法是在流水线中插入流水线气泡直至冒险消除。

结构冒险:由于资源冲突而使硬件无法支持所有可能的指令组合同时执行。例如在单端口存储器执行读写操作过程,假设流水线要求同一时钟周期 内要对存储器进行访问两次,这样的话就会产生存储器读写冲突。这种情况可以再增加一个时钟周期,即将流水线停止一个周期(产生一个流水线气泡)。另一种方法就是使用不同的存储器或者多端口存储器,消耗更多的资源。(采用使能信号推迟时钟,使得流出流水线气泡时间)

数据冒险:指令执行需要之前指令的计算结果,而这个结果在流水线中还没有计算出来。解决办法就是使用数据/寄存器转移,进行纵向气泡延迟,从而解决问题。

控制冒险:分支的流水线和其他指令改变程序计数器的值。由于分支所需的数值需要后续的计算流水才可以 产生 ,这是我们需要将流水停止几个周期知道从重新获取下一条数值进行判断,使风险降低到最小。

其他风险:数据读取访问存储器时,地址要保持不变等等。

6、什么是关键路径?如何减小?

关键路径,即组合逻辑中延时最长的时序路径。

减小方法:

(1)优化组合逻辑代码;

(2)综合时选择延时小的单元;

(3)综合时使用set_max_delay等优化指令;

7、如何提高系统运行速度?

(1)提高系统时钟频率(前提是减少组合逻辑延时);

(2)流水线设计,例如组合逻辑中间插入流水寄存器,长路径切为短路径;

(3)并行处理,即硬件复制,并行运行,以面积换性能;

8、阐述系统最快时钟频率和流水线设计思想

同步电路的速度是指同步系统时钟的速度,同步时钟越快,电路处理数据的时间间隔越短,电路在单位时间内处理的数据量就越大。时钟的延迟必须大于Tco+Tdata+Tsetup,也就是说最小的时钟周期Tmin=Tco+Tdata+Tsetup,即最快的时钟频率是Fmax = 1/Tmin。FPGA开发软件也是通过这种方法来计算系统的最高运行速度Fmax。因为Tco和Tsetup是由具体的器件工艺决定的,故设计电路时只能改变组合逻辑的延迟时间Tdelay,所以说缩短触发器间组合逻辑的延时时间是提高同步电路速度的关键所在。

流水线设计:将原本一个时钟周期完成的较大的组合逻辑通过合理的切割后分由多个时钟周期完成,采用流水线技术插入触发器后用多个时钟周期完成,该部分逻辑运行的时钟频率会有明显的提升,用面积换速度提高系统的性能。

9、为什么说时钟越快,时序越容易违规?为什么工艺越高,时钟就可以跑得越快?

寄存器的延时参数大小是固定的,而时钟越快,时钟的长度就越短,保持裕量和建立裕量就越短,当时钟快到一个周期的长度还没一个寄存器延时参数大的程度时,就没有保持裕量和建立裕量的空间了。而工艺越高就会导致寄存器延时参数越小,体积越小也会导致寄存器之间的路径延时越小。

10、时序约束的基本概念和基本策略?

时序约束主要包括周期约束,偏移约束,静态时序约束。

通过附加时序约束可以综合布线工具调整映射和布局布线,使设计达到时序要求。

附加时序约束的一般策略是先附加全局约束,然后对快速和慢速例外路径附加专门约束,首先定义设计的所有时钟,对各时钟域内的同步元件进行分组,对分组附加时序偏移约束,对全组合逻辑的 PAD to PAD 路径附加约束。附加专门约束时,首先约束分组之间的路径,然后约束快慢速例外路径和周期路径,以及其他特殊路径。

11、时序约束有哪几种路径

(1)Input paths:外部引脚到内部模块路径

(2)Register-to-register paths:系统内部寄存器到寄存器路径

(3)output paths:内部模块到外部引脚的路径

(4)port to port paths:FPGA输入端口到输出端口路径(不常用,无锁存不好分析)

12、附加约束的作用

(1)提高设计的工作频率(减少了逻辑和布线延时);

(2)获得正确的时序分析报告;

(3)指定FPGA/CPLD的电器标准和引脚位置;

13、为什么说阻塞赋值和非阻塞赋值最好不要混用?为什么说if嵌套不要太多?

这属于同一个问题。阻塞赋值和if判断都是即时得到结果的,他们属于组合逻辑,他们造成的延时效果和寄存器延时效果是一样的,所以时序逻辑中如果阻塞赋值用的多或是if嵌套太多、判断时间太长,就会导致延时。如果时钟太快了,就可能导致时序违规。

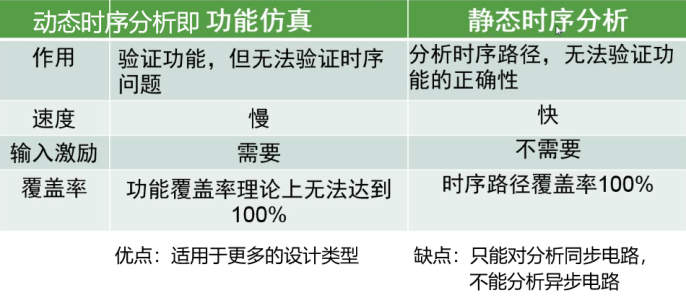

14、简述静态/动态时序模拟的区别?

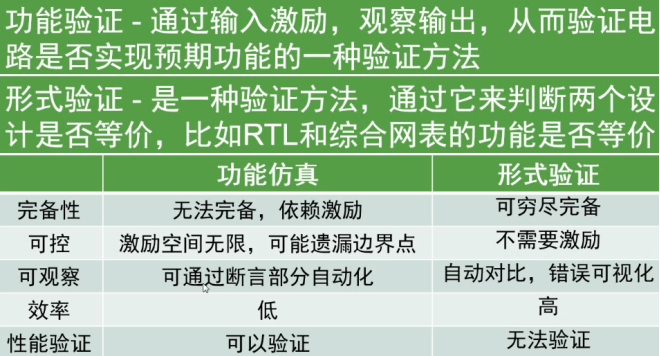

15、形式验证和功能验证的区别?

16、简述什么是fanout,以及他对时序的影响。

在数字电路中,逻辑门相互连接组成更加复杂的电路,所以大多数逻辑门的输出端都连接着多个别的单元的输入。所以需要一个术语来描述逻辑门的驱动能力的大小,也就是扇出 Fan-out。最大扇出数maximum fan-out定义为一个逻辑门驱动的同类逻辑门的最大数。

17、名词解释:时序仿真

(1)功能仿真(前仿真)

功能仿真是指在一个设计中,在设计实现前对所创建的逻辑进行验证其功能是否正确的过程。布局布线以前的仿真都称作功能仿真,他包括综合前仿真和综合后仿真。综合前仿真主要针对基于原理框图的设计;综合后仿真既适合原理图的设计,也适合基于HDL语言的设计。

(2)时序仿真(后仿真)

使用布局布线后器件给出的模块和连线的延时信息,在最坏的情况下对电路的行为作出实际的估计。时序仿真使用的仿真器和功能仿真使用的仿真器是相同的,所需要的流程和激励也是相同的;唯一的差别是时序仿真加载到仿真器的设计包括基于实际布局布线的最坏情况的延时,并且在仿真结果波形中,时序仿真后的信号加载了延时,而功能仿真没有。

18、在静态时序分析中计算时钟延迟需要考虑一下哪些因素?(BCD)

A. 寄存器的建立和保持时间

B. 工艺特性造成的on-chipvariation

C. 时钟源的抖动(jitter)

D. 时钟树不平衡引入的偏差(skew)

E. 系统时钟干扰

19、以下关于电路处理说法正确的是:(A)

A:同步电路系统中可以有一个时钟及其三分频时钟进行驱动;

B:DFF的setup时间是根据DFF和DFF之间的时序路径分析出来的,把时钟变慢可以增加DFF的setup时间

C:数字电路设计中是竞争和冒险会带来电路上的毛刺,需要加入RC滤波电路清除

D:如果DFF的hold时间不满足,通常可以通过时钟运行速度来解决

E:异步reset信号因为和时钟是异步的,因此不需要加时钟约束

解答:B setup时间是.lib/.db库里面的内容,是DFF器件的属性;C边沿触发器D输入端对于毛刺不敏感,只需要满足setup/hold time,不需要专门加滤波器;D Thold计算与时钟无关Thold< Tcq+Tcom;E类似于setup 和hold。异步信号有remove和recovery time check

20、按照通信系统仿真抽象方法,调制仿真位于()

A、系统级仿真的上层 B、链路级仿真的上层 C、链路级仿真的下层 D、链路级仿真之上与系统级仿真支架的层次

21、以下说法错误的有(BC)

A、如果DFF的Hold时间不满足,通常可以通过增加数据路径延时来解决

B、如果DFF的Setup时间不满足,通常可以通过增加数据路径延时来解决

C、如果DFF的Hold时间不满足,通常可以通过增加DFF时钟路径延时来解决

D、如果DFF的Setup时间不满足,通常可以通过增加DFF时钟路径延时来解决

解析:个人理解时钟延时是时钟路径延时是Tskew,数据路径延时是Tdata这条线。

22、FPGA在布局布线过程中,为了让系统满足时序要求对时钟采用约束?

错误。约束过后才布局布线的吧。

23、下列哪些约束属于时钟约束(A)

A、set_multicycle path B、set_false path C、set_max_delay D、set_input_delay

解析:常用的约束(1)create_clock对时钟的约束(2)set_false path时序例外

(3)set_input_delay/set_output_delay对IO的约束

24、利用verilog HDL语言描述的加法器和乘法器在功能仿真时关于延时说法正确的是( A )

A、无延时

B、有延时

C、不确定是否有延时

D、无法功能仿真

25、关于约束作用的描述中,正确的是(ABD)

A、提高设计的工作频率

B、获得正确的时序分析报告

C、静态时序分析工具以约束作为判断时序是否满足设计要求的标准

D、指定FPGA/CPLD的电气标准和引脚位置

E、缩短编译时间

26、关于建立setup和保持hold时间的表述哪些是正确?(AC)

A:解决setup time violation的方法之一是适当降低时钟频率

B:解决hold time violation的方法之一是适当降低时钟频率

C:setup time 不受系统时钟频率影响

D:setup time 是指有效的时钟沿来临之后的数据需要保持的时间

解析:B:holdup时间与时钟频率无关与时钟抖动和组合逻辑延时有关

D:setup time 是指有效的时钟沿来临之前的数据需要保持的时间

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?