分类

- 按逻辑功能不同分为:RS触发器、D触发器、JK触发器、T触发器。

- 按触发方式不同分为:电平触发器、边沿触发器和脉冲触发器。

- 按电路结构不同分为:基本RS触发器和钟控触发器。

- 按存储数据原理不同分为:静态触发器和动态触发器。

- 按构成触发器的基本器件不同分为:双极型触发器和MOS型触发器。

存储元件:锁存器

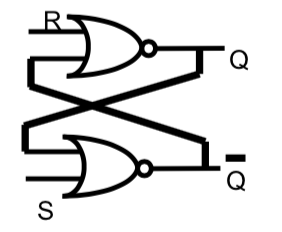

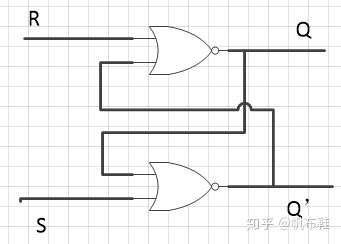

SR 锁存器(RS 锁存器)

进化历史

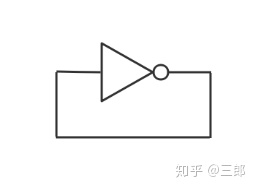

- 不稳定状态

- 稳定状态但是不可控

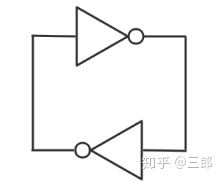

- 控制记忆状态

- 换个方向看看

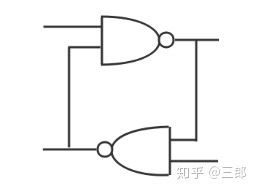

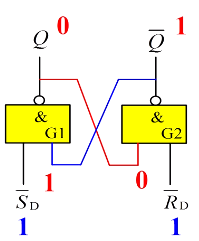

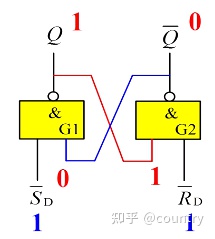

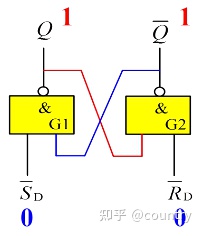

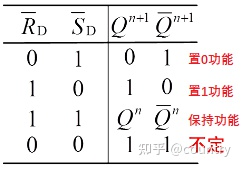

组合逻辑图

Bug:

D 锁存器

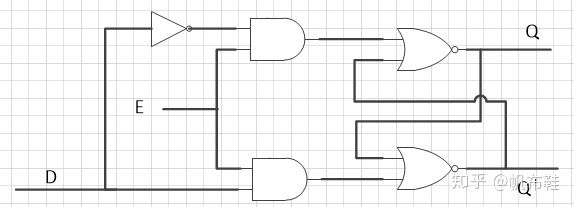

D锁存器(D Latch)完全是在SR锁存器的基础上发展得来的。

既然SR锁存器是可以通过调整输入,来得到两种固定的输出状态。但是它存在的问题是需要有两个输入,那么能不能将SR锁存器的功能使用仅一个输入来进行切换,我们只需加一个非门即可。

那现在的问题是,只要有输入S/R的状态(或者是D的状态),就会有输出状态的变化,无法区分到哪一种状态的变化是有用的,因此需要加入使能端,也就是 ENABLE端口。

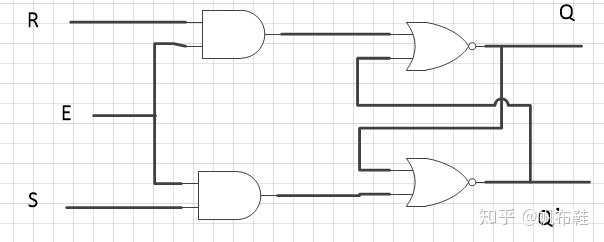

加入ENABLE的SR锁存器

加入ENABLE之后,从电路上可以很容易看出,想达到同之前的SR Latch一样的状态输出,必须要是E=1,那也就是说,可以认为设置ENABLE的状态,来确保该状态是否为有用的信息。

该电路可以使用74LS08(与门)+74LS02(或非门)来实现

加入ENABLE的D锁存器

这个电路就叫做D Latch,或者是叫做Data锁存器,它在计算机的内存和寄存器中是最基础的存储元件。这一个电路就可以存储1 bit的数据,并且是只有当E=1的情况下,才能够向计算机中写入数据。

1523

1523

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?