把断言bind到DUT上

module dut_sva_bind(input clk,input rst_n);

property cnt_jump_chk(clk, rst_n, input_cnt, boundary_value);

@(posedge clk) disable iff(!rst_n) (input_cnt >= boundary_value) |=> (input_cnt > 0);

endproperty

generate

for(genvar idx = 0; idx < 32; idx++) begin

assert property(cnt_jump_chk(clk, rst_n, top_tb.u_dut.u_xx_m.xx_id_cnt_0[idx], 4'hf));//不能定义assert名字

end

endgenerate

endmodule

//bind到dut上

bind `TOP_DUT dut_sva_bind dut_sva_bind_inst(.*);上面主要是提供一个module去写断言,在里面检查一些接口或dut内部的一些时序行为;

bind可以实现验证和设计的分离,将module/interface/program绑定到任意的设计模块或者其特定例化中,可以将interface直接bind到top module中进行例化。bind可以使得验证工程师不改动或最小的改动原有设计代码和文件结构,就能够实现对设计代码的检查。

SVA检验器通过关键字bind可以与设计中的任何模块(module)或者实例(instance)绑定。将SVA检验器可以与模块、模块的实例或者一个模块的多个实例进行bind绑定。实现绑定时,使用的是设计中的实际信号,语法如下:

bind <module_name or interface_name or instance_name> <checker_name> <checker_instance_name> <design_signals>;

这里注意以下几点:

[1] 通过bind语句将SVA的checker与设计模块绑定,等价于将SVA例化到设计模块中。

[2] bind不仅可以将断言与设计module绑定,也可以将任意两个模块之间进行绑定。

[3] bind功能可用于以下位置:module / interface;

实例:

bind:(在top层与DUT进行bind)

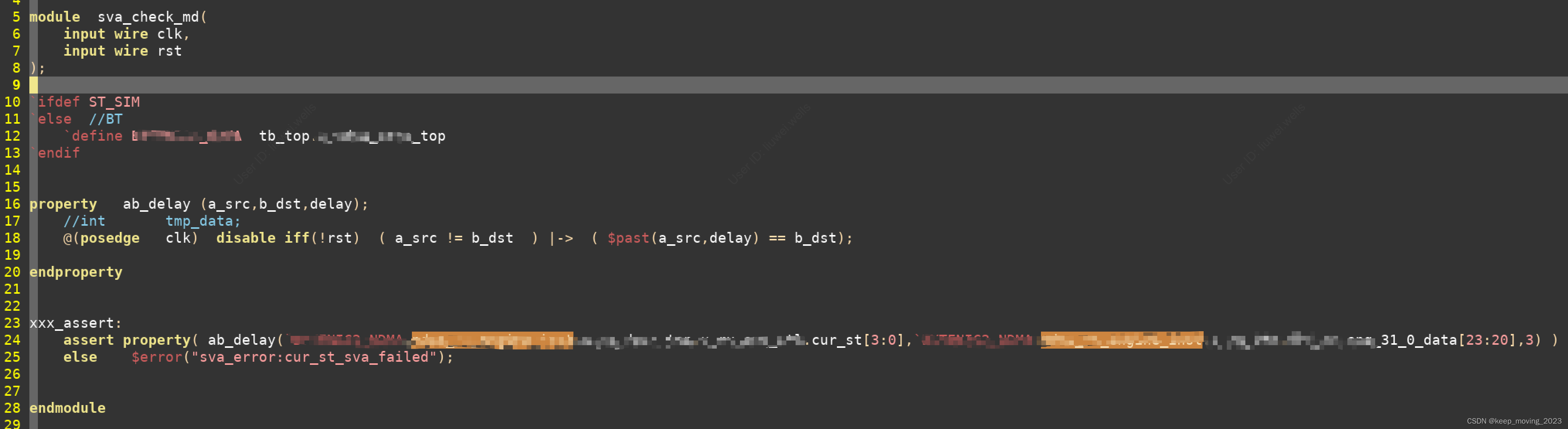

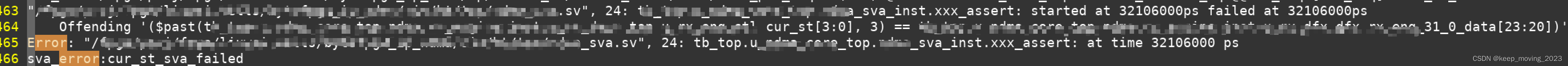

违例断言信息的打印:

断言开关控制:

assertoff(<level>, <scope1>[, <scope2> ...]);如果为 0,表示禁用当前作用域及其所有子作用域内的断言;如果为 1,表示只禁用当前作用域内的断言。还可以是2,向下递归一层(待验证)。

可以在top_tb module里面加一个initial块;

下面是中文输入法输入;linux里面自己手敲;

initial begin: assertion_ctrl

wait (rstn == 0)

$assertoff();

@(posedge rstn);

$asserton();

end只关闭某一个特定的断言:

指定断言的路径:下面这个是AI实例。实际在用例里面使用,可以生效,在特定用例里面只关掉一些特定的用例。

module single_assert_disable;

bit clk;

bit signal;

// 时钟生成

initial begin

clk = 0;

forever #5 clk = ~clk;

end

// 命名断言

my_assert: assert property (@(posedge clk) signal)

$display("Assertion passed");

else

$display("Assertion failed");

initial begin

#10;

// 禁用指定的断言

assertoff(1, single_assert_disable.my_assert);

#20;

// 重新启用断言

asserton(1, single_assert_disable.my_assert);

#20;

$finish;

end

endmodule

289

289

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?