1、查看某一个单比特信号的上升沿或下降沿的数目;

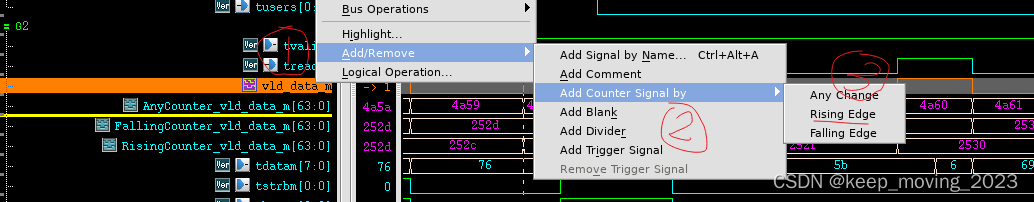

如下图所示步骤:

1)找到该信号右键,选择add/remove;

2)add couter signal by;

3)选择上升沿或下降沿或任意边沿;

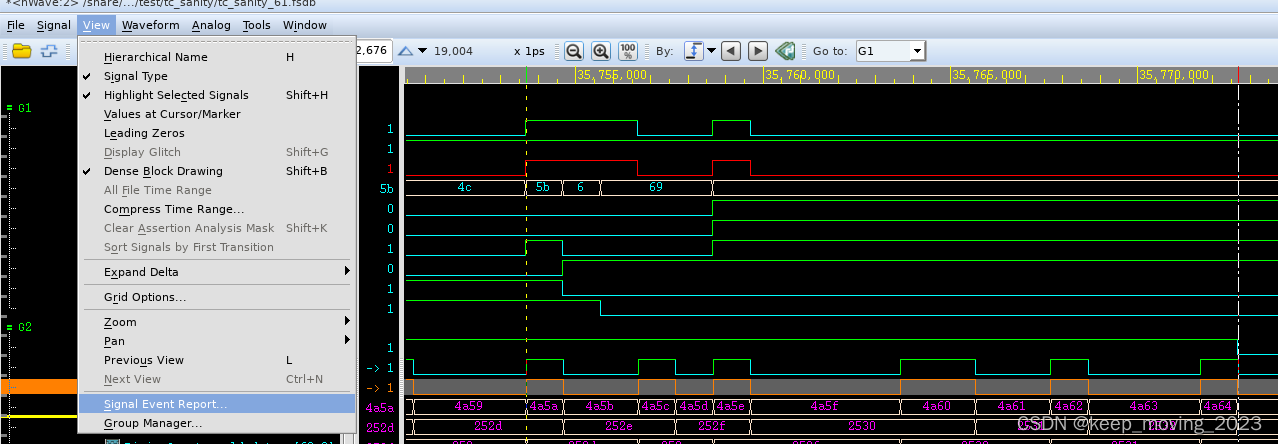

还有一种办法是:signal event 来看

1)选择要观察的信号,同时用黄白线选择要查看的区域;

2)view->signal_event_report;即可

上图结果如下:

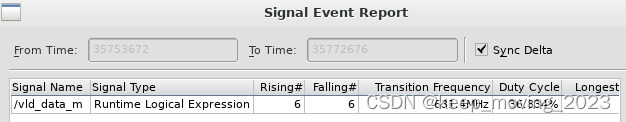

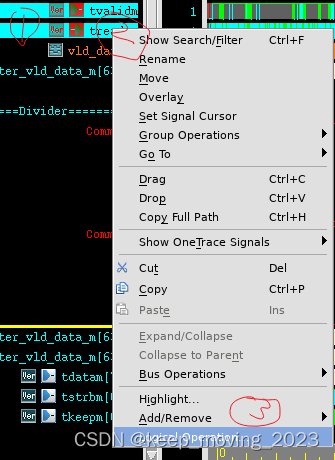

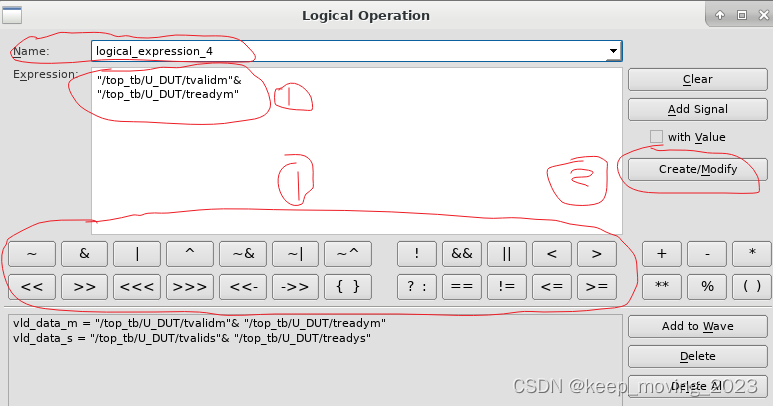

2、信号之间的逻辑操作;

1)选择要进行逻辑操作的信号;

2)右键->logical operation;

3)进入下面界面进行相关逻辑操作生成新的信号,如与或非等;

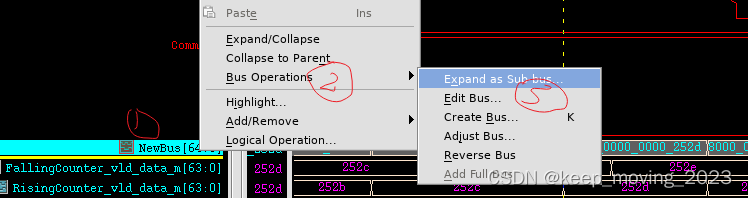

3、对多比特信号进行编辑或展开;

1)选中信号右键->bus operation->

expand as sub bus:可以把信号按固定间隔展开;

edit bus:可以只选则信号的一部分显示在波形上;

create bus:可以调整信号内各个bit之间的位置,也可以增加位宽等;

.......

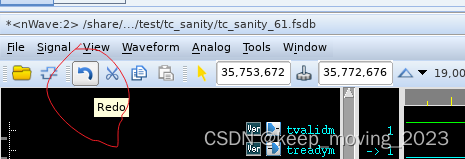

4、波形上的撤销;比如不小心展开了,点击它可以直接撤回去;

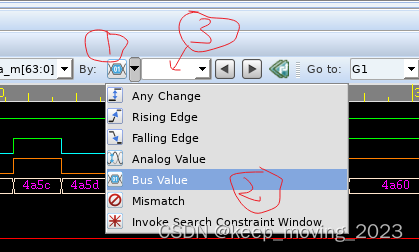

5、匹配信号中某一个值是否出现过;

先选中信号,再按下面图中顺序执行,左右三角形是指查找左侧匹配值和右侧匹配值;

6、常用快捷键;

显示信号路径层次:选中信号->按h键;

改变信号颜色:选中信号->按t键;

把代码的信号拉到波形上:方法1:鼠标选中直接拉过来;方法2:鼠标选中后,ctrl+w;(这种会拉到默认的那个波形上,如果开了多个可能不在当前这个窗口上)

波形重新跑了之后,reload波形:shift+l;

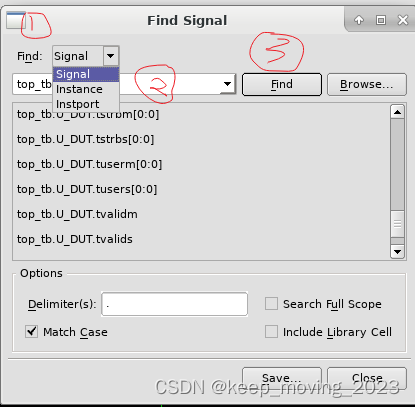

查找模块或task:shift+s;打开查找窗口如下图所示(可以使用通配符:*)输完后按一下enter键开始搜索,点go to可以直接到达该模块位置;

查找信号名/实例化模块等:shift+a;

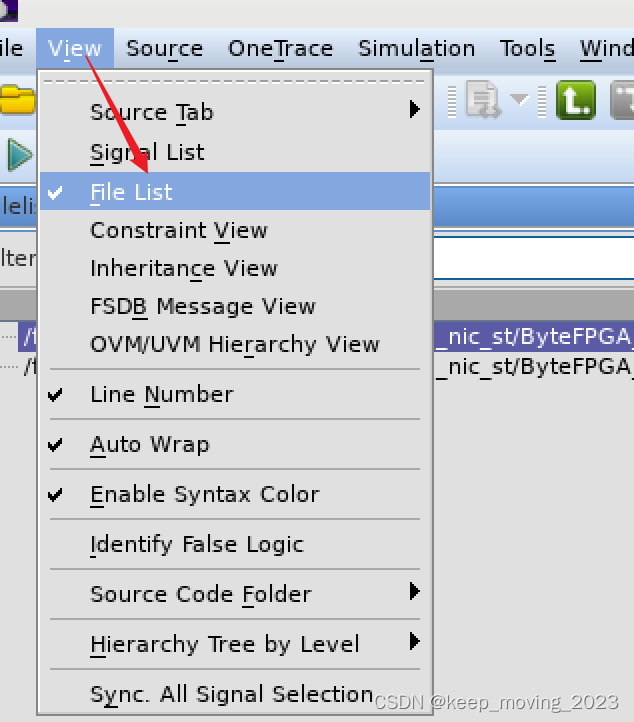

也可以通过:下图路径进入该界面;

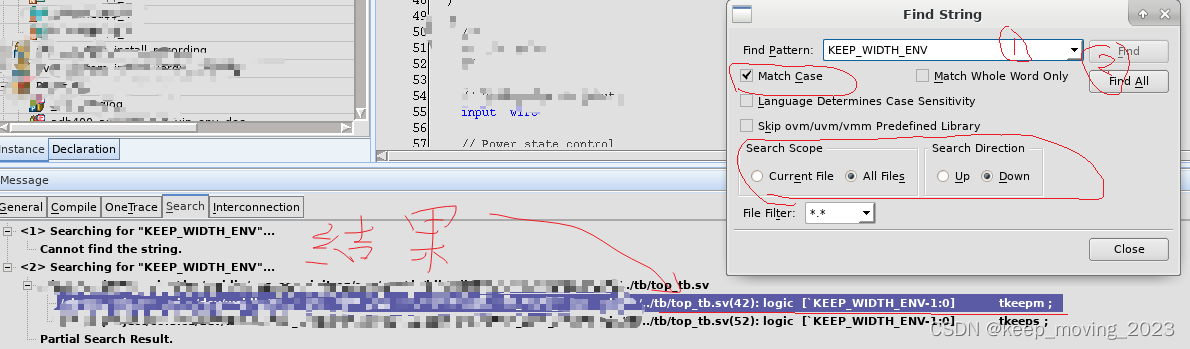

这里还可以进入查找特定字符串的窗口(注意查找的范围):

7、恢复回验证常用的窗口设置;

8,查看仿真波形的用例或组件的代码是不是最新修改后的代码:可以直接在搜索栏检索

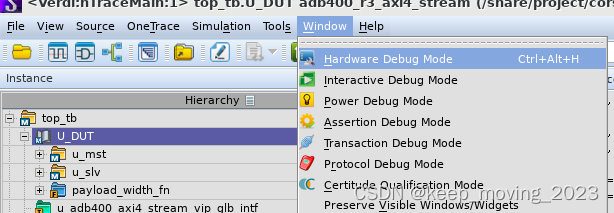

9,开启verdi的gui模式进行debug:仿真时加上:gui=on,完成编译后就会自动打开verdi进行仿真;

打开后在左下角的窗口可以直接输入:run 1000;enter后可以开始跑到对应时间点的仿真,或者遇到断点停下来;

可以使用单步仿真,一步步查看仿真路径;还可以区分DUT和TB两个仿真区域;

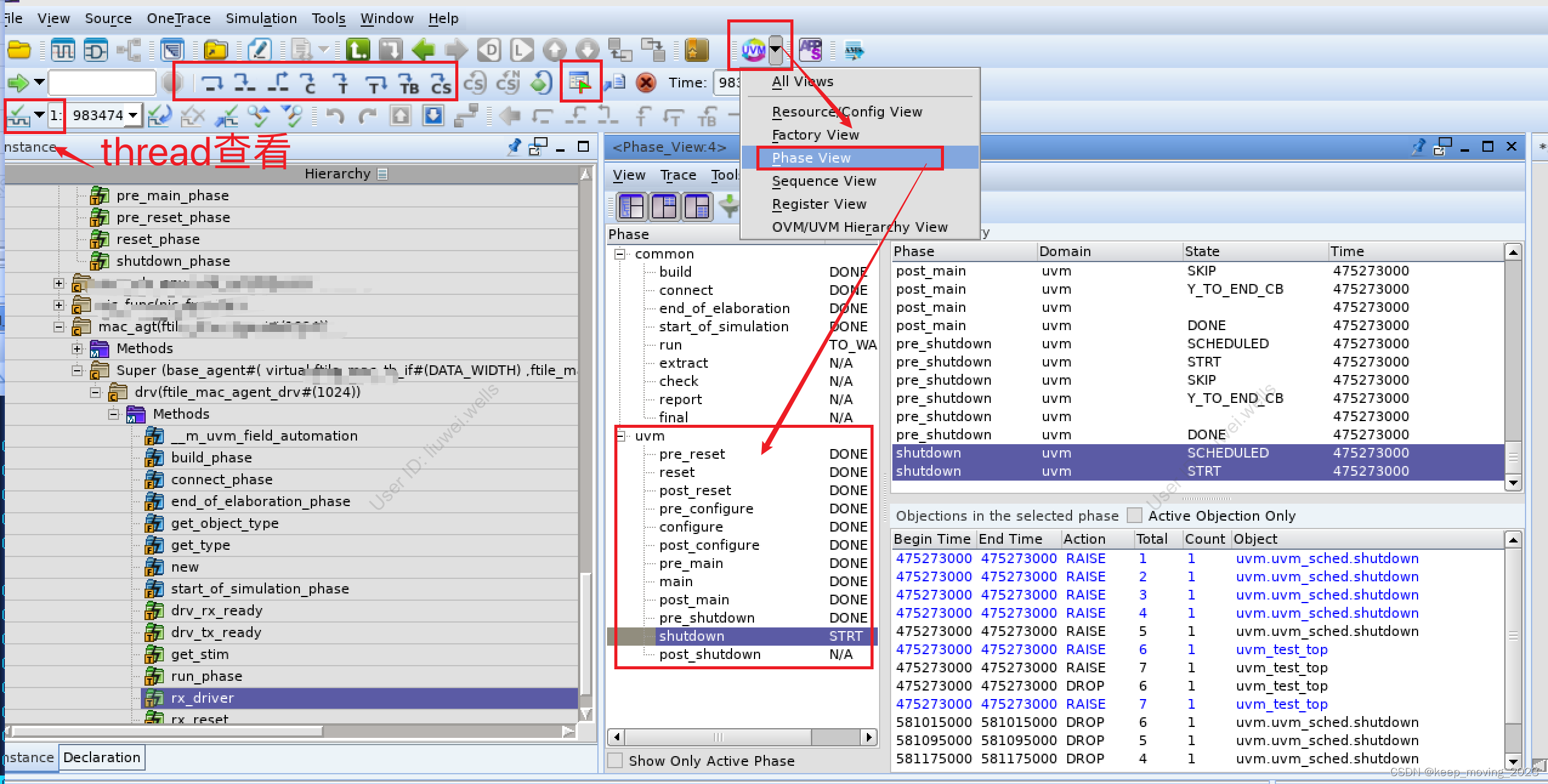

另外还有一些phase机制,可以查看哪些phase结束了;还有seq的激励是否正常发送和结束了;之前遇到了,main_phase结束后,seq里面的tr没有结束,然后shut_down phase又调用了一个seq去发送激励;导致仿真挂死在shutdown_phase了,因为main_phase的一个tr一直没有完成;

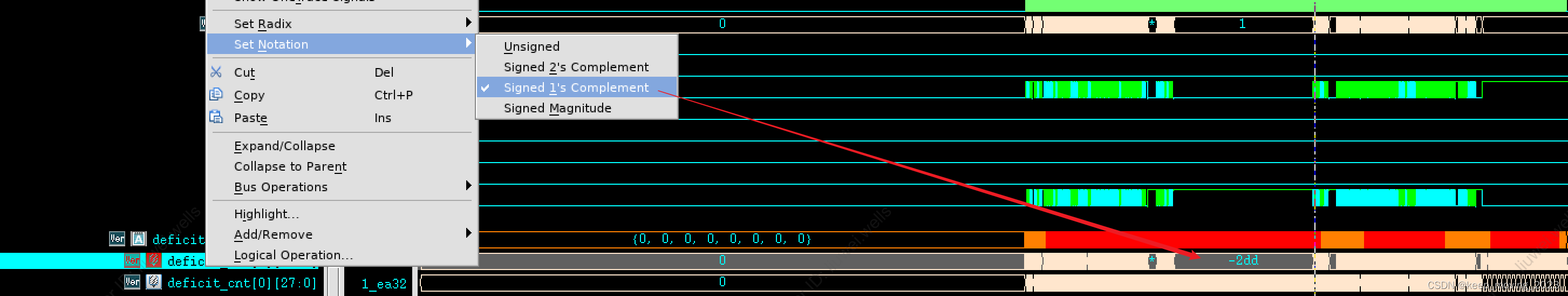

10,有些数据是有符号的,可以在波形以正负数形式显示;

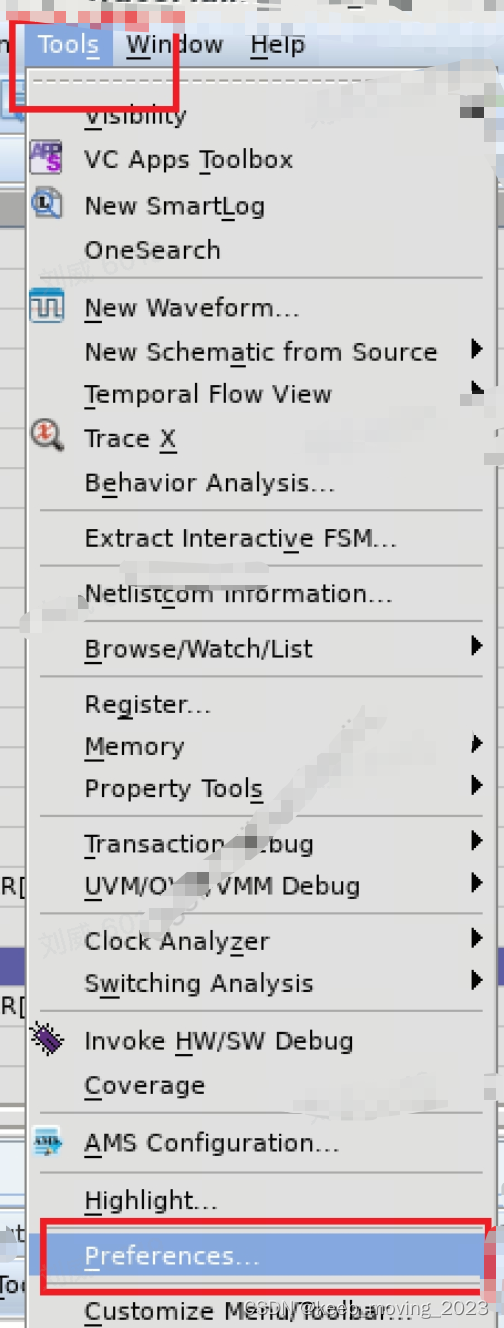

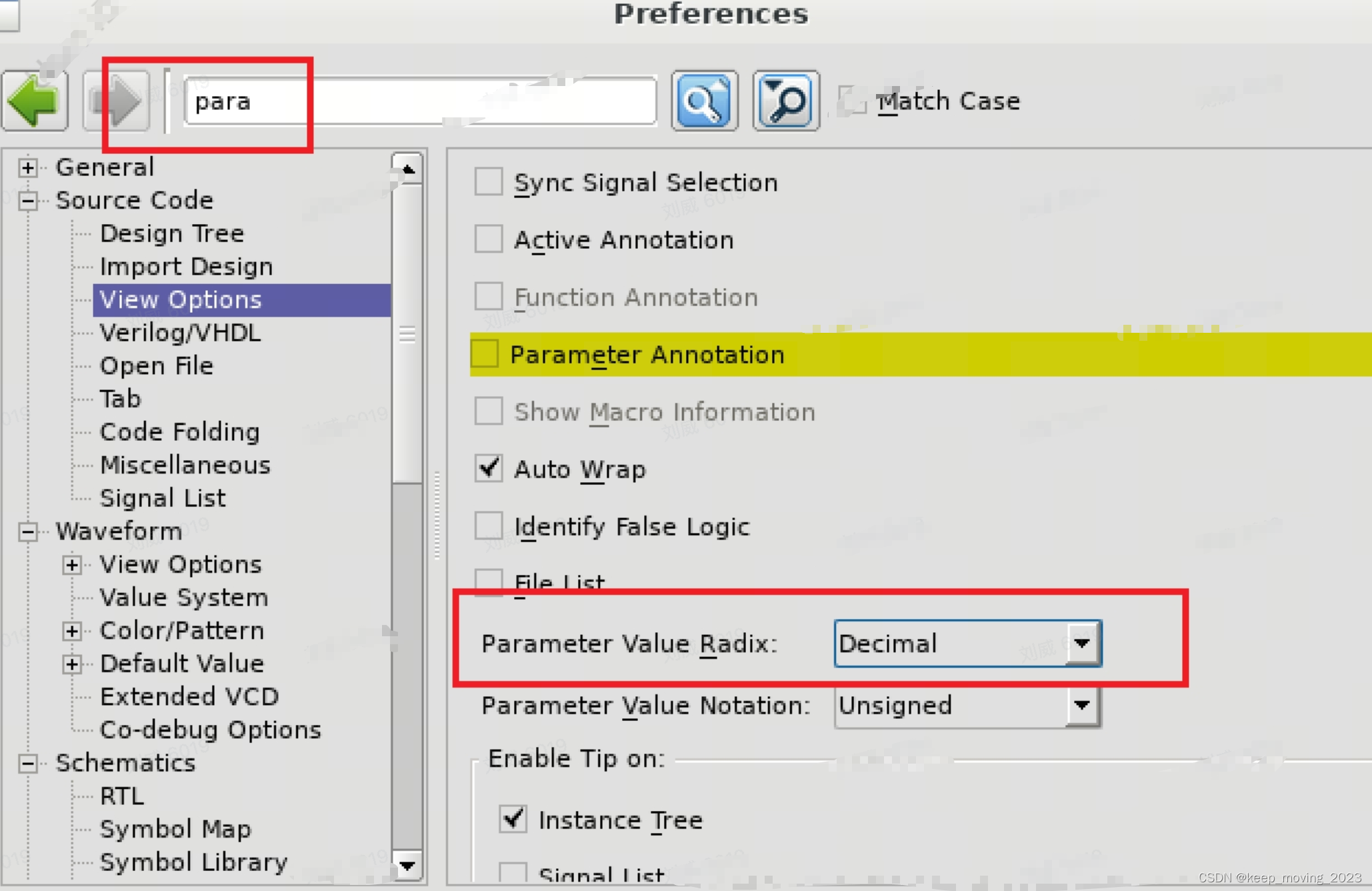

11 , 参数按指定进制显示;tool--》preferences--〉搜索:para----》选择进制 ;(也可以搜索macro,把宏按展开的形式显示;)

vcs的ucli命令:

step

ucli; 仿真时,可以输入step进行单步调试,查看执行到那行代码;debug一些组合环和环境的死循环会有不错的效果;

可以step 10;也可以run 1ns;

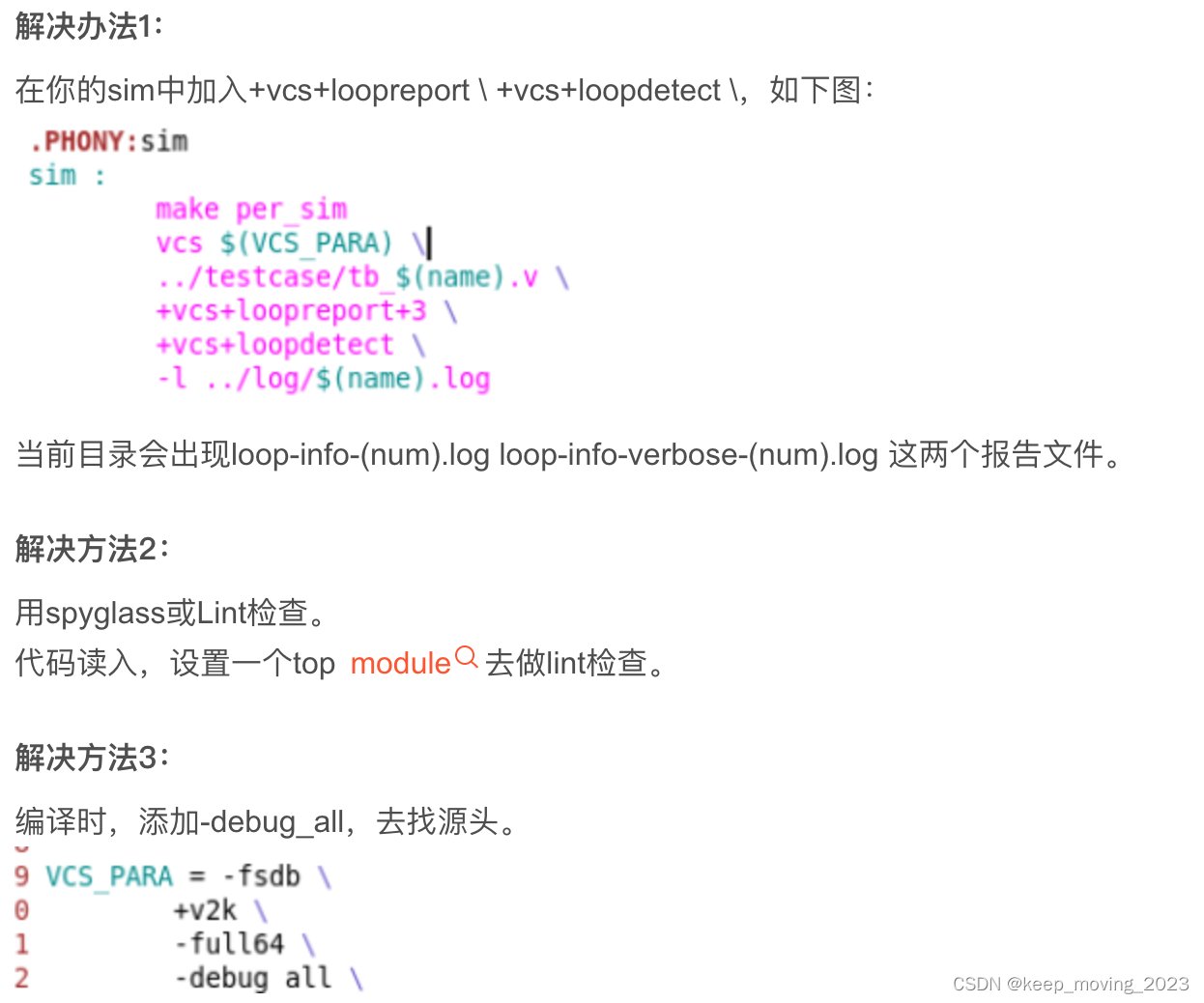

vcs好像有编译选项可以自动检测死循环:Compile/simv中加上这个option: +vcs+loopreport+number(比如1000)

看网上还有要加上loopdetect的选项,不过写了个死循环,好像也没检查出来;(后面有时间再确认一下;)

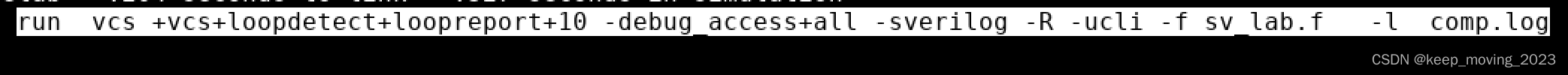

采用下面形式可以报出loop:区别就是加了两个vcs,中间有空格;

run vcs +vcs+loopdetect +vcs+loopreport+20 -debug_access+all -reportstats -sverilog -R -f sv_lab.f -l comp.log

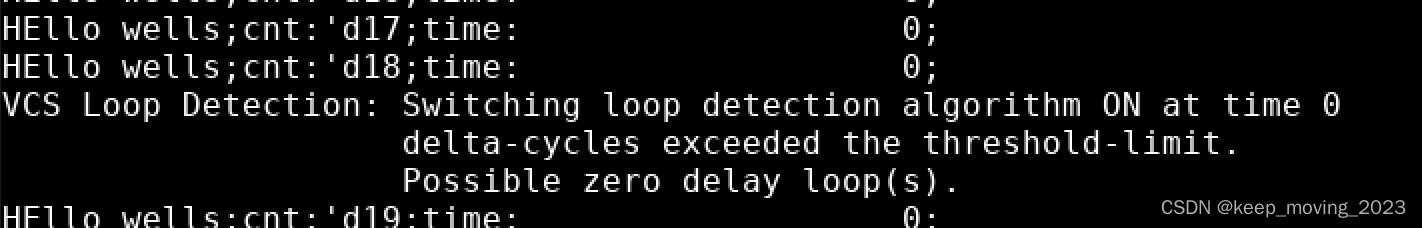

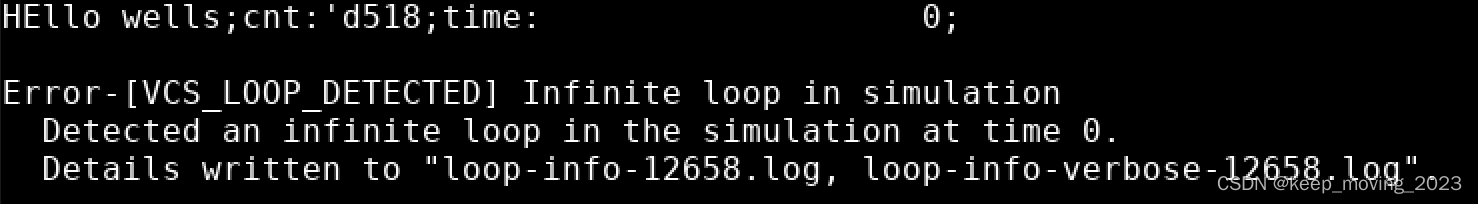

会有下面类型报错:

irun和vcs工具,检测TB环境零延时无限循环以及zero-delay组合逻辑_vcs zero delay loop-优快云博客

注意:ucli功能需要打开debug_access+all;

另外:nlint也可以检查出设计的组合环问题;

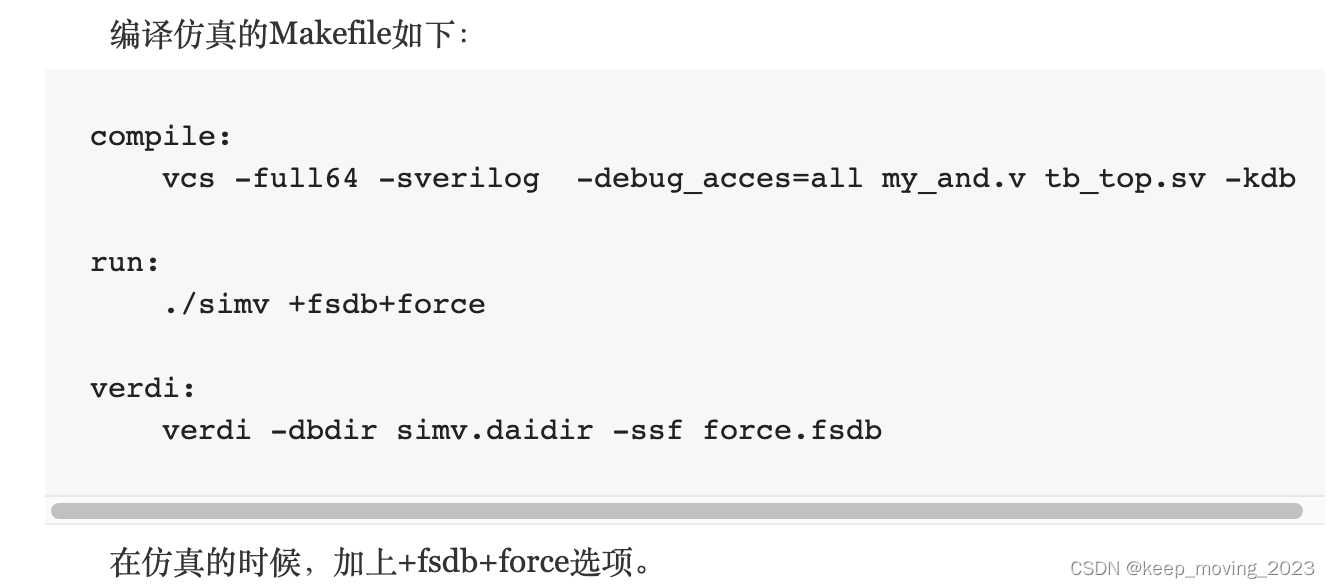

在波形上查看force信号:需要添加相关仿真选项;

1046

1046

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?